# **A71CH**

### **Plug & Trust Secure Element**

Rev. 1.2 — 27 September 2018 449312

Data sheet COMPANY PUBLIC

### 1. Introduction

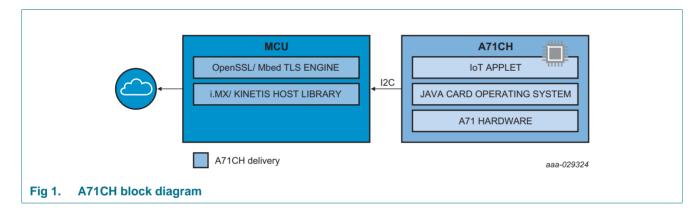

The A71CH is a ready-to-use solution providing a root of trust at the IC level and proven, chip-to-cloud security right out of the box. It is a platform capable of securely storing and provisioning credentials, securely connecting IoT devices to cloud services and performing cryptographic node authentication.

The A71CH solution provides basic security measures protecting the IC against many physical and logical attacks. It can be used with various host platforms and host operating systems to secure a broad range of applications. It is complemented by a comprehensive product support package, offering easy design-in with plug & play host application code, easy to use development kits, reference designs, and extensive documentation for product evaluation.

### 2. General description

### 2.1 A71CH naming conventions

The following table explains the naming conventions of the commercial product name of the A71CH products. Every A71CH product gets assigned such a commercial name, which includes also customer and application specific data.

The A71CH commercial names have the following format.

### A71CHxagpp(p)/mvsrrff

The 'A71CH' is a constant, all other letters are variables, which are explained in Table 1.

Table 1. A71CH commercial name format

| Variable | Meaning                                                                         | Values | Description                                                                                           |

|----------|---------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------|

| х        | IC hardware specification code                                                  | 1      | standard operational ambient temperature:<br>-25 °C to +85 °C<br>I <sup>2</sup> C interface supported |

|          |                                                                                 | 2      | standard operational ambient temperature:<br>-40 °C to +90 °C<br>I <sup>2</sup> C interface supported |

| а        | embedded operating system code                                                  | С      | Java card operating system                                                                            |

| g        | embedded application firmware (applet) code                                     | Н      | H is a fixed value = IoT security applet pre installed                                                |

| pp(p)    | package type code<br>dd(d)= Delivery Type,<br>TK2= HVSON8 (4x4),<br>UK= WLCSP12 |        |                                                                                                       |

| m        | Manufacturing Site Code                                                         | T      |                                                                                                       |

| V        | Silicon Version Code                                                            | 0      |                                                                                                       |

| S        | Silicon Version Subcode                                                         | В      |                                                                                                       |

| rr       | ROM Code ID                                                                     |        |                                                                                                       |

| ff       | FabKey ID                                                                       |        |                                                                                                       |

#### 2.2 I<sup>2</sup>C interface

The A71CH has an I<sup>2</sup>C interface in slave mode, supporting data rates up to 400 kbit/s operating in Fast-Mode (FM). The I<sup>2</sup>C interface is using the Smartcard I<sup>2</sup>C protocol as defined in Ref. 3 which is based on SMBus.

### 2.3 Security licensing

NXP Semiconductors has obtained a patent license for SPA and DPA countermeasures from Cryptography Research Incorporated (CRI). This license covers both hardware and software countermeasures. It is important to customers that countermeasures within the operation system are covered under this license agreement with CRI. Further details can be obtained on request.

### 3. Features and benefits

### 3.1 Key benefits

- Secure, zero-touch connectivity

- End-to-end security, from chip to edge to cloud

- Secure credential injection for IC-level root of trust

- Fast design-in with complete product support package

- Easy to integrate with different MCU platforms

### 3.2 Security features

The A71CH security concepts includes many security measures to protect the chip.

The A71CH operates fully autonomously based on an integrated Javacard operating system and applet. Direct memory access is possible by the fixed functionalities of the applet only. With that, the content from the memory is fully isolated from the host system.

Attack protection by integrated design measures in the chip layout, the logic and the functional blocks.

### 3.3 Cryptography features

The A71CH Secure Element provides the following functionality:

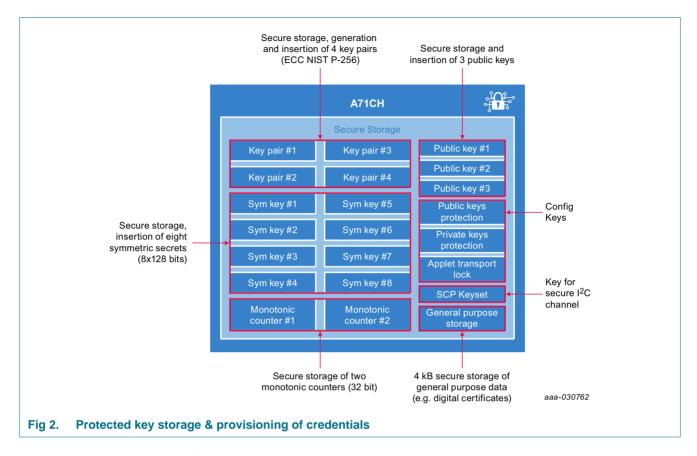

- Protected Access storage, generation, insertion or deletion of 4 key pairs (ECC NIST P-256)

- Systematic enforced authentication

- Secure key management

- Protected Access storage, insertion or deletion of 3 public keys

- Signature generation and verification (ECDSA)

- Shared secret calculation for Key Agreement (ECDH or ECDH-E)

- Protected Access storage and use of 2 monotonic counters (32 bits each)

- Protected Access storage, insertion or deletion of symmetric secrets (8x 128 bits);

longer keys can be used by using a ConstructedSecret type

- Content protected access to keys

- A unique chip ID (18 bytes)

- HKDF key derivation using the symmetric secrets as key, Extract & Expand or Expand only modes

- HMAC SHA256 calculation in one shot or sequential

- Freezing of credentials (= OTP behavior)

- Secure channel SCPO3 GP support

- (Optional) trust provisioning of key pairs, public keys, symmetric secrets, etc.

- Possibility to lock the A71CH module as transport lock mechanism

ECC keys and operations support the following ECC curve:

NIST P-256

#### **Plug & Trust Secure Element**

#### 3.4 Functional features

- Dedicated MX51 security CPU

- 400 kbit/s I<sup>2</sup>C Fast-mode interface

- -40 °C to +90 °C operational ambient temperature (A7102)

- On-chip Javacard operating system

- 40 μA typical sleep mode current with I<sup>2</sup>C pads in tristate mode

- 10 μA max deep sleep mode current with I<sup>2</sup>C pads in tristate mode

- High-performance Public Key Infrastructure (PKI)

- EEPROM with min 500,000 cycles endurance and min 25 years retention time

- HVSON8 package and small WLCSP available

### **Plug & Trust Secure Element**

### 4. Applications

### 4.1 Use Cases and target applications

- A710xCH EXAMPLE USE CASES

- Secure connection to public/private clouds, edge computing platforms, infrastructure

- Secure Amazon Web Services-compliant connectivity

- Secure commissioning

- ◆ Device-to-device authentication

- Proof of origin / anti-counterfeiting

- Key storage and data protection

- Secure provisioning of credentials

- Ecosystem protection

- A710xCH TARGET APPLICATIONS

- Connected industrial devices

- Sensor networks

- ◆ IP cameras

- Home gateways

- Home appliances

**NXP Semiconductors**

# **Ordering information**

### 5.1 Ordering options

Table 2. **Ordering information**

**5**.

| Type number 11 | Package |                                                                     |                |  |  |

|----------------|---------|---------------------------------------------------------------------|----------------|--|--|

|                | Name    | Description                                                         | Version        |  |  |

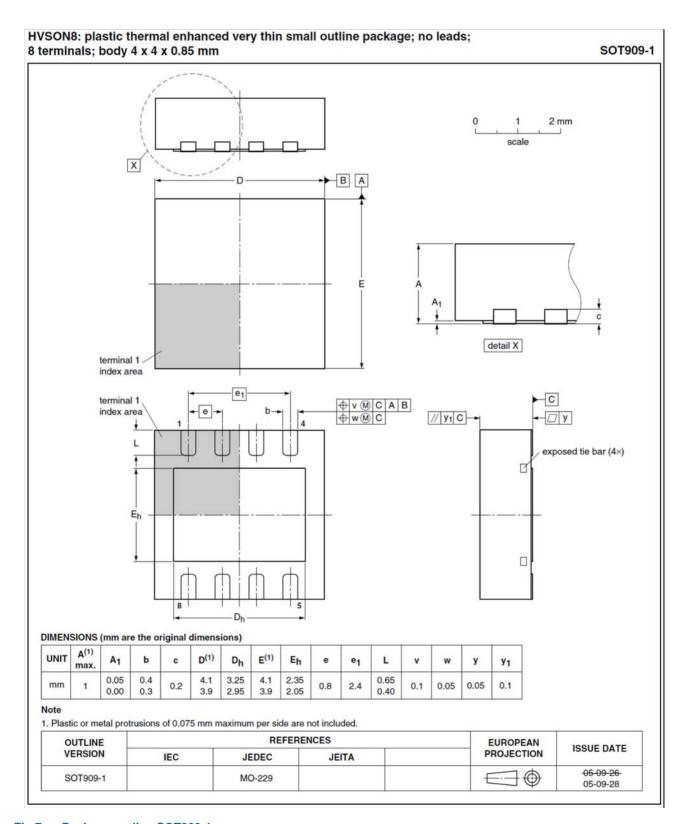

| A7101agTK2/    | HVSON-8 | plastic thermal enhanced very thin small outline package; no leads; | SOT909-1       |  |  |

| A7102agTK2/    |         | 8 terminals; body 4 × 4 × 0.85 mm                                   |                |  |  |

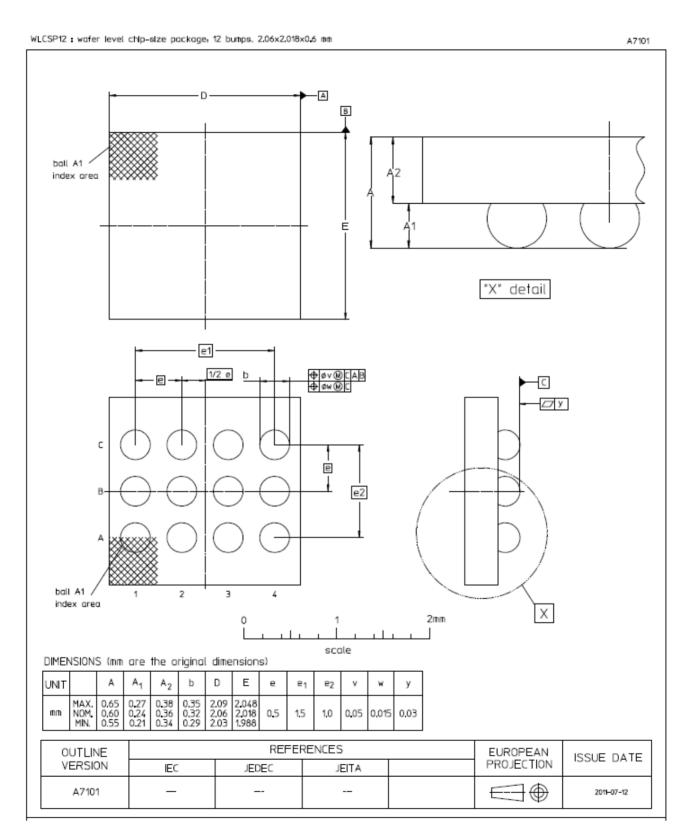

| A7101agUK/     | WLCSP12 | wafer level chip scale package, 12 bumping, 0.5 mm ball pitch       | not applicable |  |  |

| A7102agUK/     |         |                                                                     |                |  |  |

<sup>[1]</sup> a = A or C, g = G, C or A, according to the A71CH type classification see Section 2.1 "A71CH naming conventions"

#### Table 3. A71CH type table

|                   | 71                 |           |                                                                |         |                    |

|-------------------|--------------------|-----------|----------------------------------------------------------------|---------|--------------------|

| 12NC              | Type number        | Product   | Configuration                                                  | Package | Orderable part no  |

| 9353 68<br>097118 | A7101CHTK2/T0BC2V6 | A71(01)CH | customer programmable                                          | HVSON8  | A7101CHTK2/T0BC2VJ |

| 9353 635<br>15118 | A7102CHTK2/T0BC2A5 | A71(02)CH | customer programmable                                          | HVSON8  | A7102CHTK2/T0BC2AJ |

| 9353 694<br>82023 | A7101CHUK/T0BC2HA  | A71(01)CH | customer<br>programmable                                       | WLCSP   | A7101CHUK/T0BC2HAZ |

| 9353 695<br>02023 | A7102CHUK/T0BC2VA  | A71(02)CH | customer<br>programmable                                       | WLCSP   | A7102CHUK/T0BC2VAZ |

| 9353 737<br>63118 | A7101CHTK2/T0BC2BM | A71(01)CH | Provisioned &<br>Programmable<br>'Ready for IBM<br>Watson IoT' | HVSON8  | A7101CHTK2/T0BC2BJ |

| 9353 741<br>46118 | A7102CHTK2/T0BC2CH | A71(02)CH | Provisioned &<br>Programmable<br>'Ready for IBM<br>Watson IoT' | HVSON8  | A7102CHTK2/T0BC2CJ |

#### A71CH development tools type table Table 4.

| 12NC         | Type number     | Development kit | Description                        |

|--------------|-----------------|-----------------|------------------------------------|

| 935368997598 | OM3710/A71CHARD | OM3710/A71CHARD | Arduino compatible development kit |

| 935369302598 | OM3710/A71CHPCB | OM3710/A71CHPCB | Mini PCB                           |

Table 5 gives an overview of available A71CH product types.

#### Table 5. A71CH feature table

| Product type[1] | Operational ambient temperature | Interface option |

|-----------------|---------------------------------|------------------|

| A7101Cgpp(p)    | −25 °C to +85 °C                | I <sup>2</sup> C |

| A7102Cgpp(p)    | –40 °C to +90 °C                |                  |

<sup>[1]</sup> g = G, C, or A; pp(p) = UA or HN1, according the A71CH type classification see Section 2.1 "A71CH naming conventions"

### 5.1.1 Samples and final products

Section 5.1.2, gives details of how to order samples and final products.

449312

**Plug & Trust Secure Element**

### **Plug & Trust Secure Element**

### 5.1.2 Ordering A71CH samples

Samples can be ordered from NXP Semiconductors via nxp.com using the "Buy Direct" button.

Note that NXP Semiconductors can provide up to 5 pieces free of charge. Larger quantities have to be ordered separately.

### 5.2 Configuration

The A71CH is available in configurations as specified in <u>Table 3</u>. The Configuration defines the default memory and key contents. The table below describes the default configuration "customer programmable". Other configurations will be described in addenda to this data sheet.

Table 6. A71CH type table

| Credential/ State      | Amount                                    | Description                        |

|------------------------|-------------------------------------------|------------------------------------|

| Asymmetric Key Pairs   | 4 x ECDSA NIST P-256 private + public key | Not set, not locked                |

| Asymmetric Public Keys | 3 x ECDSA NIST P-256 public keys          | Not set, not locked                |

| Config Keys            | 3 x AES128                                | Not set, cannot be locked          |

| Symmetric Secret       | 8 x 128 bit key data                      | Not set, cannot be locked          |

| Monotonic Counter      | 2 x upcounting counter with 32 bit        | Counter set to 0, cannot be locked |

| SCP channel            | SCP03 keyset with 3 AES128 keys           | Keys not set, SCP03 not active     |

| GP Data                | 128 segments of 32 bytes each             | All bytes set to 0x00              |

| Plain Injection Mode   |                                           | Plain secrets can be inserted      |

| Debug Mode             |                                           | Debug Mode is active               |

| TransportLock          |                                           | Module can be set to<br>"LOCKED"   |

|                        |                                           |                                    |

#### **Plug & Trust Secure Element**

### 6. Marking

Table 7. Marking codes

| Type number | Marking code                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A710xTK2/   | Line A: 710* (* = '1' for A7101, '2' for A7102, '3' for A7103)  Line B: **** (**** = 4 digit Batch code[1])  Line C: ZnD***0 (*** = 3 digit Date code[2])  Z: diffusion center, SSMC Systems on Silicon Manufactoring (SSMC), Singapore n: assembly center  D: code to indicate conformance to RHF-2006  0: Mask version code |

[1] Batch code: 5 digits available, 2 for DBSN, 2 for ASID: mark "YY ZZ" or 4 digits available, 2 for DBSN, 2 for ASID: mark "YYZZ"

The Assembly Sequence ID (ASID) is a 2-digit indicator that counts the number of assembly batches (transport lots) within one diffusion batch id and one weekly date code. The week start and end dates are defined by the assembly center algorithm. The ASID is assigned sequentially starting with 01 and ranging through 99, then each digit ranges upper case alphabet letters in combination with numeric, then numeric in combination with upper case alphabet letters, then upper case alphabet letters in combination with upper case alphabet letters providing 1175 possible values within a week-code. The numeric zero '0' is only allowed within the sequence of 01 to 99. The alphabet letter 'O' is not allowed to avoid confusion with numeric '0'.

The Diffusion Batch Sequence Number (DBSN) is a 2-digit indicator that counts the number of diffusion batches (DBID) within one Package Type (i.e. HVSON8) and one weekly date code. The DBSN is assigned sequentially starting with 01 and ranging through 99, then each digit ranges upper case alphabet letters in combination with numeric, then numeric in combination with upper case alphabet letters, then upper case alphabet letters in combination with upper case alphabet letters providing 1175 possible values within a week-code. The numeric zero '0' is only allowed within the sequence of 01 to 99. The alphabet letter 'O' is not allowed to avoid confusion with numeric '0'.

[2] 3 digit Date code: "YWW"

"Y" is a code indicating the year in which the IC is assembled. Examples: for year 1999 is Y = 9, for year 2000 is Y = 0, for year 2001 is Y = 1. "WW" is a code indicating the week in which the IC is assembled. It is determined from the date the assembly transport lot is created or alternately the date die is issued from die stores to assembly start or the date die attach (Diebond) occurs or the date encapsulation occurs. Examples: for week 01 is WW = 01, for week 52 is WW = 52, for week 53 is WW = 53.

In the case of bumped die (WL-CSP) the code indicates the week in which the IC was bumped.

### **Plug & Trust Secure Element**

### 7. Functional description

### 7.1 Functional diagram

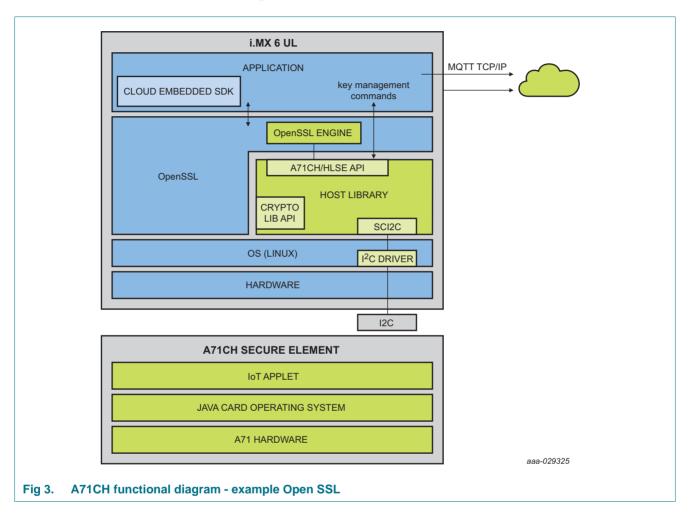

The A71CH uses I<sup>2</sup>C as communication interface as described in the following section. The A71CH commands are wrapped using the Smartcard I<sup>2</sup> protocol (SCI2C). The detailed documentation for the A71CH commands [ref to APDU Spec] and SCI2C encapsulation (Ref. 3) is available in NXP docstore."

In order to simplify the product usage a host library was created which takes care for the A71CH commands and SCI2C protocol encapsulation. The host library for various platforms is available for download with complete sources on the A71CH website.

### 7.2 Credential Storage & Memory

The I<sup>2</sup>C interface of the A71CH is supporting a Smart Card I<sup>2</sup>C (SCIIC) Protocol using an Inter-IC (I<sup>2</sup>C) based physical interface and data link layer using Fast-mode (FM) up to 400 kBit/s, a SMBus based network layer and bus protocol as well as a mapping layer to convey [ISO/IEC 7816-4] based communication. This protocol is specified in [Ref to SCI<sup>2</sup>C].

- A71CH is compliant to <u>Ref. 3</u> and implements the following SCIIC protocol options:

- Usage of the optional error detection code supported

- CDBMS MAX of 255 and a CDBSM MAX of 252

- Default Frame Waiting Time is 320 ms

- Protocol binding selection is not supported (not needed as only 7816-4 APDU mapping is supported)

- The I2C address is 90h (8-bit address) equals 48h (7-bit address) and optional 92h (8-bit address) which equals 49h (7-bit address)

#### 7.3 I<sup>2</sup>C Interface

The A71CH has an  $I^2C$  interface in slave mode, supporting data rates up to 400 kbit/s operating in Fast-Mode (FM). The  $I^2C$  interface is using the Smartcard  $I^2C$  protocol as defined in Ref. 3 which is based on SMBus. The default  $I^2C$  address after power-on-reset depends on the bootup condition as shown in Table 8.

#### 7.4 Automatic Communication Mode detection at Power on

The IC configures its interface according to the pin state as shown in the table below. The host system must keep the voltage levels stable at these pins for at least 500  $\mu$ s after power-on-reset.

Table 8. I<sup>2</sup>C address

| Value at startup |     |         |         | I <sup>2</sup> C address |      |  |

|------------------|-----|---------|---------|--------------------------|------|--|

| IF0              | IF1 | I2C_SCL | I2C_SDA | Write                    | Read |  |

| 0                | Х   | 0       | 0       | n.a.                     | n.a. |  |

| 1                | 0   | 1       | 1       | 0x90                     | 0x91 |  |

| 1                | 1   | 1       | 1       | 0x92                     | 0x93 |  |

### 7.5 Power-saving modes

The device provides two power-saving operation modes, the SLEEP mode and the DEEP SLEEP mode. These modes are activated via pad RST\_N (DEEP SLEEP mode) or by the device.

#### 7.5.1 SLEEP mode

The SLEEP mode has the following properties:

- all internal clocks are frozen,

- CPU enters power saving mode with program execution being stopped,

- · CPU registers keep their contents,

- RAM keeps its contents,

#### **Plug & Trust Secure Element**

The A71CH enters automatically into SLEEP mode after 312 ms of inactivity on the I<sup>2</sup>C lines and also wakes up automatically from SLEEP mode. In SLEEP mode, all internal clocks are stopped. The IOs hold the logical states they had at the time IDLE was activated. During SLEEP mode security sensors HVS, LVS, LTS, HTS, Light Sensors, Glitch Sensors and Active Shielding are disabled.

There are two ways to exit from the SLEEP mode:

- A reset signal on RST N

- An External Interrupt edge triggered by a falling edge on I2C SDA

#### 7.5.2 DEEP SLEEP mode

The A71CHx provides a special sleep mode offering maximum power saving. It is reached by pulling RST\_N to a logic zero level for more than  $500 \, \mu s$ .

While in deep sleep mode the internal power is completely switched off and only the IO pads stay supplied. All digital pads will stay in high-Z mode.

To leave the DEEP SLEEP mode RST\_N has to be released and set to a logic "1" level.

**Plug & Trust Secure Element**

### 8. Pinning information

### 8.1 Pinning

### 8.1.1 Pinning HVSON8

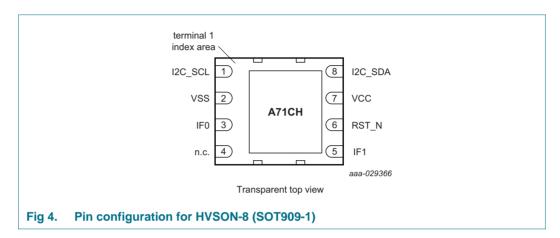

Table 9. Pin description HVSON8

| Symbol  | Pin | Description                                 |

|---------|-----|---------------------------------------------|

| I2C_SCL | 1   | I <sup>2</sup> C clock                      |

| VSS     | 2   | ground                                      |

| IF0     | 3   | interface activation, apply high on startup |

| n.c.    | 4   | not connected                               |

| IF1     | 5   | I <sup>2</sup> C address selection          |

| RST_N   | 6   | reset input, active LOW                     |

| VCC     | 7   | power supply voltage input                  |

| I2C_SDA | 8   | I <sup>2</sup> C data                       |

The center pad of the IC is not connected, although it is recommended to connect it to ground for thermal reasons.

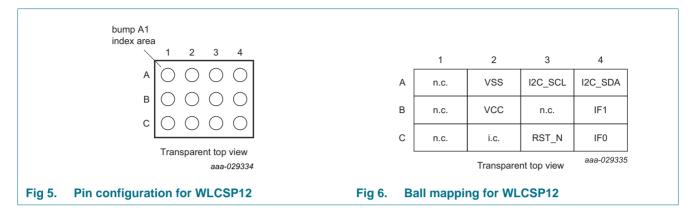

### 8.1.2 Pinning WLCSP

Table 10. Pin description WLCSP

| Symbol  | Pin | Description                                 |

|---------|-----|---------------------------------------------|

| n.c.    | A1  | not connected                               |

| VSS     | A2  | ground                                      |

| I2C_SCL | А3  | I <sup>2</sup> C Clock                      |

| I2C_SDA | A4  | I <sup>2</sup> C Data                       |

| n.c.    | B1  | not connected                               |

| VCC     | B2  | Power supply voltage input                  |

| n.c.    | В3  | not connected                               |

| IF1     | B4  | I <sup>2</sup> C address selection          |

| n.c.    | C1  | not connected                               |

| i.c.    | C2  | internally connected; connect to ground     |

| RST_N   | C3  | Reset input, active LOW                     |

| IF0     | C4  | interface activation, apply high on startup |

The pins/balls A1, B1, C1, and B3 are not connected internally. These pins/balls can be used for routing to connect to B2 (VCC) in order to have an easier PCB layout.

### **Plug & Trust Secure Element**

### 9. Package outline

Fig 7. Package outline SOT909-1

Fig 8. Package outline WLCSP12

### 10. Packing information

### 10.1 Reel packing

The A71CH product is available on 7" tape on reel and 13" tape on reel. Details are provided in Table 11.

Table 11. Reel packing options

| Package type | Reel type                       | Minimum packing quantity |

|--------------|---------------------------------|--------------------------|

| HVSON8       | 7" tape on reel                 | 1500                     |

| HVSON8       | 13" tape on reel <sup>[1]</sup> | 6000                     |

| WLCSP12      | 7" tape on reel                 | 3000                     |

<sup>[1]</sup> For details about packing method, product orientation, tape dimensions and labeling for A71 parts in HVSON8 package having an ordering code (12NC) ending 118 refer to Ref. 2.

### 11. Electrical and timing characteristics

The electrical interface characteristics of static (DC) and dynamic (AC) parameters for pads and functions used for I<sup>2</sup>C are in accordance with the NXP I<sup>2</sup>C specification (see Ref. 1).

### 12. Limiting values

Table 12. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS (ground = 0 V).

| Symbol               | Parameter                                                   | Conditions                                   |     | Min  | Max   | Unit |

|----------------------|-------------------------------------------------------------|----------------------------------------------|-----|------|-------|------|

| $V_{DD}$             | supply voltage                                              |                                              |     | -0.3 | +4.6  | V    |

| VI                   | input voltage                                               | any signal pad                               |     | -0.3 | +4.6  | V    |

| I <sub>I</sub>       | input current                                               | pad I2C_SDA,<br>I2C_SCL                      |     | -    | 10    | mA   |

| I <sub>O</sub>       | output current                                              | pad I2C_SDA,<br>I2C_SCL                      |     | -    | 10    | mA   |

| I <sub>lu</sub>      | latch-up current                                            | $V_I < 0 \text{ V or } V_I > V_{DD}$         |     | -    | 100   | mA   |

| V <sub>esd_hbm</sub> | electrostatic discharge<br>voltage (Human Body<br>Model)    | pads VCC, VSS,<br>RST_N, I2C_SDA,<br>I2C_SCL | [1] |      | ± 2.0 | kV   |

| V <sub>esd_cdm</sub> | electrostatic discharge<br>voltage (Charge Device<br>Model) | pads VCC, VSS,<br>RST_N, I2C_SDA,<br>I2C_SCL | [3] |      | ± 500 | V    |

| P <sub>tot</sub>     | Total power dissipation                                     |                                              | [2] | -    | 1     | W    |

| T <sub>stg</sub>     | Storage temperature                                         |                                              |     | -55  | +125  | °C   |

<sup>[1]</sup> MIL Standard 883-D method 3015; human body model; C = 100 pF, R = 1.5 k $\Omega$ ;  $T_{amb} = -25$  °C to +85 °C.

<sup>[2]</sup> Depending on appropriate thermal resistance of the package.

<sup>[3]</sup> JESD22-C101, JEDEC Standard Field induced charge device model test method.

### **Plug & Trust Secure Element**

### 13. Recommended operating conditions

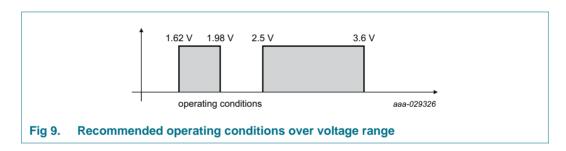

The A71CH offers two operation modes, the so-called 1V8 mode and the 3V3 mode targeted for battery supplied applications.

Table 13. Recommended operating conditions

| Symbol           | Parameter                                             | Conditions                                   | Min  | Тур | Max  | Unit |

|------------------|-------------------------------------------------------|----------------------------------------------|------|-----|------|------|

| $V_{DD}$         | supply voltage range                                  | 3V3 mode range<br>CPU in free<br>runing mode | 2.50 | 3.3 | 3.6  | V    |

|                  |                                                       | 1V8 mode                                     | 1.62 | 1.8 | 1.98 | V    |

| VI               | DC input voltage on digital I/O pads I2C_SCL, I2C_SDA | 3V3 mode                                     | 0    |     | 3.6  | V    |

|                  |                                                       | 1V8 mode                                     | 0    |     | 3.6  | V    |

| VI               | DC input voltage on digital input pad RST_N           | 3V3 mode                                     | 0    |     | 3.6  | V    |

|                  |                                                       | 1V8 mode                                     | 0    |     | 3.6  | V    |

| T <sub>amb</sub> | Operating ambient temperature                         | A7101                                        | -25  |     | +85  | °C   |

|                  |                                                       | A7102                                        | -40  |     | +90  | °C   |

### **Plug & Trust Secure Element**

### 14. Characteristics

### 14.1 DC characteristics

#### **Measurement conventions**

Testing measurements are performed at the contact pads of the device under test. All voltages are defined with respect to the ground contact pad VSS. All currents flowing into the device are considered positive.

#### 14.1.1 General and I<sup>2</sup>C I/O interface

Table 14. Electrical DC characteristics of I2C SCL, I2C SDA and RST N

| Symbol                                                | Parameter                                                                                                                                                                    | Conditions                                                                                                                                                |     | Min                         | Тур                 | Max                                                    | Unit               |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------|---------------------|--------------------------------------------------------|--------------------|

| _                                                     |                                                                                                                                                                              |                                                                                                                                                           |     | IAIIII                      | тур                 | IVIAX                                                  | Oili               |

|                                                       | put: I2C_SCL, I2C_SDA in push-p                                                                                                                                              | ouii moae                                                                                                                                                 |     |                             |                     | [41                                                    |                    |

| V <sub>IH</sub>                                       | HIGH level input voltage                                                                                                                                                     |                                                                                                                                                           |     | $0.7 V_{DD}$                |                     | V <sub>Imax</sub> [1]                                  | V                  |

| V <sub>IL</sub>                                       | LOW level input voltage                                                                                                                                                      |                                                                                                                                                           |     | -0.5                        |                     | 0.3 V <sub>DD</sub>                                    | V                  |

| I <sub>IH</sub>                                       | HIGH level input current in input mode                                                                                                                                       | $V_{IHmin} < V_{I} < V_{IHmax}$                                                                                                                           |     |                             |                     | ± 10                                                   | μΑ                 |

| I <sub>IL</sub>                                       | LOW level input current                                                                                                                                                      | $V_{ILmin} < V_{I} < V_{ILmax}$                                                                                                                           |     |                             |                     | ± 10                                                   | μΑ                 |

| V <sub>OH</sub>                                       | HIGH level output voltage                                                                                                                                                    | $I_{OH} = -3.0 \text{ mA};$<br>3V3 mode                                                                                                                   | [2] | 0.7 V <sub>DD</sub>         |                     |                                                        | V                  |

|                                                       |                                                                                                                                                                              | $I_{OH} = -3.0 \text{ mA};$<br>1V8 mode                                                                                                                   | [2] | 0.7 V <sub>DD</sub>         |                     |                                                        | V                  |

| V <sub>OL</sub>                                       | OL LOW level output voltage                                                                                                                                                  | $I_{OL} = 3.0 \text{ mA}$<br>3V3 mode                                                                                                                     |     |                             |                     | 0.4                                                    | V                  |

|                                                       | I <sub>OL</sub> = 2.0 mA<br>1V8 mode                                                                                                                                         |                                                                                                                                                           |     |                             | 0.2 V <sub>DD</sub> | V                                                      |                    |

|                                                       | . 100 001 100 004 1                                                                                                                                                          |                                                                                                                                                           |     |                             |                     |                                                        |                    |

|                                                       | put: I2C_SCL, I2C_SDA in open-o                                                                                                                                              | Irain mode                                                                                                                                                |     | 0.7.1/                      |                     | V [1]                                                  | \/                 |

| $V_{IH}$                                              | HIGH level input voltage                                                                                                                                                     | Irain mode                                                                                                                                                |     | 0.7 V <sub>DD</sub>         |                     | V <sub>Imax</sub> [1]                                  | V                  |

| V <sub>IH</sub><br>V <sub>IL</sub>                    | HIGH level input voltage  LOW level input voltage                                                                                                                            |                                                                                                                                                           |     | 0.7 V <sub>DD</sub><br>-0.5 |                     | 0.3 V <sub>DD</sub>                                    | V                  |

| V <sub>IH</sub><br>V <sub>IL</sub>                    | HIGH level input voltage                                                                                                                                                     | V <sub>IHmin</sub> < V <sub>I</sub> < V <sub>IHmax</sub>                                                                                                  |     |                             |                     |                                                        |                    |

|                                                       | HIGH level input voltage  LOW level input voltage  HIGH level input current in input                                                                                         |                                                                                                                                                           |     |                             |                     | 0.3 V <sub>DD</sub>                                    | V                  |

| V <sub>IH</sub><br>V <sub>IL</sub>                    | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode                                                                                    | $V_{IHmin} < V_I < V_{IHmax}$                                                                                                                             |     |                             |                     | 0.3 V <sub>DD</sub><br>± 10                            | V<br>µA            |

| V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub> | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode  LOW level input current                                                           | $V_{IHmin} < V_I < V_{IHmax}$ $V_{ILmin} < V_I < V_{ILmax}$ $I_{OL} = 3.0 \text{ mA}$                                                                     |     |                             |                     | 0.3 V <sub>DD</sub><br>± 10<br>± 10                    | V<br>μΑ<br>μΑ      |

| VIH<br>VIL<br>IIH<br>IIL                              | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode  LOW level input current  LOW level output voltage                                 | $V_{IHmin} < V_I < V_{IHmax}$ $V_{ILmin} < V_I < V_{ILmax}$ $I_{OL} = 3.0 \text{ mA}$ $3V3 \text{ mode}$ $I_{OL} = 2.0 \text{ mA}$                        |     |                             |                     | 0.3 V <sub>DD</sub><br>± 10<br>± 10<br>0.4             | V<br>μΑ<br>μΑ<br>V |

| V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub> | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode  LOW level input current  LOW level output voltage                                 | $V_{IHmin} < V_I < V_{IHmax}$ $V_{ILmin} < V_I < V_{ILmax}$ $I_{OL} = 3.0 \text{ mA}$ $3V3 \text{ mode}$ $I_{OL} = 2.0 \text{ mA}$                        |     |                             |                     | 0.3 V <sub>DD</sub><br>± 10<br>± 10<br>0.4             | V<br>μΑ<br>μΑ<br>V |

| VIH VIL IIH VOL                                       | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode  LOW level input current  LOW level output voltage                                 | $V_{IHmin} < V_I < V_{IHmax}$ $V_{ILmin} < V_I < V_{ILmax}$ $I_{OL} = 3.0 \text{ mA}$ $3V3 \text{ mode}$ $I_{OL} = 2.0 \text{ mA}$                        |     | -0.5                        |                     | 0.3 V <sub>DD</sub><br>± 10<br>± 10<br>0.4             | V<br>μA<br>μA<br>V |

| V <sub>IH</sub> V <sub>IL</sub> IIH V <sub>OL</sub>   | HIGH level input voltage  LOW level input voltage  HIGH level input current in input mode  LOW level input current  LOW level output voltage  ST_N  HIGH level input voltage | $V_{IHmin} < V_{I} < V_{IHmax}$ $V_{ILmin} < V_{I} < V_{ILmax}$ $I_{OL} = 3.0 \text{ mA}$ $3V3 \text{ mode}$ $I_{OL} = 2.0 \text{ mA}$ $1V8 \text{ mode}$ | 3   | -0.5                        |                     | 0.3 V <sub>DD</sub> ± 10 ± 10 0.4  0.2 V <sub>DD</sub> | V<br>μA<br>μA<br>V |

<sup>[1]</sup> Maximum value according to Table 13 "Recommended operating conditions"

### **Plug & Trust Secure Element**

- [2] : External pull-up resistor 20 k $\Omega$  to VDD. The worst case test condition for parameter V<sub>OH</sub> is present at minimum V<sub>DD</sub>. For class A supply voltage conditions V<sub>DD</sub> = 4.5 V is the worst case with respect to the fix specification limit V<sub>OHmin</sub> = 3.8 V (0.844 V<sub>DD</sub>). The supply voltage related limit "0.7 V<sub>DD</sub>" is a stricter requirement than the fix value 3.8 V at high V<sub>DD</sub> (0.7 V<sub>DD</sub> = 3.85 V at V<sub>DD</sub> = 5.5 V). So, in the V<sub>DD</sub> range 4.5 V to 5.5 V, V<sub>OHmin</sub> is specified as "the larger value of 0.7 V<sub>DD</sub> and 3.8 V, respectively".

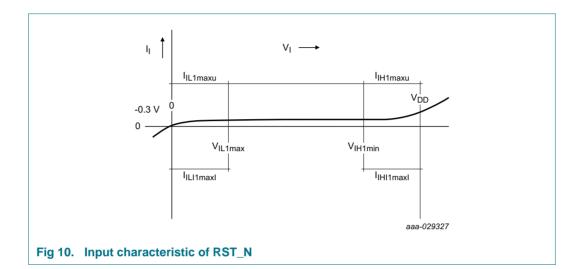

- [3] The active low RST\_N input internally has a resistive pull-down device to VSS. Accordingly a current is flowing into the pad voltages above 0 V. Figure 10 shows the RST\_N input characteristic.

### **Plug & Trust Secure Element**

### 14.1.2 I<sup>2</sup>C interface at 3V3 mode operation[1]

Table 15. Electrical characteristics of IC supply voltage  $V_{DD}$ ;  $V_{SS} = 0$  V;  $T_{amb} = -40$  to +90 °C

| Symbol                | Parameter                      | Conditions                                    | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------|-----------------------------------------------|------|------|------|------|

| Supply                |                                |                                               | '    |      | '    |      |

| $V_{DD}$              | supply voltage range           | 3V3 mode range<br>CPU in free running mode    | 2.50 | 3.3  | 3.6  | V    |

| I <sub>DD</sub>       | no coprocessor active          | CPU in free running mode                      |      | 6.3  | 7.0  | mA   |

|                       | EPROM programming in progress  | CPU in free running mode                      |      | 7.3  | 8.0  | mA   |

|                       | AES coprocessor active         | CPU in free running mode                      |      | 9.3  | 10.3 | mA   |

|                       | ECC coprocessor active         | CPU in free running mode                      |      | 13.7 | 15.1 | mA   |

| I <sub>DD(SLP)</sub>  | supply current SLEEP mode      | T <sub>amb</sub> = 25 °C                      |      | 45   | 150  | μΑ   |

| I <sub>DD(DSLP)</sub> | supply current deep sleep mode | RST_N at 0V, $T_{amb} = 25  ^{\circ}\text{C}$ |      |      | 10   | μΑ   |

|                       |                                | RST_N at 0V, $T_{amb} = 90  ^{\circ}\text{C}$ |      |      | 10   | μΑ   |

<sup>[1]</sup> All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

### 14.1.3 I<sup>2</sup>C interface at 1V8 mode operation[1]

Table 16. Electrical characteristics of IC supply voltage  $V_{DD}$ ;  $V_{SS} = 0$  V;  $T_{amb} = -40$  to +90 °C

| Symbol                | Parameter                      | Conditions                                    | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------|-----------------------------------------------|------|------|------|------|

| Supply                |                                |                                               | '    | '    | '    | '    |

| $V_{DD}$              | supply voltage range           | 1V8 mode range                                | 1.62 | 1.8  | 1.98 | V    |

| I <sub>DD</sub>       | no coprocessor active          | CPU in free running mode                      |      | 2.45 |      | mA   |

|                       | AES coprocessor active         | CPU in free running mode                      |      | 2.7  |      | mA   |

|                       | ECC coprocessor active         | CPU in free running mode                      |      | 7.5  |      | mA   |

| I <sub>DD(SLP)</sub>  | supply current SLEEP mode      | T <sub>amb</sub> = 25 °C                      |      | 40   | 80   | μΑ   |

| I <sub>DD(DSLP)</sub> | supply current deep sleep mode | RST_N at 0V, $T_{amb} = 25  ^{\circ}\text{C}$ |      |      | 10   | μΑ   |

|                       |                                | RST_N at 0V, $T_{amb} = 90  ^{\circ}\text{C}$ |      |      | 10   | μΑ   |

<sup>[1]</sup> All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

### 14.2 AC characteristics

Table 17. Non-volatile memory timing characteristics;  $V_{DD}$  = 1.8 V  $\pm$  10% or 3 V  $\pm$  10% V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to 90 °C

| Symbol           | Parameter                                       | Conditions                | Min                 | Тур | Max | Unit   |

|------------------|-------------------------------------------------|---------------------------|---------------------|-----|-----|--------|

| $t_{EEP}$        | EEPROM erase + program time                     |                           |                     | 2.7 |     | ms     |

| t <sub>EEE</sub> | EEPROM erase time                               |                           |                     | 1.7 |     | ms     |

| $t_{\sf EEW}$    | EEPROM program time                             |                           |                     | 1.0 |     | ms     |

| t <sub>EER</sub> | EEPROM data retention time                      | T <sub>amb</sub> = +55 °C | 25                  |     |     | years  |

| N <sub>EEC</sub> | EEPROM endurance (number of programming cycles) |                           | 5 × 10 <sup>5</sup> |     |     | cycles |

Table 18. Electrical AC characteristics of I2C\_SDA, I2C\_SCL, and RST\_N $^{[1]}$ ; V<sub>DD</sub> = 1.8 V  $\pm$  10% or 3 V  $\pm$  10% V; V<sub>SS</sub> = 0 V; T<sub>amb</sub> = -40 to 90 °C

| Symbol             | Parameter                                                                      | Conditions                                                                      |            | Min | Тур | Max | Unit |

|--------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| Input/O            | utput: I2C_SDA, I2C_SCL in op                                                  | en-drain mode                                                                   |            |     | '   | '   |      |

| tr <sub>IO</sub>   | I/O Input rise time                                                            | Input/reception mode                                                            | <u>[4]</u> |     |     | 1   | μs   |

| tf <sub>IO</sub>   | I/O Input fall time                                                            | Input/reception mode                                                            | [4]        |     |     | 1   | μs   |

| tf <sub>OIO</sub>  | I/O Output fall time                                                           | Output/transmission mode; $C_L = 30 \text{ pF}$                                 | <u>[4]</u> |     |     | 0.3 | μs   |

| f <sub>CLK</sub>   | External clock frequency in I <sup>2</sup> C applications                      | $t_{\text{CLKW}}$ , $T_{\text{amb}}$ and $V_{\text{DD}}$ in their spec'd limits |            | -   |     | 400 | kHz  |

| t <sub>CLKW</sub>  | Clock pulse width i.r.t. clock<br>period (positive pulse duty<br>cycle of CLK) |                                                                                 | [3]        | 40  |     | 60  | %    |

| Inputs:            | RST_N                                                                          |                                                                                 | _          | '   |     | '   |      |

| t <sub>RW</sub>    | Reset pulse width (RST_N low) without entering deep sleep mode                 |                                                                                 |            | 40  |     | 400 | μs   |

| t <sub>RDSLP</sub> | Reset pulse width (RST_N low) to enter deep sleep mode                         |                                                                                 |            | 500 |     |     | μs   |

| t <sub>WKP</sub>   | Wake-up time from SLEEP mode                                                   | $f_{CLKmin} < f_{CLK} < f_{CLKmax}$                                             |            | -   | 8   | 10  | μs   |

449312

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

**Plug & Trust Secure Element**

Table 18. Electrical AC characteristics of I2C\_SDA, I2C\_SCL, and RST\_N $^{[1]}$ ; V<sub>DD</sub> = 1.8 V  $\pm$  10% or 3 V  $\pm$  10% V; V<sub>SS</sub> = 0 V; T<sub>amb</sub> = -40 to 90 °C

| Symbol              | Parameter                                                 | Conditions                                          | Min | Тур | Max | Unit |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

|                     | Pad LOW time for wake-up                                  | level triggered ext.int.                            | -   | 8   | 10  | μs   |

|                     | from SLEEP mode                                           | edge triggered ext.int.                             | -   | 8   | 10  | μs   |

| t <sub>WKPRST</sub> | RST_N LOW time for wake-up from SLEEP mode                |                                                     | 40  |     | -   | μs   |

| t <sub>WKWT</sub>   | Time from SLEEP mode<br>wake/up event to I2C_SDA<br>valid |                                                     |     | 50  | 100 | ns   |

| C <sub>PIN</sub>    | Pin capacitances RST_N, I2C_SDA, /I2C_SCL                 | Test frequency = 1 MHz;<br>T <sub>amb</sub> = 25 °C | -   |     | 10  | pF   |

- [1] All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

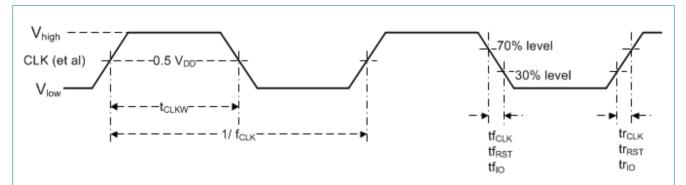

- [2]  $t_r$  is defined as rise time between 20% and 80% of the signal amplitude.  $t_f$  is defined as fall time between 80% and 20% of the signal amplitude.

- [3] During AC testing the inputs RST\_N, I2C\_SDA, I2C\_SCL are driven at 0 V to +0.3 V for a LOW input level and at V<sub>DD</sub> -0.3 V to V<sub>DD</sub> for a HIGH input level. Clock period and signal pulse (duty cycle) timing is measured at 50% of V<sub>DD</sub>.

- [4]  $t_r$  is defined as rise time between 30% and 70% of the signal amplitude.  $t_f$  is defined as fall time between 70% and 30% of the signal amplitude.

Fig 11. External clock drive and AC test timing reference points of I2C\_SDA, I2C\_SCL, and RST\_N (see <u>Table note [3]</u> and <u>Table note [4]</u>) in open drain mode

#### **14.3 EMC/EMI**

EMC and EMI resistance according to IEC 61967-4.

### Plug & Trust Secure Element

### 15. Abbreviations

Table 19. Abbreviations

| 14510 101 715511 |                                                     |

|------------------|-----------------------------------------------------|

| Acronym          | Description                                         |

| AES              | Advanced Encryption Standard                        |

| CRC              | Cyclic Redundancy Check                             |

| DES              | Digital Encryption Standard                         |

| DPA              | Differential Power Analysis                         |

| DSS              | Digital Signature Standard                          |

| ECC              | Elliptic Curve Cryptography                         |

| EEPROM           | Electrically Erasable Programmable Read-Only Memory |

| I/O              | Input/Output                                        |

| MAC              | Message Authentication Code                         |

| os               | Operating System                                    |

| PKI              | Public Key Infrastructure                           |

| SFI              | Single Fault Injection                              |

| SHA              | Secure Hash Algorithm                               |

|                  |                                                     |

### **Plug & Trust Secure Element**

### 16. References

- I<sup>2</sup>C-bus specification and user manual, Rev. 3.0 June-19-2007, NXP Semiconductors

- [2] SOT909-1; HVSON8; Reel pack; Ordering code (12NC) ending 118; Packing Information; Rev. 2 19 April 2013

- [3] Application note SCIIC Protocol Specification, Application note, Rev 1.x, AN12207 (document number an19501x)

NXP Semiconductors

A71CH

Plug & Trust Secure Element

## 17. Revision history

#### Table 20. Revision history

| Document ID    | Release date                                                        | Data sheet status                                                   | Change notice  | Supersedes |  |  |  |

|----------------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------------|------------|--|--|--|

| 449312         | 20180927                                                            | Data sheet                                                          |                | 449311     |  |  |  |

| Modifications: | • Table 1 "A71                                                      | CH commercial name format                                           | ": Added WLCSP |            |  |  |  |

|                | • <u>Table 3 "A71</u>                                               | CH type table": Updated                                             |                |            |  |  |  |

|                | <ul> <li>Section 3.4 "</li> </ul>                                   | Functional features": Added \                                       | NLCSP          |            |  |  |  |

|                | <ul> <li>Section 8.1.1 "Pinning HVSON8": Added paragraph</li> </ul> |                                                                     |                |            |  |  |  |

|                | <ul> <li>Section 8.1.2 "Pinning WLCSP": Added section</li> </ul>    |                                                                     |                |            |  |  |  |

|                | • Figure 5 "Pin                                                     | • Figure 5 "Pin configuration for WLCSP12": Added pin configuration |                |            |  |  |  |

|                | <ul> <li>Figure 6 "Bal</li> </ul>                                   | • Figure 6 "Ball mapping for WLCSP12": Updated                      |                |            |  |  |  |

|                | Table 10 "Pin description WLCSP": Updated                           |                                                                     |                |            |  |  |  |

|                | • <u>Table 11 "Re</u>                                               | el packing options": Added W                                        | /LCSP          |            |  |  |  |

| 449311         | 20180801                                                            | Data sheet                                                          |                | 449310     |  |  |  |

| 449310         | 20180221                                                            | Objective short data she                                            | et             |            |  |  |  |

| Modifications: | <ul> <li>Initial version</li> </ul>                                 | 1                                                                   |                |            |  |  |  |

#### **Plug & Trust Secure Element**

### 18. Legal information

#### 18.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 18.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 18.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

449312

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

#### **Plug & Trust Secure Element**

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 18.4 Licenses

#### ICs with DPA Countermeasures functionality

NXP ICs containing functionality implementing countermeasures to Differential Power Analysis and Simple Power Analysis are produced and sold under applicable license from Cryptography Research, Inc.

#### 18.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

FabKey — is a trademark of NXP B.V.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

### 19. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### **Plug & Trust Secure Element**

I2C\_SDA and RST\_N ......18

### 20. Tables

| A71CH feature table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6. Electrical characteristics of IC supply voltage $V_{DD}$ ; $V_{SS} = 0 \text{ V}$ ; $T_{amb} = -40 \text{ to } +90 \text{ °C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|