Datasheet, Version 2.1, August 30, 2011

# CoolSET<sup>®</sup> - Q1

# **ICE2QR1765Z**

# Off-Line SMPS Quasi-Resonant PWM Controller with integrated 650V CoolMOS<sup>®</sup> and startup cell in DIP-7

Power Management & Supply

Never stop thinking.

| CoolSET <sup>®</sup> - Q1<br>ICE2QR1765Z<br>Revision History: | August 30, 2011                              | Datasheet |

|---------------------------------------------------------------|----------------------------------------------|-----------|

| Previous Version:                                             | 2.0                                          |           |

| Page                                                          | Subjects (major changes since last revision) |           |

| 20                                                            | Revise outline dimension                     |           |

| 21                                                            | Add marking                                  |           |

|                                                               |                                              |           |

|                                                               |                                              |           |

|                                                               |                                              |           |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

CoolMOS<sup>®</sup>, CoolSET<sup>®</sup> are trademarks of Infineon Technologies AG.

Edition 2011-08-30

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 8/30/11. All Rights Reserved.

#### **Attention please!**

The information given in this data sheet shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## CoolSET<sup>®</sup> - Q1 ICE2QR1765Z

# Off-Line SMPS Quasi-Resonant PWM Controller with integrated 650V CoolMOS<sup>®</sup> and startup cell in DIP-7

## **Product Highlights**

- Quasi resonant operation

- Active Burst Mode to reach the lowest standby power requirement <100mW@no load</li>

- Digital frequency reduction for better overall system efficiency

- Integrated 650V avalanche rugged CoolMOS<sup>®</sup> with startup cell

- Pb-free lead plating; RoHS compliant

#### Features

- 650V avalanche rugged CoolMOS<sup>®</sup> with built-in startup cell

- · Quasi resonant operation till very low load

- Active burst mode operation for low standby input power (< 0.1W)</li>

- Digital frequency reduction with decreasing load for reduced switching loss

- Built-in digital soft-start

- Foldback point correction and cycle-by-cycle peak current limitation

- Maximum on/off time limitation

- Auto restart mode for VCC Overvoltage and Undervoltage protections

- Auto restart mode for overload protection

- Auto restart mode for overtemperature protection

- Latch-off mode for adjustable output overvoltage protection and transformer short-winding protection

## Description

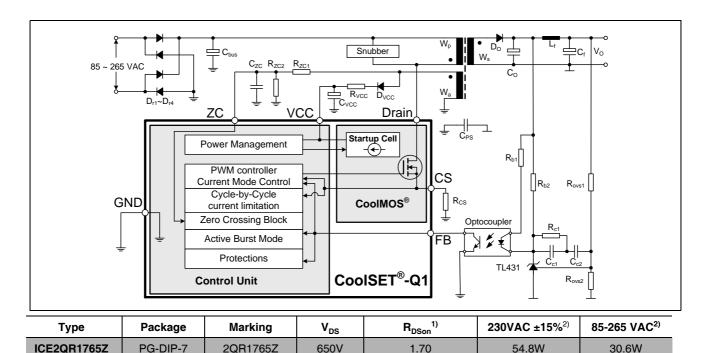

The CoolSET<sup>®</sup>-Q1 series (ICE2QRxx65Z) is the first generation of guasi-resonant integrated power ICs. It is optimized for off-line switch mode power supply applications such as LCD monitor, DVD R/W, DVD Combo, Blue-ray DVD, set top box, etc. Operating the MOSFET switch in quasi-resonant mode, lower EMI, higher efficiency and lower voltage stress on secondary diodes are expected for the SMPS. Based on the BiCMOS technology, the CoolSET®-Q1 series has a wide operation range (up to 25V) of IC power supply and lower power consumption. It also offers many advantages such as quasi-resonant operation till very low load which increases the average system efficiency, Active Burst Mode operation which enables an ultra-low power consumption at standby mode with small and controllable output voltage ripple, etc.

| 1) | typ | @ | T=25°C |

|----|-----|---|--------|

|----|-----|---|--------|

<sup>&</sup>lt;sup>2)</sup> Calculated maximum input power rating at  $T_a=50^{\circ}$ C,  $T_i=125^{\circ}$ C and without copper area as heat sink.

| ICE2QR1 |

|---------|

|         |

|         |

|         |

| Table of                                                                                                                                                      | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                                 | Pin Configuration and FunctionalityPin Configuration with PG-DIP-7Package PG-DIP-7Pin Functionality                                                                                                                                                                                                                                                                                                                                                                                                                       | 5<br>5<br>5                                                                     |

| 2                                                                                                                                                             | Representative Blockdiagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                               |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.1.2<br>3.3.1.3<br>3.3.2<br>3.4<br>3.4.1<br>3.5<br>3.5.1<br>3.5.1<br>3.5.2<br>3.5.3<br>3.6 | Functional Description         VCC Pre-Charging and Typical VCC Voltage During Start-up         Soft-start         Normal Operation         Digital Frequency Reduction         Up/down counter         Zero crossing (ZC counter)         Ringing suppression time         Switch Off Determination         Current Limitation         Foldback Point Correction         Active Burst Mode Operation         During Active Burst Mode Operation         Leaving Active Burst Mode Operation         Protection Functions | 7<br>7<br>7<br>8<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>10<br>10<br>10 |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>4.3.9<br>4.3.10                                      | Electrical Characteristics<br>Absolute Maximum Ratings<br>Operating Range<br>Characteristics<br>Supply Section<br>Internal Voltage Reference<br>PWM Section<br>Current Sense<br>Soft Start<br>Foldback Point Correction<br>Digital Zero Crossing<br>Active Burst Mode<br>Protection<br>CoolMOS® Section                                                                                                                                                                                                                   | 12<br>13<br>13<br>13<br>14<br>14<br>14<br>14<br>15<br>15<br>16                  |

| 5                                                                                                                                                             | Typical CoolMOS <sup>®</sup> Performance Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                                              |

| 6                                                                                                                                                             | Input power curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                              |

| 7                                                                                                                                                             | Outline Dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                              |

| 8                                                                                                                                                             | Marking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                                              |

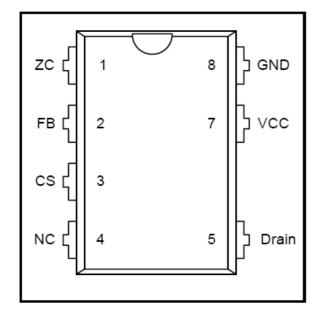

## **Pin Configuration and Functionality**

# **1** Pin Configuration and Functionality

## 1.1 Pin Configuration with PG-DIP-7

| Symbol | Function                                                               |

|--------|------------------------------------------------------------------------|

| ZC     | Zero Crossing                                                          |

| FB     | Feedback                                                               |

| CS     | Current Sense/<br>650V <sup>1)</sup> Depl. CoolMOS <sup>®</sup> Source |

| N.C.   | Not Connected                                                          |

| Drain  | 650V <sup>1)</sup> Depl. CoolMOS <sup>®</sup> Drain                    |

| VCC    | Controller Supply Voltage                                              |

| GND    | Controller Ground                                                      |

|        | ZC<br>FB<br>CS<br>N.C.<br>Drain<br>VCC                                 |

<sup>1)</sup> at  $T_i = 110^{\circ}C$

## 1.2 Package PG-DIP-7

Figure 1 Pin Configuration PG-DIP-7 (top view)

## 1.3 Pin Functionality

#### ZC (Zero Crossing)

At this pin, the voltage from the auxiliary winding after a time delay circuit is applied. Internally, this pin is connected to the zero-crossing detector for switch-on determination. Additionally, the output overvoltage detection is realized by comparing the voltage Vzc with an internal preset threshold.

#### FB (Feedback)

Normally, an external capacitor is connected to this pin for a smooth voltage  $V_{FB}$ . Internally, this pin is connected to the PWM signal generator for switch-off determination (together with the current sensing signal), the digital signal processing for the frequency reduction with decreasing load during normal operation, and the Active Burst Mode controller for entering Active Burst Mode operation determination and burst ratio control during Active Burst Mode operation. Additionally, the open-loop / over-load protection is implemented by monitoring the voltage at this pin.

#### CS (Current Sense)

This pin is connected to the external shunt resistor for the primary current sensing and the internal PWM signal generator for switch-off determination (together with the feedback voltage). Moreover, short-winding protection is realised by monitoring the voltage  $V_{\rm cs}$  during on-time of the main power switch.

#### Drain (Drain of integrated CoolMOS®)

Drain pin is the connection to the drain of the internal  $\text{CoolMOS}^{\textcircled{\text{B}}.}$

#### VCC (Power supply)

VCC pin is the positive supply of the IC. The operating range is between  $V_{\text{VCCoff}}$  and  $V_{\text{VCCOVP}}.$

#### GND (Ground)

This is the common ground of the controller.

## CoolSET<sup>®</sup> - Q1 ICE2QR1765Z

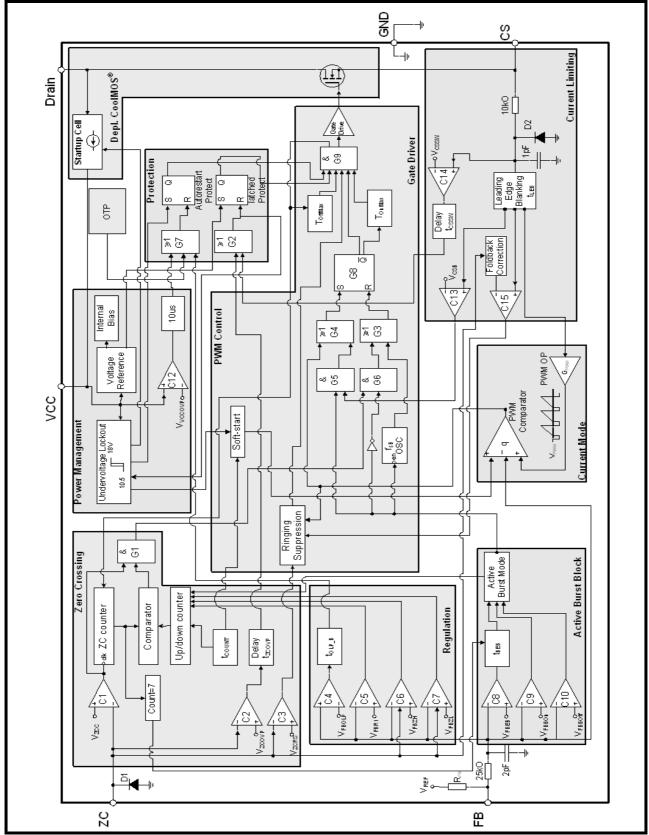

## **Representative Blockdiagram**

Figure 2 Representative Block diagram

### **Functional Description**

# 3 Functional Description

## 3.1 VCC Pre-Charging and Typical VCC Voltage During Start-up

In ICE2QR1765Z, a startup cell is integrated into the CoolMOS<sup>®</sup>. As shown in Figure 2, the start cell consists of a high voltage device and a controller, whereby the high voltage device is controlled by the controller. The startup cell provides a pre-charging of the VCC capacitor till VCC voltage reaches the VCC turned-on threshold  $V_{\rm VCCon}$  and the IC begins to operate.

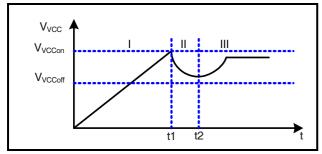

Once the mains input voltage is applied, a rectified voltage shows across the capacitor  $C_{bus}$ . The high voltage device provides a current to charge the VCC capacitor  $C_{vcc}$ . Before the VCC voltage reaches a certain value, the amplitude of the current through the high voltage device is only determined by its channel resistance and can be as high as several mA. After the VCC voltage device so that a constant current around 1mA is provided to charge the VCC capacitor further, until the VCC voltage exceeds the turned-on threshold  $V_{VCCon}$ . As shown in the time phase I in Figure 3, the VCC voltage increase near linearly and the charging speed is independent of the mains voltage level.

Figure 3 VCC voltage at start up

The time taking for the VCC pre-charging can then be approximately calculated as:

$$t_1 = \frac{V_{VCCon} \cdot C_{vcc}}{I_{VCCch} \operatorname{arge2}}$$

[1]

where  $l_{\rm VCCcharge2}$  is the charging current from the startup cell which is 1.05mA, typically.

When the VCC voltage exceeds the VCC turned-on threshold  $V_{VCCon}$  at time  $t_1$ , the startup cell is switched off and the IC begins to operate with soft-start. Due to power consumption of the IC and the fact that there is still no energy from the auxiliary winding to charge the VCC capacitor before the output voltage is built up, the VCC voltage drops (Phase II). Once the output voltage is high enough, the VCC capacitor receives the energy from the auxiliary winding from the time point  $t_2$  onward. The VCC will then reach a constant value depending on output load.

## 3.2 Soft-start

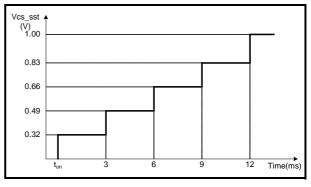

As shown in **Figure 4**, at the time  $t_{on}$ , the IC begins to operate with a soft-start. By this soft-start the switching stresses for the switch, diode and transformer are minimised. The soft-start implemented in ICE2QR1765Z is a digital time-based function. The preset soft-start time is **12ms** with 4 steps. If not limited by other functions, the peak voltage on CS pin will increase step by step from 0.32V to 1V finally.

Figure 4 Maximum current sense voltage during softstart

## 3.3 Normal Operation

The PWM controller during normal operation consists of a digital signal processing circuit including an up/ down counter, a zero-crossing counter (ZC counter) and a comparator, and an analog circuit including a current measurement unit and a comparator. The switch-on and -off time points are determined by the digital circuit and the analog circuit respectively. The zero-crossing input signal and the value of the up/down counter are needed for the switch-on determination while the feedback signal V<sub>FB</sub> and the current sensing signal V<sub>CS</sub> are necessary for the switch-off determination. Details about the full operation of the PWM controller in normal operation are illustrated in the following paragraphs.

#### 3.3.1 Digital Frequency Reduction

As mentioned above, the digital signal processing circuit consists of an up/down counter, a ZC counter and a comparator. These three parts are key to implement digital frequency reduction with decreasing load. In addition, a ringing suppression time controller is implemented to avoid mistriggering by the high frequency oscillation when the output voltage is very low under conditions such as soft start period or output short circuit. Functionality of these parts is described in the following.

## **Functional Description**

#### 3.3.1.1 Up/down counter

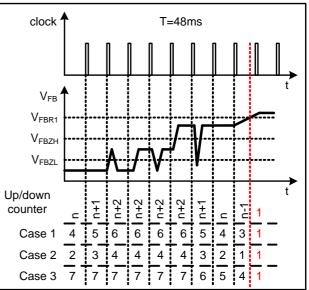

The up/down counter stores the number of the zero crossing where the main power switch is switched on after demagnetisation of the transformer. This value is fixed according to the feedback voltage,  $V_{FB}$ , which contains information about the output power. Indeed, in a typical peak current mode control, a high output power results in a high feedback voltage, and a low output power leads to a low regulation voltage. Hence, according to  $V_{FB}$ , the value in the up/down counter is changed to vary the power MOSFET off-time according to the output power. In the following, the variation of the up/down counter value according to the feedback voltage is explained.

The feedback voltage  $V_{FB}$  is internally compared with three threshold voltages  $V_{FBZL}$ ,  $V_{FBZH}$  and  $V_{FBR1}$ , at each clock period of 48ms. The up/down counter counts then upward, keep unchanged or count downward, as shown in Table 1.

Table 1

Operation of the up/down counter

| v <sub>FB</sub>                                                                 | up/down counter<br>action        |

|---------------------------------------------------------------------------------|----------------------------------|

| Always lower than $V_{\mbox{\scriptsize FBZL}}$                                 | Count upwards till<br>7          |

| Once higher than V <sub>FBZL</sub> , but<br>always lower than V <sub>FBZH</sub> | Stop counting, no value changing |

| Once higher than V <sub>FBZH</sub> , but<br>always lower than V <sub>FBR1</sub> | Count downwards till 1           |

| Once higher than $V_{FBR1}$                                                     | Set up/down counter to 1         |

In the ICE2QR1765Z, the number of zero crossing is limited to 7. Therefore, the counter varies between 1 and 7, and any attempt beyond this range is ignored. When  $V_{FB}$  exceeds  $V_{FBR1}$  voltage, the up/down counter is reset to 1, in order to allow the system to react rapidly to a sudden load increase. The up/down counter value is also reset to 1 at the start-up time, to ensure an efficient maximum load start up. **Figure 5** shows some examples on how up/down counter is changed according to the feedback voltage over time.

The use of two different thresholds  $V_{FBZL}$  and  $V_{FBZH}$  to count upward or downward is to prevent frequency jittering when the feedback voltage is close to the threshold point. However, for a stable operation, these two thresholds must not be affected by the foldback current limitation (see Section 3.4.1), which limits the  $V_{CS}$  voltage. Hence, to prevent such situation, the

threshold voltages,  $V_{\text{FBZL}}$  and  $V_{\text{FBZH}}$ , are changed internally depending on the line voltage levels.

Figure 5 Up/down counter operation

#### 3.3.1.2 Zero crossing (ZC counter)

In the system, the voltage from the auxiliary winding is applied to the zero-crossing pin through a RC network, which provides a time delay to the voltage from the auxiliary winding. Internally, this pin is connected to a clamping network, a zero-crossing detector, an output overvoltage detector and a ringing suppression time controller.

During on-state of the power switch a negative voltage applies to the ZC pin. Through the internal clamping network, the voltage at the pin is clamped to certain level.

The ZC counter has a minimum value of 0 and maximum value of 7. After the internal MOSFET is turned off, every time when the falling voltage ramp of on ZC pin crosses the 100mV threshold, a zero crossing is detected and ZC counter will increase by 1. It is reset every time after the DRIVER output is changed to high.

The voltage  $v_{ZC}$  is also used for the output overvoltage detection. Once the voltage at this pin is higher than the threshold  $V_{ZCOVP}$  during off-time of the main switch, the IC is latched off after a fixed blanking time.

To achieve the switch-on at voltage valley, the voltage from the auxiliary winding is fed to a time delay network (the RC network consists of  $D_{zc}$ ,  $R_{zc1}$ ,  $R_{zc2}$  and  $C_{zc}$  as shown in typical application circuit) before it is applied to the zero-crossing detector through the ZC pin. The needed time delay to the main oscillation signal D*t* should be approximately one fourth of the oscillation period (by transformer primary inductance and drainsource capacitance) minus the propagation delay from

the detected zero-crossing to the switch-on of the main switch  $t_{delay}$ , theoretically:

$$\Delta t = \frac{T_{osc}}{4} - t_{delay}$$

[2]

This time delay should be matched by adjusting the time constant of the RC network which is calculated as:

$$\tau_{td} = C_{zc} \cdot \frac{R_{zc1} \cdot R_{zc2}}{R_{zc1} + R_{zc2}}$$

[3]

#### 3.3.1.3 Ringing suppression time

After MOSFET is turned off, there will be some oscillation on  $V_{DS}$ , which will also appear on the voltage on ZC pin. To avoid mistriggering by such oscillations to turn on the MOSFET, a ringing suppression timer is implemented. This suppression time is depended on the voltage  $v_{ZC}$ . If the voltage  $v_{ZC}$  is lower than the threshold  $V_{ZCRS}$ , a longer preset time is applied. However, if the voltage  $v_{ZC}$  is higher than the threshold, a shorter time is set.

#### 3.3.1.4 Switch on determination

After the gate drive goes to low, it can not be changed to high during ring suppression time.

After ring suppression time, the gate drive can be turned on when the ZC counter value is higher or equal to up/down counter value.

However, it is also possible that the oscillation between primary inductor and drain-source capacitor damps very fast and IC can not detect enough zero crossings and ZC counter value will not be high enough to turn on the gate drive. In this case, a maximum off time is implemented. After gate drive has been remained off for the period of  $T_{OffMax}$ , the gate drive will be turned on again regardless of the counter values and  $V_{ZC}$ . This function can effectively prevent the switching frequency from going lower than 20kHz. Otherwise it will cause audible noise, during start up.

#### 3.3.2 Switch Off Determination

In the converter system, the primary current is sensed by an external shunt resistor, which is connected between low-side terminal of the main power switch and the common ground. The sensed voltage across the shunt resistor  $v_{CS}$  is applied to an internal current measurement unit, and its output voltage  $V_1$  is compared with the regulation voltage  $V_{FB}$ . Once the voltage  $V_1$  exceeds the voltage  $V_{FB}$ , the output flip-flop is reset. As a result, the main power switch is switched off. The relationship between the  $V_1$  and the  $V_{CS}$  is described by:

#### **Functional Description**

To avoid mistriggering caused by the voltage spike across the shunt resistor at the turn on of the main power switch, a leading edge blanking time,  $t_{LEB}$ , is applied to the output of the comparator. In other words, once the gate drive is turned on, the minimum on time of the gate drive is the leading edge blanking time.

In addition, there is a maximum on time,  $t_{OnMax}$ , limitation implemented in the IC. Once the gate drive has been in high state longer than the maximum on time, it will be turned off to prevent the switching frequency from going too low because of long on time.

#### 3.4 Current Limitation

There is a cycle by cycle current limitation realized by the current limit comparator to provide an overcurrent detection. The source current of the MOSFET is sensed via a sense resistor  $R_{CS}$ . By means of  $R_{CS}$  the source current is transformed to a sense voltage  $V_{CS}$  which is fed into the pin CS. If the voltage  $V_{CS}$  exceeds an internal voltage limit, adjusted according to the Mains voltage, the comparator immediately turns off the gate drive.

To prevent the Current Limitation process from distortions caused by leading edge spikes, a Leading Edge Blanking time ( $t_{LEB}$ ) is integrated in the current sensing path.

A further comparator is implemented to detect dangerous current levels ( $V_{CSSW}$ ) which could occur if one or more transformer windings are shorted or if the secondary diode is shorted. To avoid an accidental latch off, a spike blanking time of  $t_{CSSW}$  is integrated in the output path of the comparator.

#### 3.4.1 Foldback Point Correction

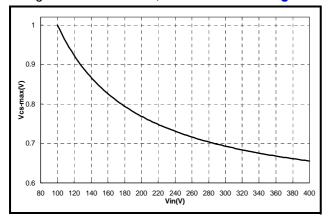

When the main bus voltage increases, the switch on time becomes shorter and therefore the operating frequency is also increased. As a result, for a constant primary current limit, the maximum possible output power is increased which is beyond the converter design limit.

To avoid such a situation, the internal foldback point correction circuit varies the  $V_{CS}$  voltage limit according to the bus voltage. This means the  $V_{CS}$  will be decreased when the bus voltage increases. To keep a constant maximum input power of the converter, the

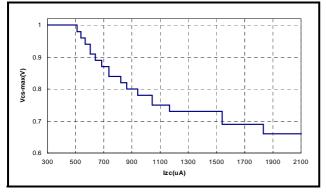

required maximum  $V_{CS}$  versus various input bus voltage can be calculated, which is shown in Figure 6.

Figure 6 Variation of the VCS limit voltage according to the  $I_{ZC}$  current

According to the typical application circuit, when MOSFET is turned on, a negative voltage proportional to bus voltage will be coupled to auxiliary winding. Inside CoolSET<sup>®</sup> - **Q1**, an internal circuit will clamp the voltage on ZC pin to nearly 0V. As a result, the current flowing out from ZC pin can be calculated as

$$I_{ZC} = \frac{V_{BUS}N_a}{R_{ZC1}N_P}$$

[5]

When this current is higher than  $I_{ZC_1}$ , the amount of current exceeding this threshold is used to generate an offset to decrease the maximum limit on  $V_{CS}$ . Since the ideal curve shown in **Figure 6** is a nonlinear one, a digital block in CoolSET<sup>®</sup> - **Q1** is implemented to get a better control of maximum output power. Additional advantage to use digital circuit is the production tolerance is smaller compared to analog solutions. The typical maximum limit on  $V_{CS}$  versus the ZC current is shown in **Figure 7**.

Figure 7  $V_{CS-max}$  versus  $I_{ZC}$

## 3.5 Active Burst Mode Operation

At light load condition, the IC enters Active Burst Mode operation to minimize the power consumption. Details

## **Functional Description**

about Active Burst Mode operation are explained in the following paragraphs.

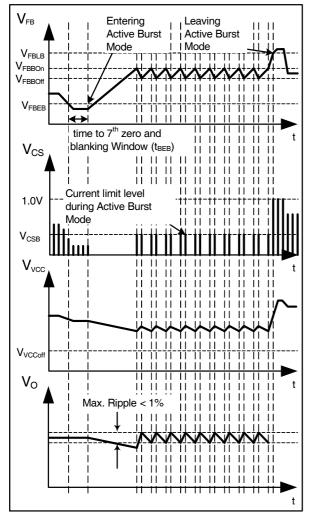

#### 3.5.1 Entering Active Burst Mode Operation

For determination of entering Active Burst Mode operation, three conditions apply:

- the feedback voltage is lower than the threshold of V<sub>FBEB</sub>(1.25V). Accordingly, the peak current sense voltage across the shunt resistor is 0.17V;

- the up/down counter is 7; and

- a certain blanking time (t<sub>BEB</sub>).

Once all of these conditions are fulfilled, the Active Burst Mode flip-flop is set and the controller enters Active Burst Mode operation. This multi-condition determination for entering Active Burst Mode operation prevents mistriggering of entering Active Burst Mode operation, so that the controller enters Active Burst Mode operation only when the output power is really low during the preset blanking time.

#### 3.5.2 During Active Burst Mode Operation

After entering the Active Burst Mode the feedback voltage rises as  $V_{OUT}$  starts to decrease due to the inactive PWM section. One comparator observes the feedback signal if the voltage level  $V_{BH}$  (3.6V) is exceeded. In that case the internal circuit is again activated by the internal bias to start with switching.

Turn-on of the power MOSFET is triggered by the timer. The PWM generator for Active Burst Mode operation composes of a timer with a fixed frequency of 52kHz, typically, and an analog comparator. Turn-off is resulted by comparison of the voltage signal v<sub>1</sub> with an internal threshold, by which the voltage across the shunt resistor V<sub>csB</sub> is 0.34V, accordingly. A turn-off can also be triggered by the maximal duty ratio controller which sets the maximal duty ratio to 50%. In operation, the output flip-flop will be reset by one of these signals which comes first.

If the output load is still low, the feedback signal decreases as the PWM section is operating. When feedback signal reaches the low threshold  $V_{BL}(3.0V)$ , the internal bias is reset again and the PWM section is disabled until the next regulation signal increases beyond the  $V_{BH}$  threshold. In Active Burst Mode, the feedback signal is changing like a saw tooth between 3.0V and 3.6V shown in Figure 8.

#### 3.5.3 Leaving Active Burst Mode Operation

The feedback voltage immediately increases if there is a high load jump. This is observed by one comparator. As the current limit is 34% during Active Burst Mode a certain load is needed so that feedback voltage can exceed  $V_{LB}$  (4.5V). After leaving active burst mode, maximum current can now be provided to stabilize  $V_0$ . In addition, the up/down counter will be set to 1

immediately after leaving Active Burst Mode. This is helpful to decrease the output voltage undershoot.

Figure 8 Signals in Active Burst Mode

## Functional Description

IC is reset and the main power switch is then kept off. After the VCC voltage falls below the threshold  $V_{VCCoff}$ , the startup cell is activated. The VCC capacitor is then charged up. Once the voltage exceeds the threshold  $V_{VCCon}$ , the IC begins to operate with a new soft-start.

In case of open control loop or output over load, the feedback voltage will be pulled up. After a blanking time of 24ms, the IC enters auto-restart mode. The blanking time here enables the converter to provide a max. power in case the increase in  $V_{FB}$  is due to a sudden load increase. During off-time of the power switch, the voltage at the zero-crossing pin is monitored for output over-voltage detection. If the voltage is higher than the preset threshold  $v_{ZCOVP}$ , the IC is latched off after the preset blanking time. This latch off mode can only be reset if the Vcc <6.23V.

If the junction temperature of IC exceeds 140 °C, the IC enters into autorestart mode (OTP).

If the voltage at the current sensing pin is higher than the preset threshold  $v_{\rm CSSW}$  during on-time of the power switch, the IC is latched off. This is short-winding protection.

During latch-off protection mode, the VCC voltage drops to 10.5V and then the startup cell is activated. The VCC voltage is then charged to 18V. The startup cell is shut down again. This action repeats again and again.

There is also a maximum on time limitation implemented inside the ICE2QR1765Z. Once the gate voltage is high and longer than  $t_{OnMAx}$ , the switch is turned off immediately.

## 3.6 **Protection Functions**

The IC provides full protection functions. The following table summarizes these protection functions.

| VCC Overvoltage    | Auto Restart Mode |  |  |

|--------------------|-------------------|--|--|

| VCC Undervoltage   | Auto Restart Mode |  |  |

| Overload/Open Loop | Auto Restart Mode |  |  |

| Over temperature   | Auto Restart Mode |  |  |

| Output Overvoltage | Latched Off Mode  |  |  |

| Short Winding      | Latched Off Mode  |  |  |

During operation, the VCC voltage is continuously monitored. In case of an under- or an over-voltage, the

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. For the same reason make sure, that any capacitor that will be connected to pin 7 (VCC) is discharged before assembling the application circuit.  $T_a=25^{\circ}$ C unless otherwise specified.

| Parameter                                                                     | Symbol              | Limit Values |      | Unit | Remarks                        |

|-------------------------------------------------------------------------------|---------------------|--------------|------|------|--------------------------------|

|                                                                               |                     | min.         | max. |      |                                |

| Drain Source Voltage                                                          | V <sub>DS</sub>     | -            | 650  | V    | T <sub>j</sub> =110°C          |

| Switching drain current, pulse width $t_p$ limited by $T_{jmax}$              | I <sub>s</sub>      | -            | 4.03 | A    |                                |

| Pulse drain current, pulse width $t_p$ limited by $T_{jmax}$                  | I <sub>D_Puls</sub> | -            | 6.12 | А    |                                |

| Avalanche energy, repetitive $t_{AR}$ limited by max. $T_j=150^{\circ}C^{1)}$ | E <sub>AR</sub>     | -            | 0.15 | mJ   |                                |

| Avalanche current, repetitive $t_{AR}$ limited by max. $T_j=150^{\circ}C$     | I <sub>AR</sub>     | -            | 1.5  | A    |                                |

| VCC Supply Voltage                                                            | V <sub>VCC</sub>    | -0.3         | 27   | V    |                                |

| FB Voltage                                                                    | V <sub>FB</sub>     | -0.3         | 5.5  | V    |                                |

| ZC Voltage                                                                    | V <sub>zc</sub>     | -0.3         | 5.5  | V    |                                |

| CS Voltage                                                                    | V <sub>CS</sub>     | -0.3         | 5.5  | V    |                                |

| Maximum current out from ZC pin                                               | I <sub>ZCMAX</sub>  | 3            | -    | mA   |                                |

| Junction Temperature                                                          | T <sub>j</sub>      | -40          | 150  | °C   | Controller & CoolMOS®          |

| Storage Temperature                                                           | T <sub>s</sub>      | -55          | 150  | °C   |                                |

| Thermal Resistance<br>Junction -Ambient                                       | R <sub>thJA</sub>   | -            | 96   | K/W  |                                |

| ESD Capability (incl. Drain Pin)                                              | V <sub>ESD</sub>    | -            | 2    | kV   | Human body model <sup>2)</sup> |

<sup>1)</sup> Repetitive avalanche causes additional power losses that can be calculated as  $P_{AV} = E_{AB}^* f$

<sup>2)</sup> According to EIA/JESD22-A114-B (discharging a 100pF capacitor through a 1.5kΩ series resistor)

## 4.2 Operating Range

Note: Within the operating range the IC operates as described in the functional description.

| Parameter          | Symbol           | Limit Values        |                     | Limit Values |  | Unit | Remarks |

|--------------------|------------------|---------------------|---------------------|--------------|--|------|---------|

|                    |                  | min.                | max.                |              |  |      |         |

| VCC Supply Voltage | V <sub>VCC</sub> | V <sub>VCCoff</sub> | V <sub>VCCOVP</sub> | V            |  |      |         |

Note: All voltages are measured with respect to ground (Pin 8). The voltage levels are valid if other ratings are not violated.

| Junction Temperature of<br>Controller        | T <sub>jCon</sub>     | -25 | 130 | °C | limited by over temperature protection |

|----------------------------------------------|-----------------------|-----|-----|----|----------------------------------------|

| Junction Temperature of CoolMOS <sup>®</sup> | T <sub>jCoolMOS</sub> | -25 | 150 | °C |                                        |

#### 4.3 Characteristics

#### 4.3.1 Supply Section

Note: The electrical characteristics involve the spread of values within the specified supply voltage and junction temperature range  $T_J$  from – 25 °C to 125 °C. Typical values represent the median values, which are related to 25°C. If not otherwise stated, a supply voltage of  $V_{CC}$  = 18 V is assumed.

| Parameter                                                      | Symbol                  | Limit Values |      |      | Unit | Test Condition                                                         |

|----------------------------------------------------------------|-------------------------|--------------|------|------|------|------------------------------------------------------------------------|

|                                                                |                         | min.         | typ. | max. |      |                                                                        |

| Start Up Current                                               | I <sub>VCCstart</sub>   | -            | 300  | 550  | mA   | V <sub>VCC</sub> =V <sub>VCCon</sub> -0.2V                             |

| VCC Charge Current                                             | I <sub>VCCcharge1</sub> | -            | 5.0  | -    | mA   | $V_{\rm VCC} = 0 \rm V$                                                |

|                                                                | I <sub>VCCcharge2</sub> | 0.8          | -    | -    | mA   | $V_{\rm VCC} = 1 \rm V$                                                |

|                                                                | I <sub>VCCcharge3</sub> | -            | 1    | -    | mA   | $V_{\rm VCC} = V_{\rm VCCon} - 0.2V$                                   |

| Maximum Input Current of Startup Cell and CoolMOS <sup>®</sup> | I <sub>DrainIn</sub>    | -            | -    | 2    | mA   | $V_{\rm VCC} = V_{\rm VCCon} - 0.2V$                                   |

| Leakage Current of<br>Startup Cell and CoolMOS <sup>®</sup>    | I <sub>DrainLeak</sub>  | -            | 0.2  | 50   | mA   | $V_{\text{Drain}} = 610V$<br>at $T_{\text{j}} = 100^{\circ}\text{C}$   |

| Supply Current in normal operation                             | I <sub>VCCNM</sub>      | -            | 1.5  | 2.3  | mA   | output low                                                             |

| Supply Current in<br>Auto Restart Mode with Inactive<br>Gate   | I <sub>VCCAR</sub>      | -            | 300  | -    | mA   | <i>I</i> <sub>FB</sub> = 0A                                            |

| Supply Current in Latch-off Mode                               | I <sub>VCClatch</sub>   | -            | 300  | -    | mA   |                                                                        |

| Supply Current in Burst Mode with inactive Gate                | I <sub>VCCburst</sub>   | -            | 500  | 950  | mA   | $V_{\rm FB}$ = 2.5V, exclude the<br>current flowing out from<br>FB pin |

| VCC Turn-On Threshold                                          | V <sub>VCCon</sub>      | 17.0         | 18.0 | 19.0 | V    |                                                                        |

| VCC Turn-Off Threshold                                         | V <sub>VCCoff</sub>     | 9.8          | 10.5 | 11.2 | V    |                                                                        |

| VCC Turn-On/Off Hysteresis                                     | V <sub>VCChys</sub>     | -            | 7.5  | -    | V    |                                                                        |

#### 4.3.2 Internal Voltage Reference

| Parameter                  | Symbol           | Symbol Limit Values |      | Unit | Test Condition |                                          |

|----------------------------|------------------|---------------------|------|------|----------------|------------------------------------------|

|                            |                  | min.                | typ. | max. |                |                                          |

| Internal Reference Voltage | V <sub>REF</sub> | 4.80                | 5.00 | 5.20 | V              | Measured at pin FB<br>/ <sub>FB</sub> =0 |

#### 4.3.3 PWM Section

| Parameter                           | Symbol             | Symbol Limit Values |      |      |    | Test Condition |

|-------------------------------------|--------------------|---------------------|------|------|----|----------------|

|                                     |                    | min.                | typ. | max. |    |                |

| Feedback Pull-Up Resistor           | R <sub>FB</sub>    | 14                  | 23   | 33   | kΩ |                |

| PWM-OP Gain                         | G <sub>PWM</sub>   | 3.18                | 3.3  | -    | -  |                |

| Offset for Voltage Ramp             | V <sub>PWM</sub>   | 0.6                 | 0.7  | -    | V  |                |

| Maximum on time in normal operation | t <sub>OnMax</sub> | 22                  | 30   | 41   | ms |                |

#### 4.3.4 Current Sense

| Parameter                                    | Symbol            |      | Limit Val | ues  | Unit | Test Condition |

|----------------------------------------------|-------------------|------|-----------|------|------|----------------|

|                                              |                   | min. | typ.      | max. |      |                |

| Peak current limitation in normal operation  | V <sub>CSth</sub> | 0.97 | 1.03      | 1.09 | V    |                |

| Leading Edge Blanking time                   | t <sub>LEB</sub>  | 200  | 330       | 460  | ns   |                |

| Peak Current Limitation in Active Burst Mode | V <sub>CSB</sub>  | 0.29 | 0.34      | 0.39 | V    |                |

#### 4.3.5 Soft Start

| Parameter                                      | Symbol                          | Limit Values |      |      | Unit | Test Condition |

|------------------------------------------------|---------------------------------|--------------|------|------|------|----------------|

|                                                |                                 | min.         | typ. | max. |      |                |

| Soft-Start time                                | t <sub>ss</sub>                 | 8.5          | 12   | -    | ms   |                |

| soft-start time step                           | t <sub>SS_S</sub> <sup>1)</sup> | -            | 3    | -    | ms   |                |

| Internal regulation voltage at first step      | V <sub>SS1</sub> <sup>1)</sup>  | -            | 1.76 | -    | V    |                |

| Internal regulation voltage step at soft start | V <sub>SS_S</sub> <sup>1)</sup> | -            | 0.56 | -    | V    |                |

<sup>1)</sup> The parameter is not subjected to production test - verified by design/characterization

#### 4.3.6 Foldback Point Correction

| Parameter                       | Symbol             | Limit Values |      |       | Unit | Test Condition                                |

|---------------------------------|--------------------|--------------|------|-------|------|-----------------------------------------------|

|                                 |                    | min.         | typ. | max.  |      |                                               |

| ZC current first step threshold | I <sub>ZC_FS</sub> | 0.350        | 0.5  | 0.621 | mA   |                                               |

| ZC current last step threshold  | I <sub>ZC_LS</sub> | 1.3          | 1.7  | 2.2   | mA   |                                               |

| CS threshold minimum            | V <sub>CSMF</sub>  | -            | 0.66 | -     | V    | I <sub>zc</sub> =2.2mA, V <sub>FB</sub> =3.8V |

#### 4.3.7 Digital Zero Crossing

| Parameter                                       | Symbol              |      | Unit | Test Condition |    |                     |

|-------------------------------------------------|---------------------|------|------|----------------|----|---------------------|

|                                                 |                     | min. | typ. | max.           |    |                     |

| Zero crossing threshold voltage                 | V <sub>ZCCT</sub>   | 50   | 100  | 170            | mV |                     |

| Ringing suppression threshold                   | V <sub>ZCRS</sub>   | -    | 0.7  | -              | V  |                     |

| Minimum ringing suppression<br>time             | t <sub>ZCRS1</sub>  | 1.62 | 2.5  | 4.5            | μS | $V_{ZC} > V_{ZCRS}$ |

| Maximum ringing suppression time                | t <sub>ZCRS2</sub>  | -    | 25   | -              | μs | $V_{ZC} < V_{ZCRS}$ |

| Threshold to set Up/Down<br>Counter to one      | V <sub>FBR1</sub>   | -    | 3.9  | -              | V  |                     |

| Threshold for downward counting at low line     | V <sub>FBZHL</sub>  | -    | 3.2  | -              | V  |                     |

| Threshold for upward counting at low line       | V <sub>FBZLL</sub>  | -    | 2.5  | -              | V  |                     |

| Threshold for downward counting at hig line     | V <sub>FBZHH</sub>  | -    | 2.9  | -              | V  |                     |

| Threshold for upward counting at highline       | V <sub>FBZLH</sub>  | -    | 2.3  | -              | V  |                     |

| ZC current for IC switch threshold to high line | I <sub>ZCSH</sub>   | -    | 1.3  | -              | mA |                     |

| ZC current for IC switch threshold to low line  | I <sub>ZCSL</sub>   | -    | 0.8  | -              | mA |                     |

| Counter time <sup>1)</sup>                      | t <sub>COUNT</sub>  | -    | 48   | -              | ms |                     |

| Maximum restart time in normal operation        | t <sub>OffMax</sub> | 30   | 42   | 57.5           | μS |                     |

<sup>1)</sup> The parameter is not subjected to production test - verified by design/characterization

#### 4.3.8 Active Burst Mode

| Parameter                                               | Symbol              |      | Limit Val | ues  | Unit | Test Condition |

|---------------------------------------------------------|---------------------|------|-----------|------|------|----------------|

|                                                         |                     | min. | typ.      | max. |      |                |

| Feedback voltage for entering<br>Active Burst Mode      | V <sub>FBEB</sub>   | -    | 1.25      | -    | V    |                |

| Minimum Up/down value for<br>entering Active Burst Mode | N <sub>ZC_ABM</sub> | -    | 7         | -    |      |                |

| Blanking time for entering Active<br>Burst Mode         | t <sub>BEB</sub>    | -    | 24        | -    | ms   |                |

| Feedback voltage for leaving<br>Active Burst Mode       | V <sub>FBLB</sub>   | -    | 4.5       | -    | V    |                |

| Feedback voltage for burst-on                           | V <sub>FBBOn</sub>  | -    | 3.6       | -    | V    |                |

| Feedback voltage for burst-off                          | V <sub>FBBOff</sub> | -    | 3.0       | -    | V    |                |

| Fixed Switching Frequency in<br>Active Burst Mode | f <sub>sB</sub>   | 39 | 52  | 65 | kHz |  |

|---------------------------------------------------|-------------------|----|-----|----|-----|--|

| Max. Duty Cycle in Active Burst<br>Mode           | D <sub>maxB</sub> | -  | 0.5 | -  |     |  |

#### 4.3.9 Protection

| Parameter                                                                     | Symbol              |      | Limit Val | ues  | Unit | Test Condition |

|-------------------------------------------------------------------------------|---------------------|------|-----------|------|------|----------------|

|                                                                               |                     | min. | typ.      | max. |      |                |

| VCC overvoltage threshold                                                     | V <sub>VCCOVP</sub> | 24.0 | 25.0      | 26.0 | V    |                |

| Over Load or Open Loop<br>Detection threshold for OLP<br>protection at FB pin | V <sub>FBOLP</sub>  | -    | 4.5       | -    | V    |                |

| Over Load or Open Loop<br>Protection Blanking Time                            | t <sub>OLP_B</sub>  | 20   | 30        | 44   | ms   |                |

| Output Overvoltage detection threshold at the ZC pin                          | V <sub>ZCOVP</sub>  | 3.55 | 3.7       | 3.84 | V    |                |

| Blanking time for Output<br>Overvoltage protection                            | t <sub>ZCOVP</sub>  | -    | 100       | -    | μs   |                |

| Threshold for short winding protection                                        | V <sub>CSSW</sub>   | 1.63 | 1.68      | 1.78 | V    |                |

| Blanking time for short-windding protection                                   | t <sub>cssw</sub>   | -    | 190       | -    | ns   |                |

| Over temperature protection <sup>1)</sup>                                     | T <sub>jCon</sub>   | 130  | 140       | 150  | °C   |                |

Note: The trend of all the voltage levels in the Control Unit is the same regarding the deviation except  $V_{VCCOVP}$

#### 4.3.10 CoolMOS<sup>®</sup> Section

| Parameter                                    | Symbol                   |      | Limit Valu          | es           | Unit   | Test Condition                                                                                          |

|----------------------------------------------|--------------------------|------|---------------------|--------------|--------|---------------------------------------------------------------------------------------------------------|

|                                              |                          | min. | typ.                | max.         |        |                                                                                                         |

| Drain Source Breakdown Voltage               | V <sub>(BR)DSS</sub>     | 650  | -                   | -            | V      | <i>T</i> <sub>j</sub> = 110°C                                                                           |

| Drain Source On-Resistance                   | R <sub>DSon1</sub>       | -    | 1.70<br>3.57        | 1.96<br>4.12 | Ω<br>Ω | $T_{\rm j} = 25^{\circ}{\rm C}$<br>$T_{\rm j} = 125^{\circ}{\rm C}^{1)}$<br>at $I_{\rm D} = 1.5{\rm A}$ |

| Effective output capacitance, energy related | C <sub>o(er)</sub>       | -    | 11.63 <sup>1)</sup> | -            | pF     | $V_{\rm DS} = 0$ V to 480V                                                                              |

| Rise Time                                    | <i>t</i> <sub>rise</sub> | -    | 30 <sup>2)</sup>    | -            | ns     |                                                                                                         |

| Fall Time                                    | t <sub>fall</sub>        | -    | 30 <sup>2)</sup>    | -            | ns     |                                                                                                         |

<sup>1)</sup> The parameter is not subjected to production test - verified by design/characterization

<sup>2)</sup> Measured in a Typical Flyback Converter Application

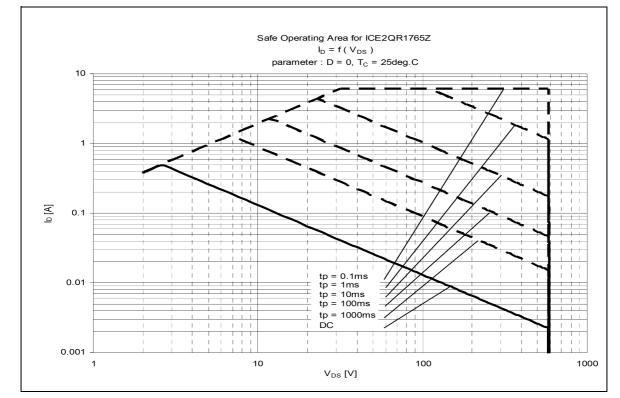

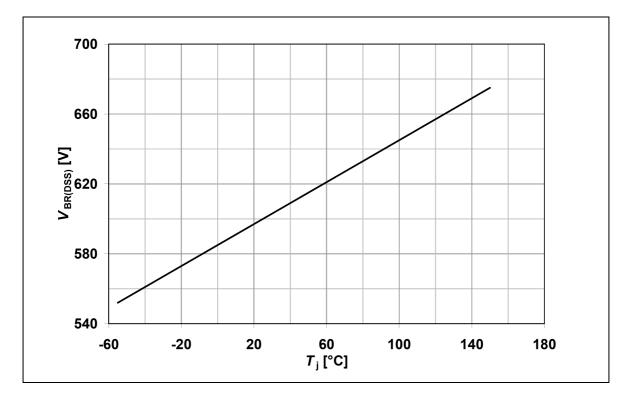

## Typical CoolMOS<sup>®</sup> Performance Characteristic

# 5 Typical CoolMOS<sup>®</sup> Performance Characteristic

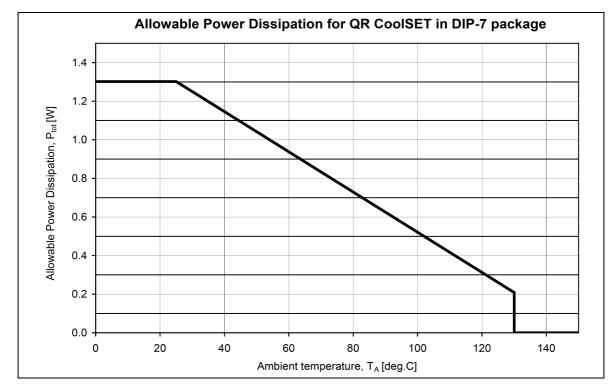

Figure 9 Safe Operating Area(SOA) curve for ICE2QR1765Z

Figure 10 Power dissipation;  $P_{tot}=f(T_a)$

## Typical CoolMOS<sup>®</sup> Performance Characteristic

Figure 11 Drain-source breakdown voltage;  $V_{BR(DSS)}=f(T_j)$

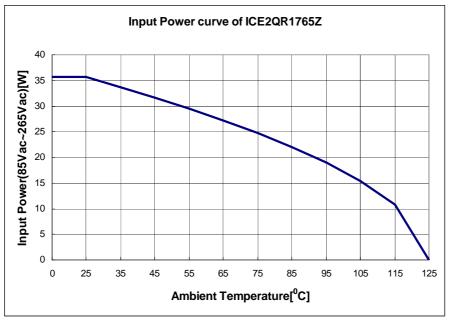

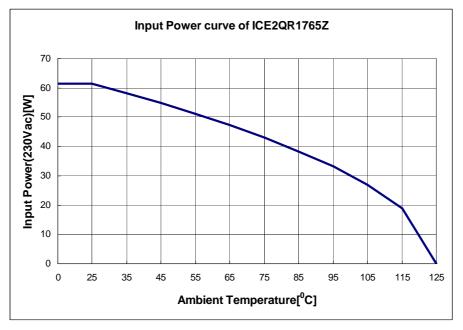

#### Input power curve

## 6 Input power curve

Two input power curves gives typical input power versus ambient temperature are showed below; Vin=85~265Vac(Figure 12) and Vin=230Vac(Figure 13). The curves are derived based on a typical discontinuous mode flyback model which considers 115V maximum secondary to primary reflected voltage(high priority). The calculation is based on no copper area as heatsink for the device. The input power already includes power loss at input comman mode choke and bridge rectifier and the CoolMOS<sup>®</sup>. The device saturation current( $I_{D_plus}@T_j=125$  °C) is also considered.

To estimate the out power of the device, it is simply multiplying the input power at a particulary ambient temperature with the estimated efficiency for the application. For example, a wide range input voltage(Figure 12), operating temperature is  $50 \,^{\circ}$ C, estimated efficiency is 85%, the output power is  $26W(30.6W^*0.85)$ .

Figure 12 Input Power curve Vin= $85 \sim 265$ Vac;Pin= $f(T_a)$

Figure 13 Input Power curve  $Vin=230Vac;Pin=f(T_a)$

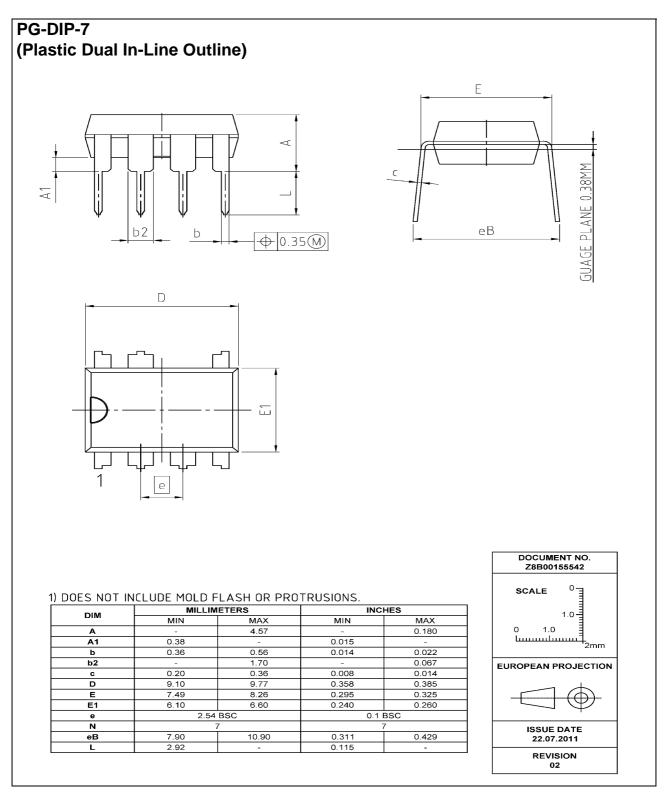

**Outline Dimension**

## 7 Outline Dimension

Figure 14 PG-DIP-7

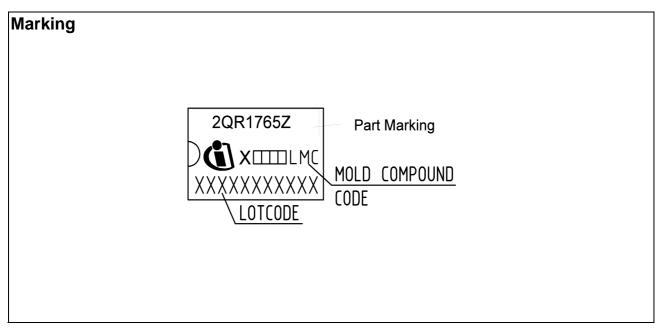

## Marking

# 8 Marking

Figure 15 Marking for ICE2QR1765Z

# **Total Quality Management**

Qualität hat für uns eine umfassende Bedeutung. Wir wollen allen Ihren Ansprüchen in der bestmöglichen Weise gerecht werden. Es geht uns also nicht nur um die Produktqualität – unsere Anstrengungen gelten gleichermaßen der Lieferqualität und Logistik, dem Service und Support sowie allen sonstigen Beratungs- und Betreuungsleistungen.

Dazu gehört eine bestimmte Geisteshaltung unserer Mitarbeiter. Total Quality im Denken und Handeln gegenüber Kollegen, Lieferanten und Ihnen, unserem Kunden. Unsere Leitlinie ist jede Aufgabe mit "Null Fehlern" zu lösen – in offener Sichtweise auch über den eigenen Arbeitsplatz hinaus – und uns ständig zu verbessern.

Unternehmensweit orientieren wir uns dabei auch an "top" (Time Optimized Processes), um Ihnen durch größere Schnelligkeit den entscheidenden Wettbewerbsvorsprung zu verschaffen.

Geben Sie uns die Chance, hohe Leistung durch umfassende Qualität zu beweisen. Quality takes on an allencompassing significance at Semiconductor Group. For us it means living up to each and every one of your demands in the best possible way. So we are not only concerned with product quality. We direct our efforts equally at quality of supply and logistics, service and support, as well as all the other ways in which we advise and attend to you.

Part of this is the very special attitude of our staff. Total Quality in thought and deed, towards co-workers, suppliers and you, our customer. Our guideline is "do everything with zero defects", in an open manner that is demonstrated beyond your immediate workplace, and to constantly improve.

Throughout the corporation we also think in terms of Time Optimized Processes (top), greater speed on our part to give you that decisive competitive edge.

Give us the chance to prove the best of performance through the best of quality – you will be convinced.

Wir werden Sie überzeugen.

http://www.infineon.com

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

#### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9