# **CYBL10X6X Family Datasheet**

# Programmable Radio-on-Chip With Bluetooth Low Energy (PRoC BLE)

# **General Description**

PRoC BLE is a 32-bit, 48-MHz ARM® Cortex®-M0 BLE solution with CapSense®, 12-bit ADC, four timer, counter, pulse-width modulators (TCPWM), thirty-six GPIOs, two serial communication blocks (SCBs), LCD, and I²S. PRoC BLE includes a royalty-free BLE stack compatible with Bluetooth® 4.1 and provides a complete, programmable, and flexible solution for HID, remote controls, toys, beacons, and wireless chargers. In addition to these applications, PRoC BLE provides a simple, low-cost way to add BLE connectivity to any system.

#### **Features**

# Bluetooth® Smart Connectivity

- Bluetooth 4.1 single-mode device

- 2.4-GHz BLE radio and baseband with integrated balun

- TX output power: -18 dBm to +3 dBm

- Received signal strength indicator (RSSI) with 1-dB resolution

- RX sensitivity: -89 dBm

- TX current: 15.6 mA at 0 dBm

- RX current: 16.4 mA

#### **ARM Cortex-M0 CPU Core**

- 32-bit processor (0.9 DMIPS/MHz) with single-cycle 32-bit multiply, operating at up to 48 MHz

- 128-KB flash memory

- 16-KB SRAM memory

- Emulated EEPROM using flash memory

- Watchdog timer with dedicated internal low-speed oscillator (ILO)

#### **Ultra-Low-Power**

- 1.3-µA Deep-Sleep mode with watch crystal oscillator (WCO) on

- 150-nA Hibernate mode current with SRAM retention

- 60-nA Stop mode current with GPIO wakeup

# CapSense® Touch Sensing with Two-Finger Gestures

- Up to 36 capacitive sensors for buttons, sliders, and touchpads

- Two-finger gestures: scroll, inertial scroll, pinch, stretch, and edge-swipe

- Cypress Capacitive Sigma-Delta (CSD) provides best-in-class SNR (> 5:1) and liguid tolerance

- Automatic hardware-tuning algorithm (SmartSense™)

#### **Peripherals**

- 12-bit, 1-Msps SAR ADC with internal reference, sample-and-hold (S/H), and channel sequencer

- Ultra-low-power LCD segment drive for 128 segments with operation in Deep-Sleep mode

- Two serial communication blocks (SCBs) supporting I<sup>2</sup>C (Master/Slave), SPI (Master/Slave), or UART

- Four dedicated 16-bit TCPWMs

□ Additional four 8-bit or two 16-bit PWMs

- Programmable LVD from 1.8 V to 4.5 V

- I<sup>2</sup>S Master interface

#### Clock, Reset, and Supply

- Wide supply-voltage range: 1.9 V to 5.5 V

- 3-MHz to 48-MHz internal main oscillator (IMO) with 2% accuracy

- 24-MHz external clock oscillator (ECO) without load capacitance

- 32-kHz WCO

# Programmable GPIOs

- 36 GPIOs configurable as open drain high/low, pull-up/pull-down, HI-Z, or strong output

- Any GPIO pin can be CapSense, LCD, or analog, with flexible pin routing

#### **Programming and Debug**

- 2-pin SWD

- In-system flash programming support

#### **Temperature and Packaging**

- Operating temperature range: -40 °C to +105 °C

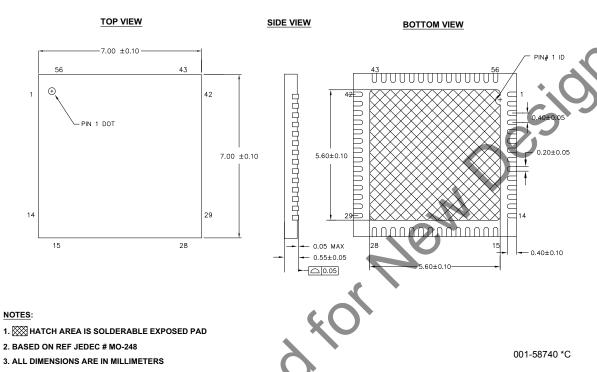

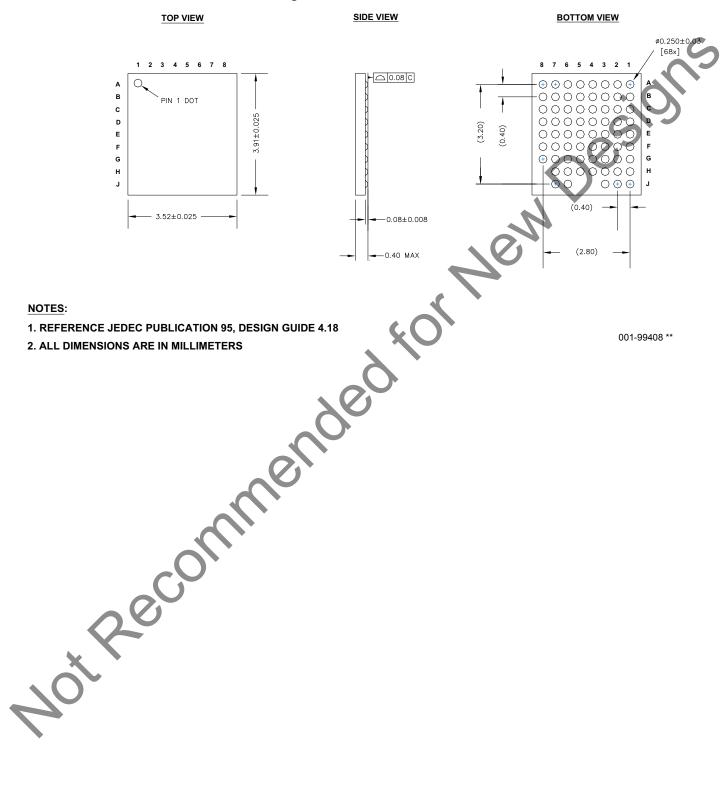

- Available in 56-pin QFN (7 mm × 7 mm) and 68-ball WLCSP (3.52 mm × 3.91 mm) packages

### PSoC<sup>®</sup> Creator™ Design Environment

- Easy-to-use IDE to configure, develop, program, and test a BLE application

- Option to export the design to Keil, IAR, or Eclipse

#### Bluetooth Low Energy Protocol Stack

- Bluetooth Low Energy protocol stack supporting generic access profile (GAP) Central, Peripheral, Observer, or Broadcaster roles

- □ Switches between Central and Peripheral roles on-the-go

- Standard Bluetooth Low Energy profiles and services for interoperability

- ☐ Custom profile and service for specific use cases

Cypress Semiconductor Corporation Document Number: 001-90478 Rev. \*L 198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised March 23, 2017

### **Contents**

| Blocks and Functionality    | 3  | Digital Peripherals             |

|-----------------------------|----|---------------------------------|

| CPU Subsystem               | 4  | Memory                          |

| BLE Subsystem               |    | System Resources                |

| System Resources Subsystem  |    | Ordering Information            |

| Peripheral Blocks           |    | Part Numbering Conventions      |

| Pinouts                     |    | Packaging                       |

| Power                       | 13 | Acronyms                        |

| Low-Power Modes             |    | Document Conventions            |

| Development Support         |    | Units of Measure                |

| Documentation               |    | Revision History                |

| Online                      |    | Sales, Solutions, and Legal Inf |

| Tools                       |    | Worldwide Sales and Design      |

| Kits                        | _  | Products                        |

| Electrical Specifications   |    | PSoC® Solutions                 |

| Absolute Maximum Ratings    |    | Cypress Developer Communication |

|                             |    | Technical Support               |

| BLE Subsystem               |    | recriffical Support             |

| Device-Level Specifications |    |                                 |

| Analog Peripherals          | 24 |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    | <b>(()</b>                      |

|                             |    | . 10                            |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             | 10 |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

| Hoibec                      |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

|                             |    |                                 |

| 26 |

|----|

| 29 |

| 29 |

| 33 |

| 34 |

| 35 |

| 38 |

| 40 |

| 40 |

| 41 |

| 42 |

| 42 |

| 42 |

| 42 |

| 42 |

| 42 |

|    |

# **Blocks and Functionality**

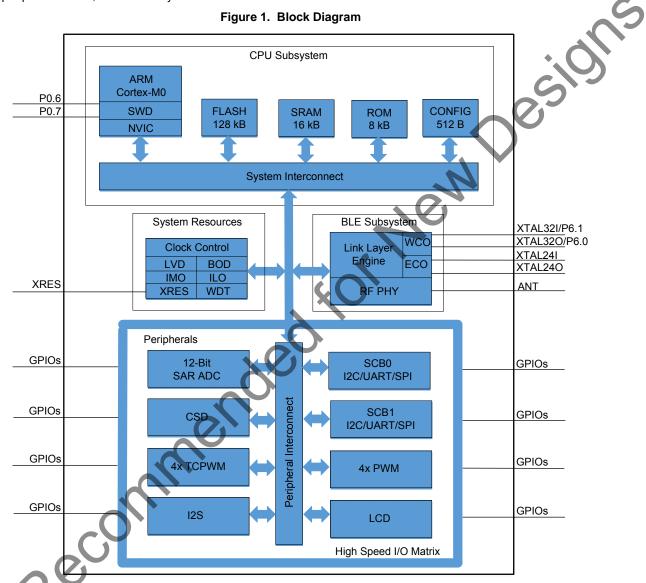

The CYBL10X6X block diagram is shown in Figure 1. There are five major subsystems: CPU subsystem, BLE subsystem, system resources, peripheral blocks, and I/O subsystem.

The PRoC BLE family includes extensive support for programming, testing, debugging, and tracing both hardware and firmware. The complete debug-on-chip functionality enables full-device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE provides fully integrated programming and debug support for PRoC BLE devices. The SWD interface is fully compatible with industry-standard third-party tools. PRoC BLE also supports disabling the SWD interface and has a robust flash-protection feature.

#### CPU Subsystem

#### CPU

The CYBL10X6X device is based on an energy-efficient ARM Cortex-M0 32-bit processor, offering low power consumption, high performance, and reduced code size using 16-bit thumb instructions. The Cortex-M0's ability to perform single-cycle 32-bit arithmetic and logic operations, including single-cycle 32-bit multiplication, helps in better performance. The inclusion of the tightly-integrated Nested Vectored Interrupt Controller (NVIC) with 32 interrupt lines enables the Cortex-M0 to achieve a low latency and a deterministic interrupt response.

The CPU also includes a 2-pin interface, the serial wire debug (SWD), which is a 2-wire form of JTAG. The debug circuits are enabled by default and can only be disabled in firmware. If disabled, the only way to re-enable them is to erase the entire device, clear flash protection, and reprogram the device with the new firmware that enables debugging. In addition, it is possible to use the debug pins as GPIO too. The device has four breakpoints and two watchpoints for effective debugging.

#### Flash

The device has a 128-KB flash memory with a flash accelerator, tightly coupled to the CPU to improve average access times from flash. The flash is designed to deliver 1-wait-state (WS) access time at 48 MHz and with 0-WS access time at 24 MHz. The flash accelerator delivers 85% of single-cycle SRAM access performance on average. Part of the flash can be used to emulate EEPROM operation, if required.

During flash erase and programming operations (the maximum erase and program time is 20 ms per row), the IMO will be set to 48 MHz for the duration of the operation. This also applies to the emulated EEPROM. System design must take this into account because peripherals operating from different IMO frequencies will be affected. If it is critical that peripherals continue to operate with no change during flash programming, always set the IMO to 48 MHz and derive the peripheral clocks by dividing down from this frequency.

#### **SRAM**

The low-power 16-KB SRAM memory retains its contents even in Hibernate mode.

#### ROM

The 8-KB supervisory ROM contains a library of executable functions for flash programming. These functions are accessed through supervisory calls (SVC) and enable in-system programming of the flash memory.

# **BLE Subsystem**

The BLE subsystem consists of the link layer engine and physical layer. The link layer engine supports both master and slave roles. The link layer engine implements time-critical functions such as encryption in the hardware to reduce the power consumption, and provides minimal processor intervention and a high performance. The key protocol elements, such as host control interface (HCI) and link control, are implemented in firmware. The direct test mode (DTM) is included to test the radio performance using a standard Bluetooth tester.

The physical layer consists of a modem and an RF transceiver that transmits and receives BLE packets at the rate of 1 Mbps over the 2.4-GHz ISM band. In the transmit direction, this block performs GFSK modulation and then converts the digital baseband signal of these BLE packets into radio frequency before transmitting them to air through an antenna. In the receive direction, this block converts an RF signal from the antenna to a digital bit stream after performing GFSK demodulation

The RF transceiver contains an integrated balun, which provides a single-ended RF port pin to drive a  $50-\Omega$  antenna terminal through a pi-matching network. The output power is programmable from -18 dBm to +3 dBm to optimize the current consumption for different applications.

The Bluetooth Low Energy protocol stack uses the BLE subsystem and provides the following features:

- Link Layer (LL)

- □ Master and Slave roles

- □ 128-bit AES engine

- □ Encryption

- □ Low-duty-cycle advertising (Bluetooth 4.1 feature)

- □ LE ping (Bluetooth 4.1 feature)

- Bluetooth Low Energy 4.1 single-mode protocol stack with logical link control and adaptation protocol (L2CAP), attribute (ATT), and security manager (SM) protocols

- Master and slave roles

- API access to generic attribute profile (GATT), generic access profile (GAP), and L2CAP

- ■L2CAP connection-oriented channel (Bluetooth 4.1 feature)

- GAP features

- □ Broadcaster, Observer, Peripheral, and Central roles

- ☐ Security mode 1: Level 1, 2, and 3

- □ Security mode 2: Level 1 and 2

- □ User-defined advertising data

- □ Multiple-bond support

- GATT features

- □ GATT client and server

- □ Supports GATT subprocedures

- 32-bit universally unique identifiers (UUID) (Bluetooth 4.1 feature)

- Security Manager (SM)

- □ Pairing methods: Just Works, Passkey Entry, and Out of Band

- Authenticated man-in-the-middle (MITM) protection and data signing

- Supports all SIG-adopted BLE profiles

#### System Resources Subsystem

#### Power

The power block includes internal LDOs that supply required voltage levels for different blocks. The power system also includes POR, BOD, and LVD circuits. The POR circuit holds the device in the reset state until the power supplies have stabilized at appropriate levels and the clock is ready. The BOD circuit resets the device when the supply voltage is too low for proper device operation. The LVD circuit generates an interrupt if the supply voltage drops below a user-selectable level.

An external active-LOW reset pin (XRES) can be used to reset the device. The XRES pin has an internal pull-up resistor and, in most applications, does not require any additional pull-up resistors. The power system is described in detail in the "Power" section on page 13.

#### Clock Control

The PRoC BLE clock control is responsible for providing clocks to all subsystems and also for switching between different clock sources without glitching. The clock control for PRoC BLE consists of the IMO and the internal low-speed oscillator (ILO). It uses the 24-MHz external crystal oscillator (ECO) and the 32-kHz WCO. In addition, an external clock may be supplied from a pin.

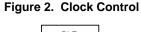

The device has 12 dividers with 16 divider outputs. Two dividers have additional fractional division capability. The HFCLK signal is divided down, as shown in Figure 2, to generate the system clock (SYSCLK) and peripheral clock (PERx\_CLK) for different

peripherals. The system clock (SYSCLK) driving buses, registers, and the processor must be higher than all the other clocks in the system that are divided off HFCLK. The ECO and WCO are present in the BLE subsystem and the clock outputs are routed to the system resources.

#### Internal Main Oscillator (IMO)

The IMO is the primary system clock source, which can be adjusted in the range of 3 MHz to 48 MHz in steps of 1 MHz. The IMO accuracy is  $\pm 2\%$ .

#### Internal Low-Speed Oscillator (ILO)

The ILO is a very-low-power 32-kHz oscillator, which is primarily used to generate clocks for peripheral operations in Deep-Sleep mode. The ILO-driven counters can be calibrated to the IMO to improve accuracy. Cypress provides a software component, which does the calibration.

# External Crystal Oscillator (ECO)

The ECO is used as the active clock for the BLE subsystem to meet the ±50-ppm clock accuracy requirement of the Bluetooth 4.1 specification. The ECO includes a tunable load capacitor to tune the crystal clock frequency by measuring the actual clock frequency. The high-accuracy ECO clock can also be used as a system clock.

#### Watch Crystal Oscillator (WCO)

The WCO is used as the sleep clock for the BLE subsystem to meet the ±500-ppm clock accuracy requirement of the Bluetooth 4.1 specification. The sleep clock provides accurate sleep timing and enables wakeup at specified advertisement and connection intervals. With the WCO and firmware, an accurate real-time clock (within the bounds of the 32.768-kHz crystal accuracy) can be realized.

#### Voltage Reference

The internal bandgap reference circuit with 1% accuracy provides the voltage reference for the 12-bit SAR ADC. To enable better SNRs and absolute accuracy, it will be possible to bypass the internal bandgap reference using a REF pin and to use an external reference for the SAR.

#### Watchdog Timer (WDT)

A watchdog timer is implemented in the system resources subsystem running from the ILO; this allows watchdog operations during Deep-Sleep mode and generates a watchdog reset if not serviced before the timeout occurs. The watchdog reset is recorded in the 'Reset Cause' register.

### Peripheral Blocks

#### 12-Bit SAR ADC

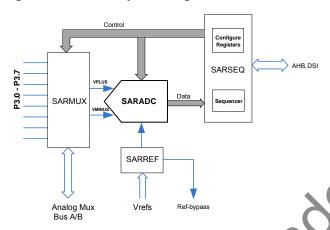

The ADC is a 12-bit, 1-Msps SAR ADC with a built-in sample-and-hold (S/H) circuit. The ADC can operate with either an internal voltage reference or an external voltage reference.

Preceding the SAR ADC is the SARMUX, which can route external pins and internal signals (analog mux bus and temperature sensor output) to the eight internal channels of the SAR ADC. The sequencer controller (SARSEQ) is used to control the SARMUX and SAR ADC to do an automatic scan on all enabled channels without CPU intervention and for preprocessing tasks such as averaging the output data. A Cypress-supplied software driver (Component) is used to control the ADC peripheral.

Figure 3. SAR ADC System Diagram

A diode based, on-chip temperature sensor is used to measure the die temperature. The temperature sensor is connected to the ADC, which digitizes the reading and produces a temperature value using the Cypress-supplied software that includes calibration and linearization.

#### 4x Timer Counter PWM (TCPWM)

The 16-bit TCPWM module can be used to generate the PWM output or to capture the timing of edges of input signals or to provide a timer functionality. TCPWM can also be used as a 16-bit counter that supports up, down, and up/down counting modes.

Rising edge, falling edge, combined rising/falling edge detection, or pass-through on all hardware input signals can be used to derive counter events. Three routed output signals are available to indicate underflow, overflow, and counter/compare match events. A maximum of four TCPWMs are available.

#### 4x PWM

These PWMs are in addition to the TCPWMs. The PWM peripheral can be configured as 8-bit or 16-bit resolution. The PWM provides compare outputs to generate single or continuous timing and control signals in hardware. It also provides an easy method of generating complex real-time events accurately with minimal CPU intervention. A maximum of four 8-bit PWMs or two 16-bit PWMs are available.

Serial Communication Block (SCB0/SCB1)

The SCB can be configured as an I<sup>2</sup>C, UART, or SPI interface. It supports an 8-byte FIFO for receive and transmit buffers to reduce CPU intervention. A maximum of two SCBs (SCB0, SCB1) are available.

$I^2C$  mode: The  $I^2C$  peripheral is compatible with the  $I^2C$  Standard-mode, Fast-mode, and Fast-Mode-Plus devices as defined in the NXP  $I^2C$ -bus specification and user manual (UM10204). The  $I^2C$  bus I/O is implemented with GPIOs in open-drain modes.

The hardware I<sup>2</sup>C block implements a full multimaster and slave interface (it is capable of multimaster arbitration). This block is capable of operating at speeds of up to 1 Mbps (Fast-Mode Plus) and has flexible buffering options to reduce the interrupt overhead and latency for the CPU. The I<sup>2</sup>C function is implemented using the Cypress-provided software Component (EzI2C) that creates a mailbox address range in the memory of PRoC BLE and effectively reduces the I<sup>2</sup>C communication to reading from and writing to an array in memory. In addition, the block supports an 8-byte FIFO for receive and transmit, which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read the data on time.

When SCB0 is used, Serial Data (SDA) and Serial Clock (SCL) of I<sup>2</sup>C can be connected to P0.4 and P0.5, or P1.4 and P1.5, or P3.0 and P3.1.

When SCB1 is used, SDA and SCL can be connected to P0.0 and P0.1, or P3.4 and P3.5, or P5.0 and P5.1.

Configurations for I<sup>2</sup>C are as follows:

- SCB1 is fully compliant with the Standard-mode (100 kHz), Fast-mode (400 kHz), and Fast-Mode-Plus (1 MHz) I<sup>2</sup>C signaling specifications when routed to GPIO pins P5.0 and P5.1, except for hot-swap capability during I<sup>2</sup>C active communication.

- SCB1 is compliant only with Standard mode (100 kHz) when not used with P5.0 and P5.1.

- SCB0 is compliant with Standard mode (100 kHz) only.

**UART mode:** This is a full-feature UART operating up to 1 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO7816) protocols. In addition, it supports the 9-bit multiprocessor mode, which allows addressing of peripherals connected over common RX and TX lines. The UART hardware flow control is supported to allow slow and fast devices to communicate with each other over UART without the risk of losing data. Refer to Table 4 on page 11 for possible UART connections to the GPIOs.

**SPI Mode:** The SPI mode supports full Motorola® SPI, Texas Instruments® Secure Simple Pairing (SSP) (essentially adds a start pulse used to synchronize SPI Codecs), and National Microwire (half-duplex form of SPI). This block supports an 8-byte FIFO for receive and transmit. Refer to Table 4 on page 11 for the possible SPI connections to the GPIOs.

#### Inter-IC Sound Bus (I<sup>2</sup>S)

Inter-IC Sound Bus (I<sup>2</sup>S) is a serial bus interface standard used for connecting digital audio devices. The specification is from Philips<sup>®</sup> Semiconductor (I<sup>2</sup>S bus specification; February 1986, revised June 5, 1996).

$I^2S$  operates only in the Master mode, supporting the transmitter (TX) and the receiver (RX), which have independent data byte streams. These byte streams are packed with the most significant byte first. The number of bytes used for each sample (a sample for the left or right channel) is the minimum number of bytes to hold a sample.

#### LCD

The LCD controller can drive up to four commons and up to 32 segments. It uses full digital methods to drive the LCD segments providing ultra-low power consumption. The two methods used are referred to as digital correlation and PWM.

The digital correlation method modulates the frequency and signal levels of the commons and segments to generate the highest RMS voltage across a segment to light it up or to maintain the RMS signal as zero. This method is good for STN displays but may result in reduced contrast in TN (cheaper) displays.

The PWM method drives the panel with PWM signals to effectively use the capacitance of the panel to provide the integration of the modulated pulse-width to generate the desired LCD voltage. This method results in higher power consumption but provides better results in driving TN displays.

LCD operation is supported during Deep-Sleep mode by refreshing a small display buffer (four bits; one 32-bit register per port).

#### CapSense

CapSense is supported on all GPIOs through a Capacitive Sigma-Delta (CSD) block, which can be connected to any GPIO through an analog mux bus. Any GPIO pin can be connected to the analog mux bus via an analog switch. The CapSense function can thus be provided on any pin or group of pins in a system under software control. A software Component in PSoC Creator is provided for the CapSense block to make it easy for the user. The shield voltage can be driven on another mux bus to provide liquid-tolerance capability. Driving the shield electrode

in phase with the sense electrode keeps the shield capacitance from attenuating the sensed input.

The CapSense trackpad/touchpad with gestures has the following features:

- Supports 1-finger and 2-finger touch applications

- Supports up to 35 X/Y sensor inputs

- Includes a gesture-detection library:

- □ 1-finger touch: tracing, pan, click, double-click

- □ 2-finger touch: pan, click, zoom

#### I/O Subsystem

The I/O subsystem, which comprises the GPIO block, implements the following:

- Eight drive-strength modes:

- ☐ Analog input mode (input and output buffers disabled)

- □ Input only

- □ Weak pull-up with strong pull-down

- □ Weak pull-up with weak pull-down

- ☐ Strong pull-up with weak pull-down

- □ Strong pull-up with strong pull-down

- □ Open drain with strong pull-down

- □ Open drain with strong pull-up

- Port pins: 36

- Input threshold select (CMOS or LVTTL)

- Individual control of input and output buffers (enabling/disabling) in addition to drive-strength modes

- Hold mode for latching the previous state (used for retaining the I/O state in Deep Sleep and Hibernate modes)

- Selectable slew rates for dV/dt to improve EMI

- The GPIO pins P5.0 and P5.1 are overvoltage-tolerant

- The GPIO cells, including P5.0 and P5.1, cannot be hot-swapped or powered up independent of the rest of the system.

# **Pinouts**

Table 1 shows the pin list for the CYBL10X6X device.

Table 1. CYBL10X6X Pin List (QFN Package)

| Pin | Name         | Туре    | Description                                |

|-----|--------------|---------|--------------------------------------------|

| 1   | VDDD         | POWER   | 1.71-V to 5.5-V digital supply             |

| 2   | XTAL320/P6.0 | CLOCK   | 32.768-kHz crystal                         |

| 3   | XTAL32I/P6.1 | CLOCK   | 32.768-kHz crystal or external clock input |

| 4   | XRES         | RESET   | Reset, active LOW                          |

| 5   | P4.0         | GPIO    | Port 4 Pin 0, analog/digital/lcd/csd       |

| 6   | P4.1         | GPIO    | Port 4 Pin 1, analog/digital/lcd/csd       |

| 7   | P5.0         | GPIO    | Port 5 Pin 0, analog/digital/lcd/csd       |

| 8   | P5.1         | GPIO    | Port 5 Pin 1, analog/digital/lcd/csd       |

| 9   | VSSD         | GROUND  | Digital ground                             |

| 10  | VDDR         | POWER   | 1.9-V to 5.5-V radio supply                |

| 11  | GANT1        | GROUND  | Antenna shielding ground                   |

| 12  | ANT          | ANTENNA | Antenna pin                                |

| 13  | GANT2        | GROUND  | Antenna shielding ground                   |

| 14  | VDDR         | POWER   | 1.9-V to 5.5-V radio supply                |

| 15  | VDDR         | POWER   | 1.9-V to 5.5-V radio supply                |

| 16  | XTAL24I      | CLOCK   | 24-MHz crystal or external clock input     |

| 17  | XTAL24O      | CLOCK   | 24-MHz crystal                             |

| 18  | VDDR         | POWER   | 1.9-V to 5.5-V radio supply                |

| 19  | P0.0         | GPIO    | Port 0 Pín 0, analog/digital/lcd/csd       |

| 20  | P0.1         | GPIO    | Port 0 Pin 1, analog/digital/lcd/csd       |

| 21  | P0.2         | GPIO    | Port 0 Pin 2, analog/digital/lcd/csd       |

| 22  | P0.3         | GPIO    | Port 0 Pin 3, analog/digital/lcd/csd       |

| 23  | VDDD         | POWER   | 1.71-V to 5.5-V digital supply             |

| 24  | P0.4         | GPIO    | Port 0 Pin 4, analog/digital/lcd/csd       |

| 25  | P0.5         | GPIO    | Port 0 Pin 5, analog/digital/lcd/csd       |

| 26  | P0.6         | GPIO    | Port 0 Pin 6, analog/digital/lcd/csd       |

| 27  | P0.7         | GPIO    | Port 0 Pin 7, analog/digital/lcd/csd       |

| 28  | P1.0         | GPIO    | Port 1 Pin 0, analog/digital/lcd/csd       |

| 29  | P1.1         | GPIO    | Port 1 Pin 1, analog/digital/lcd/csd       |

| 30  | P1.2         | GPIO    | Port 1 Pin 2, analog/digital/lcd/csd       |

| 31  | P1.3         | GPIO    | Port 1 Pin 3, analog/digital/lcd/csd       |

| 32  | P1.4         | GPIO    | Port 1 Pin 4, analog/digital/lcd/csd       |

| 33  | P1.5         | GPIO    | Port 1 Pin 5, analog/digital/lcd/csd       |

| 34  | P1.6         | GPIO    | Port 1 Pin 6, analog/digital/lcd/csd       |

| 35  | P1.7         | GPIO    | Port 1 Pin 7, analog/digital/lcd/csd       |

| 36  | VDDA         | POWER   | 1.71-V to 5.5-V analog supply              |

| 37  | P2.0         | GPIO    | Port 2 Pin 0, analog/digital/lcd/csd       |

| 38  | P2.1         | GPIO    | Port 2 Pin 1, analog/digital/lcd/csd       |

| 39  | P2.2         | GPIO    | Port 2 Pin 2, analog/digital/lcd/csd       |

| 40  | P2.3         | GPIO    | Port 2 Pin 3, analog/digital/lcd/csd       |

Document Number: 001-90478 Rev. \*L Page 8 of 42

Table 1. CYBL10X6X Pin List (QFN Package) (continued)

| Pin | Name | Туре   | Description                                       |

|-----|------|--------|---------------------------------------------------|

| 41  | P2.4 | GPIO   | Port 2 Pin 4, analog/digital/lcd/csd              |

| 42  | P2.5 | GPIO   | Port 2 Pin 5, analog/digital/lcd/csd              |

| 43  | P2.6 | GPIO   | Port 2 Pin 6, analog/digital/lcd/csd              |

| 44  | P2.7 | GPIO   | Port 2 Pin 7, analog/digital/lcd/csd              |

| 45  | VREF | REF    | 1.024-V reference                                 |

| 46  | VDDA | POWER  | 1.71-V to 5.5-V analog supply                     |

| 47  | P3.0 | GPIO   | Port 3 Pin 0, analog/digital/lcd/csd              |

| 48  | P3.1 | GPIO   | Port 3 Pin 1, analog/digital/lcd/csd              |

| 49  | P3.2 | GPIO   | Port 3 Pin 2, analog/digital/lcd/csd              |

| 50  | P3.3 | GPIO   | Port 3 Pin 3, analog/digital/lcd/csd              |

| 51  | P3.4 | GPIO   | Port 3 Pin 4, analog/digital/lcd/csd              |

| 52  | P3.5 | GPIO   | Port 3 Pin 5, analog/digital/lcd/csd              |

| 53  | P3.6 | GPIO   | Port 3 Pin 6, analog/digital/lcd/csd              |

| 54  | P3.7 | GPIO   | Port 3 Pin 7, analog/digital/lcd/csd              |

| 55  | VSSA | GROUND | Analog ground                                     |

| 56  | VCCD | POWER  | Regulated 1.8-V supply; connect to 1-µF capacitor |

| 57  | EPAD | GROUND | Ground paddle for the QFN package                 |

Table 2 shows the pin list for the CYBL10X6X device (WLCSP package).

Table 2. CYBL10X6X Pin List (WLCSP Package)

| Pin | Name         | Туре   | Description                                       |

|-----|--------------|--------|---------------------------------------------------|

| A1  | VREF         | REF    | 1.024-V reference                                 |

| A2  | VSSA         | GROUND | Analog ground                                     |

| A3  | P3.3         | GPIO   | Port 3 Pin 3, analog/digital/lcd/csd              |

| A4  | P3.7         | GPIO   | Port 3 Pin 7, analog/digital/lcd/csd              |

| A5  | VSSD         | GROUND | Digital ground                                    |

| A6  | VSSA         | GROUND | Analog ground                                     |

| A7  | VCCD         | POWER  | Regulated 1.8-V supply, connect to 1-µF capacitor |

| A8  | VDDD         | POWER  | 1.71-V to 5.5-V digital supply                    |

| B1  | P2.3         | GPIO   | Port 2 Pin 3, analog/digital/lcd/csd              |

| B2  | VSSA         | GROUND | Analog ground                                     |

| В3  | P2.7         | GPIO   | Port 2 Pin 7, analog/digital/lcd/csd              |

| B4  | P3.4         | GPIO   | Port 3 Pin 4, analog/digital/lcd/csd              |

| B5  | P3.5         | GPIO   | Port 3 Pin 5, analog/digital/lcd/csd              |

| B6  | P3.6         | GPIO   | Port 3 Pin 6, analog/digital/lcd/csd              |

| B7  | XTAL32I/P6.1 | CLOCK  | 32.768-kHz crystal or external clock input        |

| B8  | XTAL32O/P6.0 | CLOCK  | 32.768-kHz crystal                                |

| C1  | VSSA         | GROUND | Analog ground                                     |

| C2  | P2.2         | GPIO   | Port 2 Pin 2, analog/digital/lcd/csd              |

| C3  | P2.6         | GPIO   | Port 2 Pin 6, analog/digital/lcd/csd              |

| C4  | P3.0         | GPIO   | Port 3 Pin 0, analog/digital/lcd/csd              |

Document Number: 001-90478 Rev. \*L Page 9 of 42

Table 2. CYBL10X6X Pin List (WLCSP Package) (continued)

| Pin | Name    | Туре   | Description                                                |

|-----|---------|--------|------------------------------------------------------------|

| C5  | P3.1    | GPIO   | Port 3 Pin 1, analog/digital/lcd/csd                       |

| C6  | P3.2    | GPIO   | Port 3 Pin 2, analog/digital/lcd/csd                       |

| C7  | XRES    | RESET  | Reset, active LOW                                          |

| C8  | P4.0    | GPIO   | Port 4 Pin 0, analog/digital/lcd/csd                       |

| D1  | P1.7    | GPIO   | Port 1 Pin 7, analog/digital/lcd/csd                       |

| D2  | VDDA    | POWER  | 1.71-V to 5.5-V analog supply                              |

| D3  | P2.0    | GPIO   | Port 2 Pin 0, analog/digital/lcd/csd                       |

| D4  | P2.1    | GPIO   | Port 2 Pin 1, analog/digital/lcd/csd                       |

| D5  | P2.5    | GPIO   | Port 2 Pin 5, analog/digital/lcd/csd                       |

| D6  | VSSD    | GROUND | Digital ground                                             |

| D7  | P4.1    | GPIO   | Port 4 Pin 1, analog/digital/lcd/csd                       |

| D8  | P5.0    | GPIO   | Port 5 Pin 0, analog/digital/lcd/csd, overvoltage-tolerant |

| E1  | P1.2    | GPIO   | Port 1 Pin 2, analog/digital/lcd/csd                       |

| E2  | P1.3    | GPIO   | Port 1 Pin 3, analog/digital/lcd/csd                       |

| E3  | P1.4    | GPIO   | Port 1 Pin 4, analog/digital/lcd/csd                       |

| E4  | P1.5    | GPIO   | Port 1 Pin 5, analog/digital/lcd/csd                       |

| E5  | P1.6    | GPIO   | Port 1 Pin 6, analog/digital/lcd/csd                       |

| E6  | P2.4    | GPIO   | Port 2 Pin 4, analog/digital/lcd/csd                       |

| E7  | P5.1    | GPIO   | Port 5 Pin 1, analog/digital/lcd/csd, overvoltage-tolerant |

| E8  | VSSD    | GROUND | Digital ground                                             |

| F1  | VSSD    | GROUND | Digital ground                                             |

| F2  | P0.7    | GPIO   | Port 0 Pin 7, analog/digital/lcd/csd                       |

| F3  | P0.3    | GPIO   | Port 0 Pin 3, analog/digital/lcd/csd                       |

| F4  | P1.0    | GPIO   | Port 1 Pin 0, analog/digital/lcd/csd                       |

| F5  | P1.1    | GPIO   | Port 1 Pin 1, analog/digital/lcd/csd                       |

| F6  | VSSR    | GROUND | Radio ground                                               |

| F7  | VSSR    | GROUND | Radio ground                                               |

| F8  | VDDR    | POWER  | 1.9-V to 5.5-V radio supply                                |

| G1  | P0.6    | GPIO   | Port 0 Pin 6, analog/digital/lcd/csd                       |

| G2  | VDDD    | POWER  | 1.71-V to 5.5-V digital supply                             |

| G3  | P0.2    | GPIO   | Port 0 Pin 2, analog/digital/lcd/csd                       |

| G4  | VSSD    | GROUND | Digital ground                                             |

| G5  | VSSR    | GROUND | Radio ground                                               |

| G6  | VSSR    | GROUND | Radio ground                                               |

| G7  | GANT    | GROUND | Antenna shielding ground                                   |

| G8  | VSSR    | GROUND | Radio ground                                               |

| H1  | P0.5    | GPIO   | Port 0 Pin 5, analog/digital/lcd/csd                       |

| H2  | P0.1    | GPIO   | Port 0 Pin 1, analog/digital/lcd/csd                       |

| H3  | XTAL24O | CLOCK  | 24-MHz crystal                                             |

| H4  | XTAL24I | CLOCK  | 24-MHz crystal or external clock input                     |

Table 2. CYBL10X6X Pin List (WLCSP Package) (continued)

| Pin | Name       | Туре    | Description                          |

|-----|------------|---------|--------------------------------------|

| H5  | VSSR       | GROUND  | Radio ground                         |

| H6  | VSSR       | GROUND  | Radio ground                         |

| H7  | ANT        | ANTENNA | Antenna pin                          |

| J1  | P0.4       | GPIO    | Port 0 Pin 4, analog/digital/lcd/csd |

| J2  | P0.0       | GPIO    | Port 0 Pin 0, analog/digital/lcd/csd |

| J3  | VDDR       | POWER   | 1.9-V to 5.5-V radio supply          |

| J6  | VDDR       | POWER   | 1.9-V to 5.5-V radio supply          |

| J7  | NO CONNECT | -       |                                      |

The I/O subsystem consists of a high-speed I/O matrix (HSIOM), which is a group of high-speed switches that routes GPIOs to the resources inside the device. These resources include CapSense, TCPWMs, I<sup>2</sup>C, SPI, UART, and LCD. HSIOM\_PORT\_SELx are Jur.

Jie 3. 32-bit-wide registers that control the routing of GPIOs. Each register controls one port; four dedicated bits are assigned to each GPIO in the port. This provides up to 16 different options for GPIO routing as shown in Table 3.

**Table 3. HSIOM Port Settings**

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Firmware-controlled GPIO            |

| 1     | Reserved                            |

| 2     | Reserved                            |

| 3     | Reserved                            |

| 4     | Pin is a CSD sense pin              |

| 5     | Pin is a CSD shield pin             |

| 6     | Pin is connected to AMUXA           |

| 7     | Pin is connected to AMUXB           |

| 8     | Pin-specific Active function #0     |

| 9     | Pin-specific Active function #1     |

| 10    | Pin-specific Active function #2     |

| 11    | Reserved                            |

| 12    | Pin is an LCD common pin            |

| 13    | Pin is an LCD segment pin           |

| 14    | Pin-specific Deep-Sleep function #0 |

| 15    | Pin-specific Deep-Sleep function #1 |

The selection of peripheral functions for different GPIO pins is given in Table 4.

Table 4. Port Pin Connections<sup>[1]</sup>

| <b>*</b> |        |      | Digital (HSIOM_PORT_SELx.SELy) ('x' denotes port number and 'y' denotes pin number) |                  |           |                 |                   |  |  |

|----------|--------|------|-------------------------------------------------------------------------------------|------------------|-----------|-----------------|-------------------|--|--|

| Name     | Analog | 0    | 8                                                                                   | 9                | 10        | 14              | 15                |  |  |

|          |        | GPIO | Active #0                                                                           | Active #1        | Active #2 | Deep Sleep #0   | Deep Sleep #1     |  |  |

| P0.0     |        | GPIO | TCPWM0_P[3]                                                                         | SCB1_UART_RX[1]  |           | SCB1_I2C_SDA[1] | SCB1_SPI_MOSI[1]  |  |  |

| P0.1     |        | GPIO | TCPWM0_N[3]                                                                         | SCB1_UART_TX[1]  |           | SCB1_I2C_SCL[1] | SCB1_SPI_MISO[1]  |  |  |

| P0.2     |        | GPIO | TCPWM1_P[3]                                                                         | SCB1_UART_RTS[1] |           |                 | 'SCB1_SPI_SS0[1]' |  |  |

| P0.3     |        | GPIO | TCPWM1_N[3]                                                                         | SCB1_UART_CTS[1] |           |                 | SCB1_SPI_SCLK[1]  |  |  |

#### Note

<sup>1.</sup> For devices with only 1 SCB, use pins corresponding to SCB1.

Table 4. Port Pin Connections<sup>[1]</sup> (continued)

|             |          |      | Digital (HSIOM_PORT_SELx.SELy) ('x' denotes port number and 'y' denotes pi |                                              |                           |                 |                  |  |

|-------------|----------|------|----------------------------------------------------------------------------|----------------------------------------------|---------------------------|-----------------|------------------|--|

| Name        | Analog   | 0    | 8                                                                          | 8 9 10                                       |                           |                 | 15               |  |

|             |          | GPIO | Active #0                                                                  | Active #1                                    | Active #2                 | Deep Sleep #0   | Deep Sleep #1    |  |

| P0.4        |          | GPIO | TCPWM1_P[0]                                                                | SCB0_UART_RX[1]                              | EXT_CLK[0]/<br>ECO_OUT[0] | SCB0_I2C_SDA[1] | SCB0_SPI_MOSI[1] |  |

| P0.5        |          | GPIO | TCPWM1_N[0]                                                                | SCB0_UART_TX[1]                              |                           | SCB0_I2C_SCL[1] | SCB0_SPI_MISO[1] |  |

| P0.6        |          | GPIO | TCPWM2_P[0]                                                                | SCB0_UART_RTS[1]                             |                           | SWDIO[0]        | SCB0_SPI_SS0[1]  |  |

| P0.7        |          | GPIO | TCPWM2_N[0]                                                                | SCB0_UART_CTS[1]                             |                           | SWDCLK[0]       | SCB0_SPI_SCLK[1] |  |

| P1.0        |          | GPIO | TCPWM0_P[1]                                                                |                                              |                           |                 | WCO_OUT[2]       |  |

| P1.1        |          | GPIO | TCPWM0_N[1]                                                                |                                              |                           |                 | SCB1_SPI_SS1     |  |

| P1.2        |          | GPIO | TCPWM1_P[1]                                                                |                                              |                           | N               | SCB1_SPI_SS2     |  |

| P1.3        |          | GPIO | TCPWM1_N[1]                                                                |                                              |                           |                 | SCB1_SPI_SS3     |  |

| P1.4        |          | GPIO | TCPWM2_P[1]                                                                | SCB0_UART_RX[0]                              |                           | SCB0_I2C_SDA[0] | SCB0_SPI_MOSI[1] |  |

| P1.5        |          | GPIO | TCPWM2_N[1]                                                                | SCB0_UART_TX[0]                              | 13                        | SCB0_I2C_SCL[0] | SCB0_SPI_MISO[1] |  |

| P1.6        |          | GPIO | TCPWM3_P[1]                                                                | SCB0_UART_RTS[0]                             |                           |                 | SCB0_SPI_SS0[1]  |  |

| P1.7        |          | GPIO | TCPWM3_N[1]                                                                | SCB0_UART_CTS[0]                             |                           |                 | SCB0_SPI_SCLK[1] |  |

| P2.0        |          | GPIO |                                                                            |                                              |                           |                 | SCB0_SPI_SS1     |  |

| P2.1        |          | GPIO |                                                                            | <b>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</b> |                           |                 | SCB0_SPI_SS2     |  |

| P2.2        |          | GPIO |                                                                            |                                              |                           | WAKEUP          | SCB0_SPI_SS3     |  |

| P2.3        |          | GPIO |                                                                            | 70                                           |                           |                 | WCO_OUT[1]       |  |

| P2.4        |          | GPIO |                                                                            | 70                                           |                           |                 |                  |  |

| P2.5        |          | GPIO |                                                                            |                                              |                           |                 |                  |  |

| P2.6        |          | GPIO | 0                                                                          |                                              |                           |                 |                  |  |

| P2.7        |          | GPIO |                                                                            |                                              | EXT_CLK[1]/<br>ECO_OUT[1] |                 |                  |  |

| P3.0        | SARMUX_0 | GPIO | TCPWM0_P[2]                                                                | SCB0_UART_RX[2]                              |                           | SCB0_I2C_SDA[2] |                  |  |

| P3.1        | SARMUX_1 | GPIO | TCPWM0_N[2]                                                                | SCB0_UART_TX[2]                              |                           | SCB0_I2C_SCL[2] |                  |  |

| P3.2        | SARMUX_2 | GPIO | TCPWM1_P[2]                                                                | SCB0_UART_RTS[2]                             |                           |                 |                  |  |

| P3.3        | SARMUX_3 | GPIO | TCPWM1_N[2]                                                                | SCB0_UART_CTS[2]                             |                           |                 |                  |  |

| P3.4        | SARMUX_4 | GPIO | TCPWM2_P[2]                                                                | SCB1_UART_RX[2]                              |                           | SCB1_I2C_SDA[2] |                  |  |

| P3.5        | SARMUX_5 | GPIO | TCPWM2_N[2]                                                                | SCB1_UART_TX[2]                              |                           | SCB1_I2C_SCL[2] |                  |  |

| P3.6        | SARMUX_6 | GPIO | TCPWM3_P[2]                                                                | SCB1_UART_RTS[2]                             |                           |                 |                  |  |

| P3.7        | SARMUX_7 | GPIO | TCPWM3_N[2]                                                                | SCB1_UART_CTS[2]                             |                           |                 | WCO_OUT[0]       |  |

| P4.0        | CMOD     | GPIO | TCPWM0_P[0]                                                                | SCB1_UART_RTS[0]                             |                           |                 | SCB1_SPI_MOSI[0] |  |

| P4.1        | CTANK    | GPIO | TCPWM0_N[0]                                                                | SCB1_UART_CTS[0]                             |                           |                 | SCB1_SPI_MISO[0] |  |

| P5.0        |          | GPIO | TCPWM3_P[0]                                                                | SCB1_UART_RX[0]                              | EXTPA_EN                  | SCB1_I2C_SDA[0] | SCB1_SPI_SS0[0]  |  |

| P5.1        |          | GPIO | TCPWM3_N[0]                                                                | SCB1_UART_TX[0]                              | EXT_CLK[2]/<br>ECO_OUT[2] | SCB1_I2C_SCL[0] | SCB1_SPI_SCLK[0] |  |

| 0.0_XTAL32O |          | GPIO |                                                                            |                                              |                           |                 |                  |  |

| 6.1_XTAL32I |          | GPIO |                                                                            |                                              |                           |                 |                  |  |

#### **Power**

PRoC BLE can be supplied from batteries with a voltage range of 1.9 V to 5.5 V by directly connecting to the digital supply  $(V_{DDD})$ , analog supply  $(V_{DDA})$ , and radio supply  $(V_{DDR})$  pins. The internal LDOs in the device regulate the supply voltage to required levels for different blocks. The device has one regulator for the digital circuitry and separate regulators for radio circuitry for noise isolation. The analog circuits run directly from the analog supply ( $V_{DDA}$ ) input. The device uses separate regulators for Deep Sleep and Hibernate modes to minimize the power consumption. The radio stops working below 1.9 V, but the rest of the system continues to function down to 1.71 V without RF. Note that  $V_{DDR}$  must be supplied whenever  $V_{DDD}$  is supplied.

Bypass capacitors must be used from VDDx (x = A, D, or R) to ground. The typical practice for systems in this frequency range is to use a capacitor in the 1-µF range in parallel with a smaller capacitor (for example, 0.1 µF). Note that these are simply rules of thumb and that, for critical applications, the PCB layout, lead inductance, and the bypass capacitor parasitic should be simulated to design to obtain optimal bypassing.

| Power Supply                | Bypass Capacitors                                                   |

|-----------------------------|---------------------------------------------------------------------|

| V <sub>DDD</sub>            | 0.1-μF ceramic at each pin plus bulk capacitor 1 μF to 10 μF        |

| V <sub>DDA</sub>            | 0.1-μF ceramic at each pin plus bulk capacitor 1 μF to 10 μF        |

| V <sub>DDR</sub>            | 0.1-μF ceramic at each pin plus bulk capacitor 1 μF to 10 μF        |

| V <sub>CCD</sub>            | 1-μF ceramic capacitor at the VCCD pin                              |

| V <sub>REF</sub> (optional) | The internal bandgap may be bypassed with a 1-µF to 10-µF capacitor |

#### **Low-Power Modes**

PRoC BLE supports five power modes. Refer to Table 5 for more details on the system status. The PRoC BLE device consumes the lowest current in Stop mode; the device wakeup from stop mode is with a system reset through the XRES or WAKEUP pin. It can retain the SRAM data in Hibernate mode and is capable of retaining the complete system status in Deep-Sleep mode. Table 5 shows the different power modes and the peripherals that are active.

Table 5. Power Modes System Status

| Power Mode | Current<br>Consumption                    | Code<br>Execution | Digital<br>Peripherals<br>Available              | Analog<br>Peripherals<br>Available | Clock<br>Sources<br>Available | Wake Up<br>Sources                               | Wake-Up<br>Time |

|------------|-------------------------------------------|-------------------|--------------------------------------------------|------------------------------------|-------------------------------|--------------------------------------------------|-----------------|

| Active     | 850 μA + 260 μA<br>per MHz <sup>[2]</sup> | Yes               | All                                              | All                                | All                           | _                                                | -               |

| Sleep      | 1.1 mA at 3 MHz                           | No                | All                                              | All                                | All                           | Any interrupt source                             | 0               |

| Deep Sleep | 1.3 μΑ                                    | No                | WDT, LCD,<br>I <sup>2</sup> C/SPI,<br>Link-Layer | POR, BOD                           | WCO,<br>ILO                   | GPIO, WDT,<br>I <sup>2</sup> C/SPI Link<br>Layer | 25 μs           |

| Hibernate  | 150 nA                                    | No                | No                                               | POR, BOD                           | No                            | GPIO                                             | 2 ms            |

| Stop       | 60 nA                                     | No                | No                                               | No                                 | No                            | Wake-Up pin,<br>XRES                             | 2 ms            |

| Not        | 500                                       |                   |                                                  |                                    |                               |                                                  |                 |

2. For CPU subsystem.

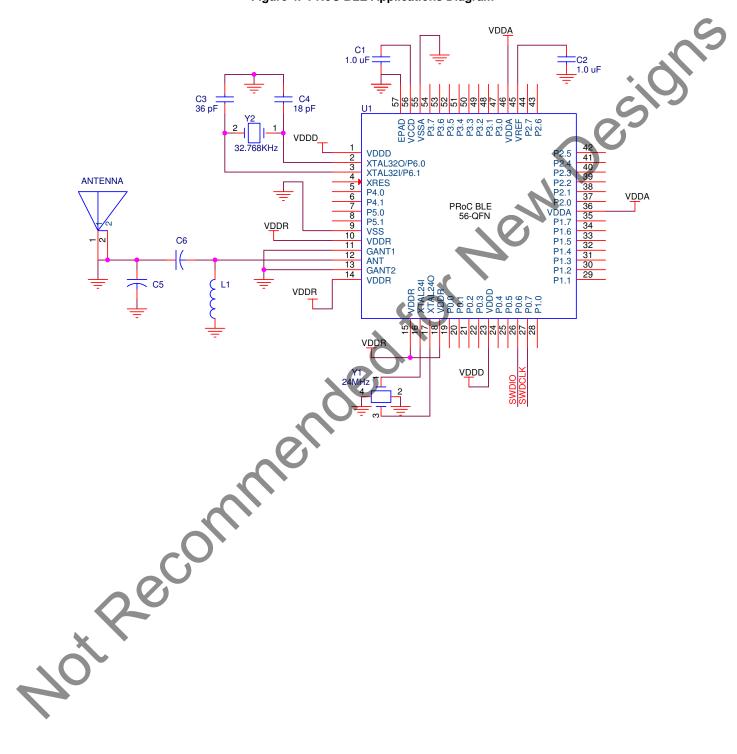

A typical system application connection diagram for the 56-QFN package is shown in Figure 4.

Figure 4. PRoC BLE Applications Diagram

## **Development Support**

The CYBL10X6X family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit www.cypress.com/procble to find out more.

#### **Documentation**

A suite of documentation supports the CYBL10X6X family to ensure that you find answers to your questions quickly. This section contains a list of some of the key documents.

Component Datasheets: PSoC Creator Components provide hardware abstraction using APIs to configure and control peripheral activity. The Component datasheet covers Component features, its usage and operation details, API description, and electrical specifications. This is the primary documentation used during development. These Components can represent peripherals on the device (such as a timer, I<sup>2</sup>C, or UART) or high-level system functions (such as the BLE Component).

Application Notes: Application notes help you to understand how to use various device features. They also provide guidance on how to solve a variety of system design challenges.

**Technical Reference Manual (TRM):** The TRM describes all peripheral functionality in detail, with register-level descriptions. This document is divided into two parts: the Architecture TRM and the Register TRM.

#### Online

In addition to the print documentation, Cypress forums connect you with fellow users and experts from around the world, 24 hours a day, 7 days a week.

#### Tools

With industry-standard cores, programming, and debugging interfaces, the CYBL10X6X family is part of a development tool ecosystem.

Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy-to-use PSoC Creator IDE, supported third-party compilers, programmers, and debuggers.

#### Kits

Cypress provides a portfolio of kits to accelerate time-to-market. Visit us at www.cypress.com/procble.

# **Electrical Specifications**

This section provides detailed electrical characteristics. Absolute maximum rating for the CYBL10X6X devices is listed in the following table. Usage above the absolute maximum conditions may cause permanent damage to the device.

Exposure to absolute maximum conditions for extended periods of time may affect device reliability.

The maximum storage temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below absolute maximum conditions, but above normal operating conditions, the device may not operate to the specification.

### **Absolute Maximum Ratings**

**Table 6. Absolute Maximum Ratings**

| Spec ID# | Parameter                   | Description                                                                            | Min                 | Тур | Max                  | Units | Details/<br>Conditions                       |

|----------|-----------------------------|----------------------------------------------------------------------------------------|---------------------|-----|----------------------|-------|----------------------------------------------|

| SID1     | V <sub>DDD_ABS</sub>        | Analog, digital, or radio supply relative to $V_{SS}$ ( $V_{SSD} = V_{SSA}$ )          | -0.5                | -   | 6                    | V     | Absolute max                                 |

| SID2     | V <sub>CCD_ABS</sub>        | Direct digital core voltage input relative to V <sub>SSD</sub>                         | -0.5                | -   | 1.95                 | V     | Absolute max                                 |

| SID3     | V <sub>GPIO_ABS</sub>       | GPIO voltage                                                                           | -0.5                | -   | V <sub>DD</sub> +0.5 | V     | Absolute max                                 |

| SID4     | I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                               | -25                 | 1   | 25                   | mA    | Absolute max                                 |

| SID5     | I <sub>GPIO_injection</sub> | GPIO injection current, Max for $V_{IH}$ > $V_{DDD}$ , and Min for $V_{IL}$ < $V_{SS}$ | -0.5                | -   | 0.5                  | mA    | Absolute max,<br>current injected per<br>pin |

| BID57    | ESD_HBM                     | Electrostatic discharge human body model                                               | 2200 <sup>[3]</sup> | -   | _                    | V     |                                              |

| BID58    | ESD_CDM                     | Electrostatic discharge charged device model                                           | 500                 | _   | -                    | V     |                                              |

| BID61    | LU                          | Pin current for latch up                                                               | -200                | _   | 200                  | mA    |                                              |

### **BLE Subsystem**

Table 7. BLE Subsystem

| Spec ID#   | Parameter      | Description                                                                               | Min | Тур             | Max | Units | Details/<br>Conditions                |

|------------|----------------|-------------------------------------------------------------------------------------------|-----|-----------------|-----|-------|---------------------------------------|

| RF Receive | Specifications | 7/                                                                                        |     |                 |     |       |                                       |

| SID340     | RXS, IDLE      | RX sensitivity with idle transmitter                                                      | _   | -89             | _   | dBm   |                                       |

| SID340A    | RXS, IDLE      | RX sensitivity with idle transmitter excluding balun loss                                 | _   | <b>-</b> 91     | _   | dBm   | Guaranteed by design simulation       |

| SID341     | RXS, DIRTY     | RX sensitivity with dirty transmitter                                                     | _   | <del>-</del> 87 | _   | dBm   | RF-PHY Specification (RCV-LE/CA/01/C) |

| SID342     | RXS, HIGHGAIN  | RX sensitivity in high-gain mode with idle transmitter                                    | _   | <b>-</b> 91     | _   | dBm   |                                       |

| SID343     | PRXMAX         | Maximum input power                                                                       | -10 | -1              | _   | dBm   | RF-PHY Specification (RCV-LE/CA/06/C) |

| SID344     | CI1            | Co-channel interference,<br>Wanted signal at –67 dBm and<br>Interferer at F <sub>RX</sub> | _   | 9               | 21  | dB    | RF-PHY Specification (RCV-LE/CA/03/C) |

#### Note

<sup>3.</sup> This does not apply to the RF pins (ANT, XTALI, and XTALO). RF pins (ANT, XTALI, and XTALO) are tested for 500-V HBM.

Table 7. BLE Subsystem (continued)

| Spec ID#  | Parameter          | Description                                                                                                                    | Min        | Тур | Max             | Units | Details/<br>Conditions                                          |

|-----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----------------|-------|-----------------------------------------------------------------|

| SID345    | CI2                | Adjacent channel interference<br>Wanted signal at –67 dBm and<br>Interferer at FRX ±1 MHz                                      | -          | 3   | 15              | dB    | RF-PHY Specification<br>(RCV-LE/CA/03/C)                        |

| SID346    | CI3                | Adjacent channel interference<br>Wanted signal at –67 dBm and<br>Interferer at F <sub>RX</sub> ±2 MHz                          | _          | -29 | _               | dB    | RF-PHY Specification (RCV-LE/CA/03/C)                           |

| SID347    | CI4                | Adjacent channel interference<br>Wanted signal at –67 dBm and<br>Interferer at ≥F <sub>RX</sub> ±3 MHz                         | _          | -39 | _               | dB    | RF-PHY Specification<br>(RCV-LE/CA/03/C)                        |

| SID348    | CI5                | Adjacent channel interference<br>Wanted Signal at –67 dBm and<br>Interferer at Image frequency<br>(F <sub>IMAGE</sub> )        | _          | -20 | -               | dB    | RF-PHY Specification<br>(RCV-LE/CA/03/C)                        |

| SID349    | CI3                | Adjacent channel interference<br>Wanted signal at –67 dBm and<br>Interferer at Image frequency<br>(F <sub>IMAGE</sub> ± 1 MHz) | _          | -30 | 10              | dB    | RF-PHY Specification (RCV-LE/CA/03/C)                           |

| SID350    | OBB1               | Out-of-band blocking,<br>Wanted signal at –67 dBm and<br>Interferer at F = 30–2000 MHz                                         | -30        | -27 | _               | dBm   | RF-PHY Specification<br>(RCV-LE/CA/04/C)                        |

| SID351    | OBB2               | Out-of-band blocking,<br>Wanted signal at –67 dBm and<br>Interferer at F = 2,003–2,399 MHz                                     | -35        | -27 | -               | dBm   | RF-PHY Specification<br>(RCV-LE/CA/04/C)                        |

| SID352    | OBB3               | Out-of-band blocking,<br>Wanted signal at –67 dBm and<br>Interferer at F = 2,484–2,997 MHz                                     | -35        | -27 | -               | dBm   | RF-PHY Specification<br>(RCV-LE/CA/04/C)                        |

| SID353    | OBB4               | Out-of-band blocking,<br>Wanted signal a –67 dBm and Inter-<br>ferer at F = 3,000–12,750 MHz                                   | -30        | -27 | -               | dBm   | RF-PHY Specification (RCV-LE/CA/04/C)                           |

| SID354    | IMD                | Intermodulation performance<br>Wanted signal at –64 dBm and<br>1-Mbps BLE, third, fourth, and fifth<br>offset channel          | <b>-50</b> | _   | -               | dBm   | RF-PHY Specification (RCV-LE/CA/05/C)                           |

| SID355    | RXSE1              | Receiver spurious emission<br>30 MHz to 1.0 GHz                                                                                | _          | -   | <b>–</b> 57     | dBm   | 100-kHz<br>measurement<br>bandwidth<br>ETSI EN300 328<br>V1.8.1 |

| SID356    | RXSE2              | Receiver spurious emission<br>1.0 GHz to 12.75 GHz                                                                             | _          | _   | <del>-4</del> 7 | dBm   | 1-MHz measurement<br>bandwidth<br>ETSI EN300 328<br>V1.8.1      |

| RF Transm | tter Specification |                                                                                                                                |            |     |                 |       |                                                                 |

| SID357    | TXP, ACC           | RF power accuracy                                                                                                              | _          | ±1  | _               | dB    |                                                                 |

| SID358    | TXP, RANGE         | RF power control range                                                                                                         | -          | 20  | _               | dB    |                                                                 |

| SID359    | TXP, 0 dBm         | Output power, 0-dB gain setting (PA7)                                                                                          | _          | 0   | _               | dBm   |                                                                 |

Table 7. BLE Subsystem (continued)

| Spec ID#     | Parameter       | Description                                         | Min  | Тур  | Max               | Units         | Details/<br>Conditions                                                                  |

|--------------|-----------------|-----------------------------------------------------|------|------|-------------------|---------------|-----------------------------------------------------------------------------------------|

| SID360       | TXP, MAX        | Output power, maximum power setting (PA10)          | -    | 3    | _                 | dBm           | 200                                                                                     |

| SID361       | TXP, MIN        | Output power, minimum power setting (PA1)           | _    | -18  | _                 | dBm           |                                                                                         |

| SID362       | F2AVG           | Average frequency deviation for 10101010 pattern    | 185  | _    | -                 | kHz           | RF-PHY Specification (TRM-LE/CA/05/C)                                                   |

| SID363       | F1AVG           | Average frequency deviation for 11110000 pattern    | 225  | 250  | 275               | kHz           | RF-PHY Specification (TRM-LE/CA/05/C)                                                   |

| SID364       | EO              | Eye opening = ΔF2AVG/ΔF1AVG                         | 0.8  | _    | -                 |               | RF-PHY Specification (TRM-LE/CA/05/C)                                                   |

| SID365       | FTX, ACC        | Frequency accuracy                                  | -150 | _    | 150               | kHz           | RF-PHY Specification (TRM-LE/CA/06/C)                                                   |

| SID366       | FTX, MAXDR      | Maximum frequency drift                             | -50  | -    | 50                | kHz           | RF-PHY Specification (TRM-LE/CA/06/C)                                                   |

| SID367       | FTX, INITDR     | Initial frequency drift                             | -20  | 1    | 20                | kHz           | RF-PHY Specification (TRM-LE/CA/06/C)                                                   |

| SID368       | FTX,DR          | Maximum drift rate                                  | -20  | -    | 20                | kHz/<br>50 µs | RF-PHY Specification (TRM-LE/CA/06/C)                                                   |

| SID369       | IBSE1           | In-band spurious emission at 2-MHz offset           | X-F  | -    | -20               | dBm           | RF-PHY Specification (TRM-LE/CA/03/C)                                                   |

| SID370       | IBSE2           | In-band spurious emission at ≥3-MHz offset          | _    | _    | -30               | dBm           | RF-PHY Specification (TRM-LE/CA/03/C)                                                   |

| SID371       | TXSE1           | Transmitter spurious emissions (average), <1.0 GHz  | _    | _    | -55.5             | dBm           | FCC-15.247                                                                              |

| SID372       | TXSE2           | Transmitter spurious emissions (average), >1.0 GHz  | _    | _    | <del>-4</del> 1.5 | dBm           | FCC-15.247                                                                              |

| RF Current S | Specification   |                                                     |      | •    |                   | •             |                                                                                         |

| SID373       | IRX             | Receive current in normal mode                      | _    | 18.7 | -                 | mA            |                                                                                         |

| SID373A      | IRX_RF          | Receive current in normal mode                      | _    | 16.4 | _                 | mA            | Measured at V <sub>DDR</sub>                                                            |

| SID374       | IRX, HIGHGAIN   | Receive current in high-gain mode                   | _    | 21.5 | _                 | mA            |                                                                                         |

| SID375       | ITX, 3 dBm      | TX current at 3-dBm setting (PA10)                  | _    | 20   | _                 | mA            |                                                                                         |

| SID376       | ITX, 0 dBm      | TX current at 0-dBm setting (PA7)                   | _    | 16.5 | _                 | mA            |                                                                                         |

| SID376A      | ITX_RF, 0 dBm   | TX current at 0-dBm setting (PA7)                   | -    | 15.6 | _                 | mA            | Measured at V <sub>DDR</sub>                                                            |

| SID376B      | ITX_RF, 0 dBm   | TX current at 0 dBm excluding Balun loss            | _    | 14.2 | -                 | mA            | Guaranteed by design simulation                                                         |

| SID377       | ITX, -3 dBm     | TX current at -3-dBm setting (PA4)                  | -    | 15.5 | -                 | mA            |                                                                                         |

| SID378       | ≢TX, -6 dBm     | TX current at –6-dBm setting (PA3)                  | _    | 14.5 | _                 | mA            |                                                                                         |

| SID379       | ITX, -12 dBm    | TX current at –12-dBm setting (PA2)                 | _    | 13.2 | _                 | mA            |                                                                                         |

| SID380       | ITX, -18 dBm    | TX current at –18-dBm setting (PA1)                 | _    | 12.5 | _                 | mA            |                                                                                         |

| SID380A      | lavg_1sec, 0dBm | Average current at 1-second BLE connection interval | _    | 18.9 | -                 | μА            | TXP: 0 dBm; ±20-ppm<br>master and slave<br>clock accuracy.<br>For empty PDU<br>exchange |

Table 7. BLE Subsystem (continued)

| Spec ID#      | Parameter       | Description                                         | Min  | Тур  | Max  | Units | Details/<br>Conditions                                                                 |

|---------------|-----------------|-----------------------------------------------------|------|------|------|-------|----------------------------------------------------------------------------------------|

| SID380B       | lavg_4sec, 0dBm | Average current at 4-second BLE connection interval | -    | 6.25 | ı    | μA    | TXP: 0 dBm; ±20-ppm<br>master and slave<br>clock accuracy<br>For empty PDU<br>exchange |

| General RF S  | Specification   |                                                     |      |      |      |       | C                                                                                      |

| SID381        | FREQ            | RF operating frequency                              | 2400 | _    | 2482 | MHz   | 2,5                                                                                    |

| SID382        | CHBW            | Channel spacing                                     | _    | 2    | -    | MHz   | 0                                                                                      |

| SID383        | DR              | On-air data rate                                    | _    | 1000 | -    | kbps  |                                                                                        |

| SID384        | IDLE2TX         | BLE Radio Idle to BLE Radio TX transition time      | -    | 120  | 140  | μs    |                                                                                        |

| SID385        | IDLE2RX         | BLE Radio Idle to BLE Radio RX transition time      | -    | 75   | 120  | μs    |                                                                                        |

| RSSI Specific | cation          |                                                     |      | 1    | 7    |       |                                                                                        |

| SID386        | RSSI, ACC       | RSSI accuracy                                       | -    | ±5   | _    | dB    |                                                                                        |

| SID387        | RSSI, RES       | RSSI resolution                                     | 4.0  | 1    | _    | dB    |                                                                                        |

| SID388        | RSSI, PER       | RSSI sample period                                  | *    | 6    | _    | μs    |                                                                                        |

# **Device-Level Specifications**

All specifications are valid for  $-40~^{\circ}\text{C} \le \text{TA} \le 105~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

**Table 8. DC Specifications**

| Spec ID#    | Parameter                      | Description                                                                                     | Min  | Тур | Max  | Units | Details/<br>Conditions                |

|-------------|--------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|-------|---------------------------------------|

| SID6        | $V_{DD}$                       | Power supply input voltage (V <sub>DDA</sub> = V <sub>DDD</sub> = V <sub>DD</sub> )             | 1.8  | _   | 5.5  | V     | With regulator enabled                |

| SID7        | $V_{DD}$                       | Power supply input voltage unregulated (V <sub>DDA</sub> = V <sub>DDD</sub> = V <sub>DD</sub> ) | 1.71 | 1.8 | 1.89 | V     | Internally unregulated supply         |

| SID8        | $V_{DDR}$                      | Radio supply voltage (Radio on)                                                                 | 1.9  | -   | 5.5  | V     |                                       |

| SID8A       | $V_{DDR}$                      | Radio supply voltage (Radio off)                                                                | 1.71 | _   | 5.5  | V     |                                       |