#### MAX22513

## Surge Protected Dual Driver IO-Link Device Transceiver with DC-DC

#### **General Description**

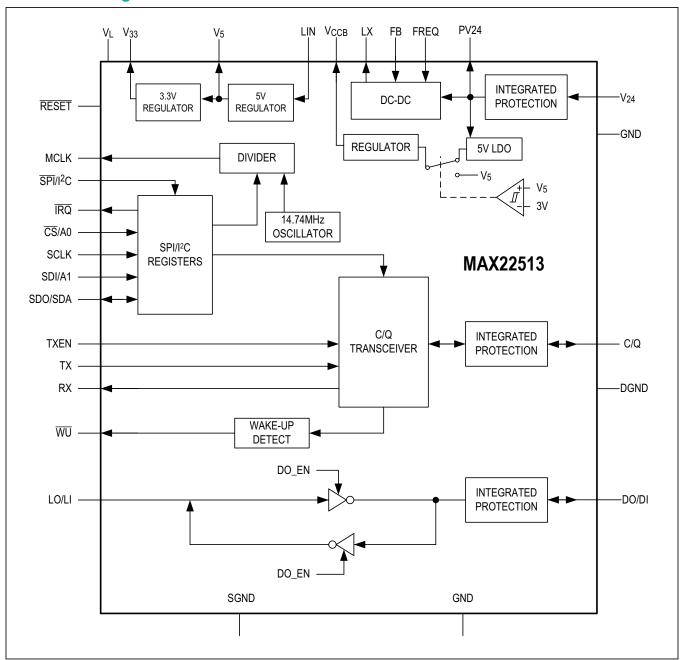

The MAX22513 dual-channel low power IO-Link device transceiver features a selectable control interface, internal high-efficiency DC-DC buck regulator, two internal linear regulators, and integrated surge protection for robust communication. The device features low-on resistance drivers (C/Q and DO/DI), selectable driver current limits, and overcurrent protection to reduce power dissipation in small sensor applications.

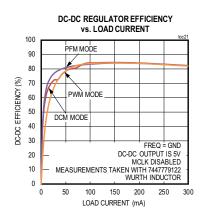

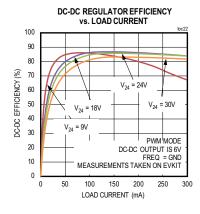

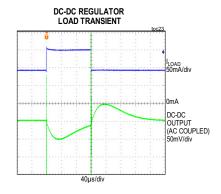

The DC-DC buck regulator supplies up to 300mA load current and has an adjustable output voltage (from 2.5V to 12V). Internal linear regulators generate 5V and 3.3V, supplying up to 50mA of current.

The MAX22513 can be controlled using SPI or I<sup>2</sup>C interfaces, providing flexibility for microcontrollers, and extensive control and diagnostic features. Both full-and half-duplex SPI are supported. The internal MCLK oscillator provides a clock source to a microcontroller for IO-Link communication.

The MAX22513 features extensive integrated protection to ensure robust communication in harsh industrial environments. All four IO pins ( $V_{24}$ , C/Q, DO/DI, and GND), are reverse voltage protected, short circuit protected, and feature integrated  $\pm 1 kV/500\Omega$  surge protection.

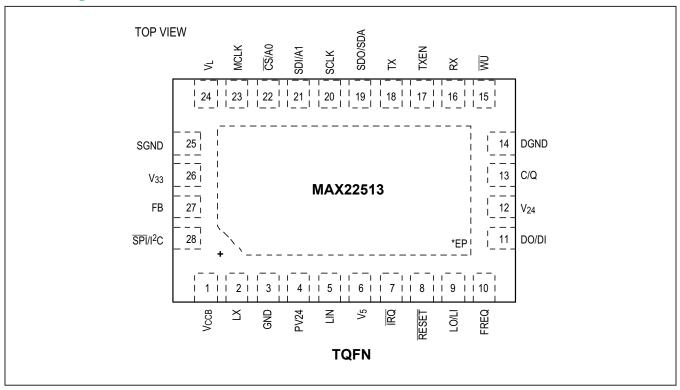

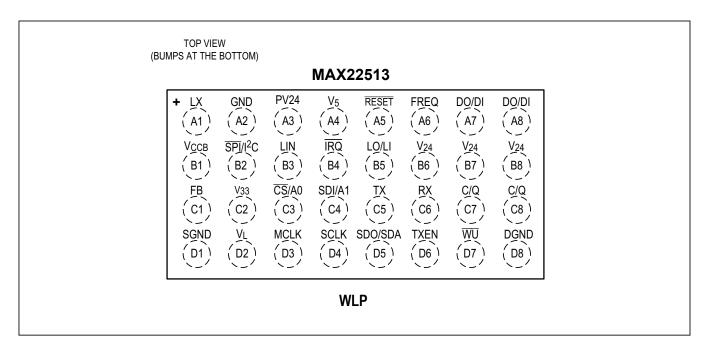

The MAX22513 is available in a tiny WLP package (4.1 mm x 2.1 mm) or 28-pin TQFN-EP package (3.5 mm x 5.5 mm) and operates over the -40°C to +125°C temperature range.

### **Applications**

- IO-Link Sensor and Actuator Devices

- Industrial Sensors

#### **Benefits and Features**

- High Configurability and Integration Reduces SKU

- Configurable C/Q and DO/DI Drivers

- PNP, NPN, and Push-Pull Modes

- · Individual Slew Rate Control for Drivers

- Selectable Driver Current Limit: 50mA to 250mA

- Control and Monitoring with I<sup>2</sup>C or SPI

- Half- and Full-Duplex SPI Modes

- · Integrated High-Efficiency DC-DC Buck Regulator

- Selectable Switching Frequency

- 921kHz (typ) or 1.229MHz (typ)

- 300mA (max) Load

- Output Voltage from 2.5V to 12V

- Internal 5V and 3.3V Linear Regulators

- Accurate Oscillator for IO-Link Communication

- Integrated Protection Enables Robust Systems

- Integrated ±1kV/500Ω Surge Protection

- · Glitch Filters for Improved Burst Resilience

- · Selectable Overcurrent Configuration

- · Hot-Plug and Reverse Polarity Protection

- -40°C to +125°C Operating Temperature Range

- Optimized for Small Sensor Designs

- · Low Power Dissipation:

- 2Ω (typ) On-Resistance for C/Q and DO/DI Drivers

- · Available in Two Tiny Packages:

- 28-Pin TQFN-EP (3.5mm x 5.5mm)

- WLP (4.1mm x 2.1mm)

Ordering Information appears at end of data sheet.

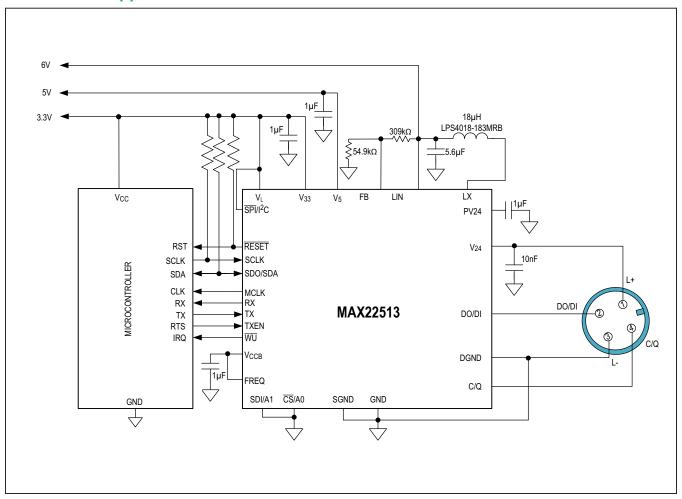

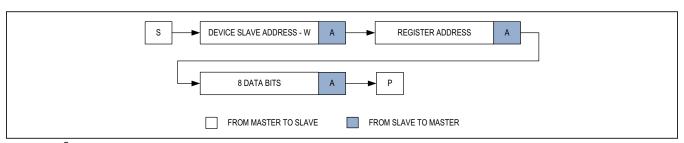

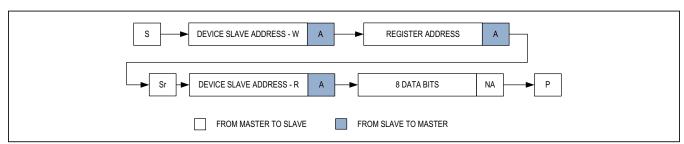

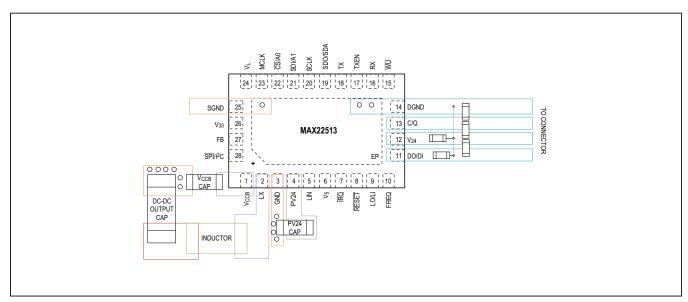

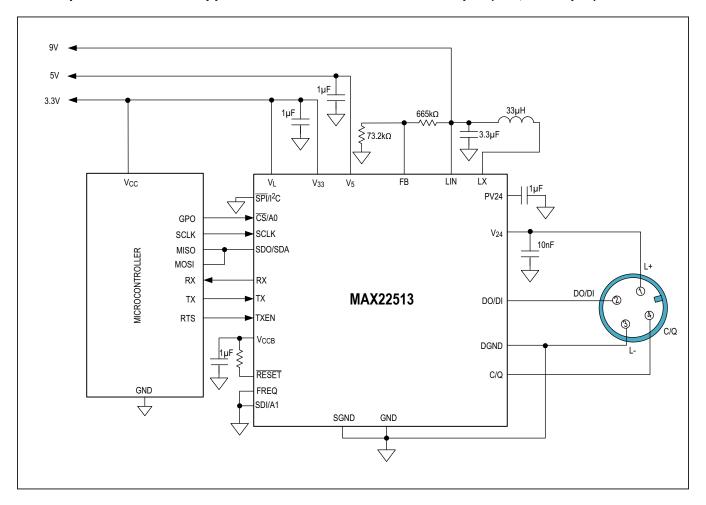

## I<sup>2</sup>C Interface Application Circuit

## **Absolute Maximum Ratings**

| (All voltages referenced to GND unless otherwise noted.)                  | ĪRQ0.3V to +6V                                       |

|---------------------------------------------------------------------------|------------------------------------------------------|

| V <sub>24</sub> (Continuous)36V to +36V                                   | DGND, SGND0.3V to +0.3V                              |

| V <sub>24</sub> (Peak, 100µs)52V to +65V                                  | Continuous Current into V24, LX, GND, or DGND±1A     |

| PV24 (Continuous) (Note 1) max(-0.3V, V <sub>24</sub> - 3V) to +36V       | Continuous Current into PV24±300mA                   |

| PV24 (Peak, 100µs)max(-0.3V, V <sub>24</sub> - 52V)                       | Peak Current into PV24 (100µs)±1A                    |

| to min(+52V, V <sub>24</sub> + 52V)                                       | Continuous Current into C/Q and DO/DI±500mA          |

| LX0.3V to (PV24 + 0.3V)                                                   | Continuous Current into Any Other Pin±50mA           |

| LIN (Continuous) max(-0.3V, V <sub>5</sub> - 0.3V) to +36V                | Continuous Power Dissipation (28-pin TQFN)           |

| LIN (Peak, 100µs)max(-0.3V, V <sub>5</sub> - 0.3V) to +52V                | $(T_A = +70^{\circ}C \text{ (derate at 28.6mW/°C)})$ |

| C/Q, DO/DI (Continuous)max(-36V, V <sub>24</sub> - 36V)                   | above +70°C))2280mW                                  |

| to min(+36V, V <sub>24</sub> + 36V)                                       | Continuous Power Dissipation (30-bump WLP)           |

| C/Q, DO/DI (Peak, 100µs)max(-52V, V <sub>24</sub> - 52V)                  | (T <sub>A</sub> = +70°C (derate at 20.76mW/°C        |

| to min(+52V, V <sub>24</sub> + 52V)                                       | above +70°C))3850mW                                  |

| V <sub>5</sub> , FB, V <sub>CCB</sub> , RESET, FREQ0.3V to +6V            | Operating Temperature Range40°C to +125°C            |

| V <sub>L</sub> 0.3V to +6V                                                | Maximum Junction Temperature+165°C                   |

| V <sub>33</sub> 0.3V to (V <sub>5</sub> + 0.3V)                           | Storage Temperature Range40°C to +150°C              |

| LOGIC INPUTS                                                              | Soldering Temperature (reflow)                       |

| SPĪ/I <sup>2</sup> C, CS/A0, SCLK, SDI/A1,                                | (TQFN only, soldering, 10 sec)+300°C                 |

| SDO/SDA, TX, TXEN, LO/LI0.3V to (V <sub>L</sub> + 0.3V)                   | Bump Reflow Temperature+260°C                        |

| LOGIC OUTPUTS                                                             |                                                      |

| $\overline{WU}$ , SDO/SDA, RX, LO/LI, MCLK0.3V to (V <sub>L</sub> + 0.3V) |                                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: During power-up, (V<sub>24</sub> - PV24) voltage can be up to +52V until the internal active diode turns on.

## **Package Information**

| PACKAGE TYPE: 28 TQFN                  |            |  |  |  |  |  |

|----------------------------------------|------------|--|--|--|--|--|

| Package Code                           | T283555+1C |  |  |  |  |  |

| Outline Number                         | 21-0184    |  |  |  |  |  |

| Land Pattern Number                    | 90-0123    |  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   | ):         |  |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 35°C/W     |  |  |  |  |  |

| Junction to Case $(\theta_{JC})$       | 2.7°C/W    |  |  |  |  |  |

| PACKAGE TYPE: 8 x 4 WLP                            |           |  |  |  |  |

|----------------------------------------------------|-----------|--|--|--|--|

| Package Code                                       | W322A4+1  |  |  |  |  |

| Outline Number                                     | 21-100247 |  |  |  |  |

| Land Pattern Number Refer to Application Note 1891 |           |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:              |           |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )             | 48.16°C/W |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **DC Electrical Characteristics**

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{DGND}=V_{SGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.)$  (Note 2)

| PARAMETER                                                    | SYMBOL                         | CONDITIONS                                                                                                             |                                                                                         | MIN  | TYP   | MAX   | UNITS |

|--------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|-------|-------|-------|

| DC CHARACTERISTICS / PO                                      | WER SUPPLY                     |                                                                                                                        |                                                                                         |      |       |       |       |

| V <sub>24</sub> Supply Voltage                               | V <sub>24</sub>                |                                                                                                                        |                                                                                         | 8    |       | 36    | V     |

| V <sub>24</sub> Undervoltage Lockout                         | V                              | V <sub>24</sub> rising                                                                                                 |                                                                                         | 7.0  | 7.6   | 8     | V     |

| Threshold                                                    | V <sub>24UVLO</sub>            | V <sub>24</sub> falling                                                                                                |                                                                                         | 6.6  | 7.0   | 7.5   | V     |

| V <sub>24</sub> Undervoltage Lockout<br>Threshold Hysteresis | V <sub>24UVLO_HYST</sub>       |                                                                                                                        |                                                                                         |      | 550   |       | mV    |

| V <sub>24</sub> Low Voltage Warning<br>Threshold             | V <sub>24_W</sub>              | V <sub>24</sub> falling                                                                                                |                                                                                         | 14.5 | 16    | 18    | V     |

|                                                              |                                | No load on C/Q or DO/DI,                                                                                               | C/Q and DO/DI<br>disabled                                                               |      | 0.042 | 0.075 |       |

| V <sub>24</sub> Supply Current                               | l <sub>24</sub>                | V <sub>5</sub> powered<br>externally, DC-<br>DC disabled,<br>MCLK disabled                                             | C/Q and DO/DI are in push-pull and are high or low                                      |      | 0.46  | 0.65  | mA    |

|                                                              |                                | DC-DC enabled, MCLK enabled, C/Q and DO/DI in push-pull and are high or low (see <i>Typical Application Circuits</i> ) |                                                                                         |      | 3.75  |       |       |

| V <sub>5</sub> Supply Voltage                                | V <sub>5</sub>                 | V <sub>5</sub> supplied exterr                                                                                         | nally                                                                                   | 4.5  |       | 5.5   | V     |

| V <sub>5</sub> Undervoltage Lockout                          | V <sub>5UVLOR</sub>            | V <sub>5</sub> rising                                                                                                  |                                                                                         | 4.0  |       | 4.25  | V     |

| Threshold                                                    | V <sub>5UVLOF</sub>            | V <sub>5</sub> falling                                                                                                 |                                                                                         | 3.95 |       | 4.25  | V     |

| V. Comple Compart                                            |                                | No load on<br>C/Q or DO/DI,<br>V <sub>5</sub> powered<br>externally, DC-                                               | C/Q and DO/DI<br>disabled                                                               |      | 0.91  | 1.2   |       |

| V <sub>5</sub> Supply Current                                | DC dis MCLK V <sub>33</sub> en | DC disabled,<br>MCLK disabled,<br>V <sub>33</sub> enabled, no<br>load on V <sub>33</sub>                               | C/Q and DO/DI in<br>push-pull mode, no<br>load on C/Q, DO/DI                            |      | 1.89  | 2.4   | mA    |

| V <sub>L</sub> Logic Level Supply Voltage                    | VL                             |                                                                                                                        | •                                                                                       | 2.5  |       | 5.5   | V     |

| V <sub>L</sub> Undervoltage Threshold                        | V <sub>LUVLO</sub>             |                                                                                                                        |                                                                                         | 0.5  | 0.84  | 1.2   | V     |

| V <sub>L</sub> Logic Level Supply Current                    | ΙL                             |                                                                                                                        | All logic inputs at GND or V <sub>L</sub> , no load on any logic outputs, MCLK disabled |      | 15    | 30    | μΑ    |

## **DC Electrical Characteristics (continued)**

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{DGND}=V_{SGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  (Note 2)

| PARAMETER                           | SYMBOL                  | CONDITIONS                                           |                                                         | MIN   | TYP   | MAX   | UNITS               |

|-------------------------------------|-------------------------|------------------------------------------------------|---------------------------------------------------------|-------|-------|-------|---------------------|

| DC CHARACTERISTICS / DC             | DC SWITCHING            | REGULATOR                                            |                                                         |       |       | ,     | 1                   |

| Input Voltage Range                 | V <sub>24_DC</sub>      | V <sub>24</sub> is the input t                       | to the DC-DC                                            | 8     |       | 36    | V                   |

| DC-DC Turn-on Delay                 | t <sub>DC_ON</sub>      |                                                      | crossing V <sub>24UVLO</sub><br>ne DC-DC regulator<br>t |       | 2.22  |       | ms                  |

|                                     | f <sub>DC_H</sub>       | FREQ = high                                          | BUCKSS = 0                                              | 1.198 | 1.223 | 1.260 | MHz                 |

| Switching Frequency                 | f <sub>DC_HSPRD</sub>   | FREQ - High                                          | BUCKSS = 1                                              |       | 1.229 |       | IVITIZ              |

| Switching Frequency                 | f <sub>DC_L</sub>       | FREQ = low                                           | BUCKSS = 0                                              | 898.6 | 921.6 | 944.6 | kHz                 |

|                                     | fDC_LSPRD               | FREQ - IOW                                           | BUCKSS = 1                                              |       | 921.6 |       | KIIZ                |

| Spread Spectrum                     | Δf <sub>DC_SPRD</sub>   | FREQ = high, BI                                      | UCKSS = 1                                               |       | 7     |       | %                   |

| Feedback (FB) Regulation<br>Voltage | V <sub>DC_FB</sub>      |                                                      |                                                         |       | 0.9   |       | V                   |

| Output Voltage Accuracy             | ACC <sub>DCFB</sub>     |                                                      |                                                         | -1    | 0     | +1    | %                   |

| Feedback (FB) OK Threshold          | V <sub>DC_FBOK</sub>    | FB rising                                            |                                                         | 91.5  | 95.3  | 99.4  | %V <sub>DC_FB</sub> |

| Feedback (FB) Low<br>Threshold      | V <sub>DC_FBTHLOW</sub> |                                                      |                                                         | 61    | 64    | 72    | %V <sub>DC_FB</sub> |

| LX On-Resistance<br>(High Side)     | R <sub>DC_HS</sub>      | From V <sub>24</sub> to LX, (Note 3)                 |                                                         | 1.4   | 2.6   | Ω     |                     |

| LX On-Resistance<br>(Low Side)      | R <sub>DC_LS</sub>      | From LX to GND (Note 3)                              |                                                         |       | 0.85  | 1.7   | Ω                   |

| Active Diode On-Resistance          | R <sub>DC_ACT</sub>     | DC current (Note                                     | e 3)                                                    |       | 5.1   | 10    | Ω                   |

| Peak Current into Active Diode      | IDC_ACTMAX              | (Note 3)                                             |                                                         |       |       | 200   | mA                  |

| Maximum LX Current Ripple           | ΔI <sub>DC LX</sub>     |                                                      |                                                         |       | 100   |       | %                   |

| High-Side Peak Current Limit        | I <sub>DC_HS(LIM)</sub> |                                                      |                                                         | 650   | 750   | 860   | mA                  |

| Low-Side Current Limit              | IDC_LS(MAX)             |                                                      |                                                         | -375  | -300  | -240  | mA                  |

| DC-DC Autoretry Period              | T <sub>DCRETRY</sub>    |                                                      |                                                         |       | 22    |       | ms                  |

| External Capacitance on PV24        | C <sub>DC_PV24</sub>    |                                                      |                                                         | 1     |       |       | μF                  |

| DC CHARACTERISTICS / 5V             | LINEAR REGUL            | ATOR (V <sub>5</sub> )                               |                                                         |       |       |       |                     |

| V <sub>5</sub> Input Supply Voltage | V <sub>LIN</sub>        |                                                      |                                                         | 6     |       | 36    | V                   |

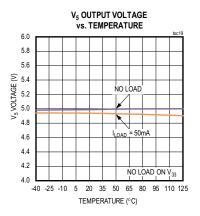

| V <sub>5</sub> Output Voltage       | V <sub>5</sub>          | 6V ≤ V <sub>LIN</sub> ≤ 36V                          | , no load on V <sub>5</sub>                             | 4.75  | 4.92  | 5.25  | V                   |

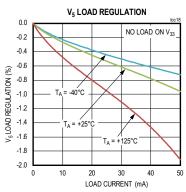

| V <sub>5</sub> Load Regulation      | ΔV <sub>5LDR</sub>      | V <sub>LIN</sub> = 24V, 1mA                          | A < I <sub>LOAD</sub> < 50mA                            |       | 0.8   | 2     | %                   |

| V <sub>5</sub> Line Regulation      | $\Delta V_{5LNR}$       | 6V ≤ V <sub>LIN</sub> ≤ 36V, I <sub>LOAD</sub> = 1mA |                                                         |       | 0.03  | 0.15  | mV/V                |

| V <sub>5</sub> Load Capacitance     | C <sub>V5</sub>         | External capacit                                     | 1                                                       |       |       | μF    |                     |

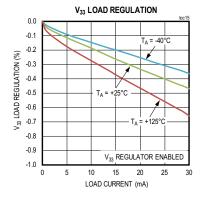

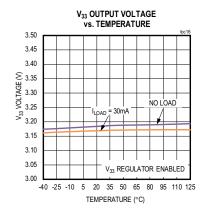

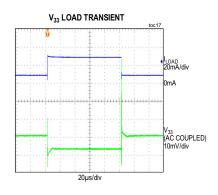

| DC CHARACTERISTICS / 3.3            | V LINEAR REGU           | LATOR (V <sub>33</sub> )                             |                                                         |       |       |       |                     |

| V <sub>33</sub> Output Voltage      | V <sub>33</sub>         | No load                                              | 3.1                                                     | 3.17  | 3.3   | V     |                     |

| V <sub>33</sub> Load Regulation     | ΔV <sub>33_LR</sub>     | 1mA < I <sub>LOAD</sub> < 3                          | 30mA                                                    | 0     | 0.35  | 1     | %                   |

| V <sub>33</sub> Load Capacitance    | C <sub>V33</sub>        | External capacit                                     | ance on V <sub>33</sub>                                 | 1     |       |       | μF                  |

## **DC Electrical Characteristics (continued)**

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{DGND}=V_{SGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  (Note 2)

| PARAMETER                                    | SYMBOL                                | CON                                                                 | MIN                                                     | TYP                   | MAX  | UNITS |                  |

|----------------------------------------------|---------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-----------------------|------|-------|------------------|

| DC CHARACTERISTICS / C/O                     | Q, DO/DI DRIVER                       |                                                                     |                                                         |                       |      |       |                  |

| C/Q, DO/DI Driver High-Side<br>On-Resistance | R <sub>CQOH</sub> , R <sub>DOOH</sub> | High-side enabled I <sub>LOAD</sub> = +200mA                        |                                                         |                       | 2.25 | 4.2   | Ω                |

| C/Q, DO/DI Driver Low-Side<br>On-Resistance  | R <sub>DOOL</sub> , R <sub>DOOL</sub> | Low-side enabled I <sub>LOAD</sub> = -200mA (                       |                                                         |                       | 2.07 | 4.1   | Ω                |

|                                              |                                       |                                                                     | CL[1:0] = 00                                            | 50                    | 67   | 82    |                  |

| C/Q, DO/DI Driver Current                    |                                       | V <sub>DROP</sub> = 3V                                              | CL[1:0] = 01                                            | 100                   | 120  | 140   | A                |

| Limit                                        | ICQCL, IDOCL                          | (Note 4)                                                            | CL[1:0] = 10                                            | 200                   | 240  | 280   | mA mA            |

|                                              |                                       |                                                                     | CL[1:0] = 11                                            | 250                   | 300  | 350   |                  |

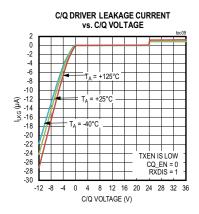

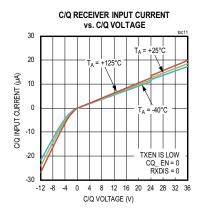

| C/Q Leakage Current                          | I <sub>LEAK_CQ</sub>                  |                                                                     | 36V) ≤ V <sub>C/Q</sub> ≤ 36V,<br>Q receiver disabled   | -40                   |      | +30   | μA               |

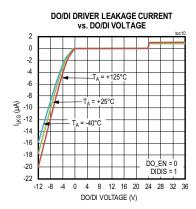

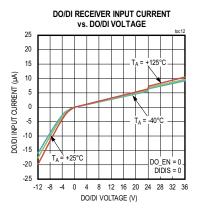

| DO/DI Leakage Current                        | I <sub>LEAK_DO</sub>                  | V <sub>24</sub> = 24V, (V <sub>24</sub> – DO/DI driver disal        | 36V) ≤ V <sub>DO/DI</sub> ≤ 36V,<br>oled                | -30                   |      | +17   | μA               |

| C/Q Output Reverse Current                   | I <sub>REV_CQ</sub>                   | C/Q driver enable $V_{C/Q} = (V_{24} + 5V)$                         | d and in push-pull,<br>or (V <sub>GND</sub> - 5V)       | -100                  |      | +300  | μA               |

| DO/DI Output Reverse<br>Current              | I <sub>REV_DO/DI</sub>                | DO/DI driver enab<br>V <sub>DO/DI</sub> = (V <sub>24</sub> + 5      | oled and in push-pull,<br>V) or (V <sub>GND</sub> - 5V) | -100                  |      | +300  | μA               |

| C/Q, DO/DI Weak Pull-Down<br>Current         | I <sub>CQPD</sub> , I <sub>DOPD</sub> | Driver disabled, V<br>CQ_PD = 1, CQ_<br>DO_PD = 1, DO_              |                                                         | -400                  | -300 | -230  | μΑ               |

| C/Q, DO/DI Weak Pull-Up<br>Current           | I <sub>CQPU</sub> , I <sub>DOPU</sub> | Driver disabled, V <sub>C</sub><br>CQ_PD = 0, CQ_<br>DO_PD = 0, DO_ |                                                         | +230                  | +300 | +400  | μА               |

| DC CHARACTERISTICS / C/O                     | Q, DO/DI RECEIV                       | ER                                                                  |                                                         |                       |      |       |                  |

| C/Q, DO/DI Input Voltage<br>Range            | V <sub>CQIN</sub> , V <sub>DIIN</sub> | For valid RX/LI lo                                                  | gic                                                     | V <sub>24</sub> - 36V |      | 36    | V                |

| C/Q, DO/DI Input Threshold                   | \/\/                                  | Driver disabled                                                     | V <sub>24</sub> ≥ 18V                                   | 10.75                 |      | 12.5  | V                |

| High                                         | V <sub>CQTH</sub> , V <sub>DITH</sub> | Driver disabled                                                     | V <sub>24</sub> < 18V                                   | 53.1                  |      | 84.4  | %V <sub>24</sub> |

| C/Q, DO/DI Input Threshold                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Driver disabled                                                     | V <sub>24</sub> ≥ 18V                                   | 9                     |      | 10.5  | V                |

| Low                                          | V <sub>CQTL</sub> , V <sub>DITL</sub> | Driver disabled                                                     | V <sub>24</sub> < 18V                                   | 43.75                 |      | 72    | %V <sub>24</sub> |

| C/O DO/DI Input Hystorosis                   | V <sub>CQHYS</sub> ,                  | Driver disabled                                                     | V <sub>24</sub> ≥ 18V                                   | 1.45                  | 1.9  | 2.15  | V                |

| C/Q, DO/DI Input Hysteresis                  | V <sub>DIHYS</sub>                    | Driver disabled V <sub>24</sub> < 18V                               |                                                         | 6.25                  | 11.4 | 15.6  | %V <sub>24</sub> |

| C/Q Input Capacitance                        | C <sub>IN_CQ</sub>                    | Driver disabled, CQ_PD = 0, CQ_PU = 0, f = 100kHz                   |                                                         |                       | 35   |       | pF               |

| DO/DI Input Capacitance                      | C <sub>IN_DI</sub>                    | Driver disabled, D<br>DO_PU = 0, f = 10                             |                                                         |                       | 35   |       | pF               |

## **DC Electrical Characteristics (continued)**

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{DGND}=V_{SGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.)$  (Note 2)

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                                                    | MIN                   | TYP    | MAX                  | UNITS |

|-------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|-----------------------|--------|----------------------|-------|

| DC CHARACTERISTICS / AU                         | XILIARY INPUTS          | (RESET, FREQ)                                                                                 |                       |        |                      |       |

| RESETInput Voltage Low                          | V <sub>RSTIL</sub>      |                                                                                               |                       |        | 3.05                 | V     |

| RESETInput Voltage High                         | V <sub>RSTIH</sub>      |                                                                                               | 0.8                   |        |                      | V     |

| FREQ Input Voltage Low                          | V <sub>FREQIL</sub>     |                                                                                               |                       |        | 3.05                 | V     |

| FREQ Input Voltage High                         | V <sub>FREQIH</sub>     |                                                                                               | 0.8                   |        |                      | V     |

| RESETOutput Voltage Low                         | V <sub>POKLOW</sub>     | I <sub>LOAD</sub> = 5mA                                                                       |                       |        | 0.2                  | V     |

| DC CHARACTERISTICS / LO                         | GIC INPUTS (SP          |                                                                                               | TX, TXEN, I           | LO/LI) |                      |       |

| Logic Input Voltage Low                         | V <sub>IL</sub>         |                                                                                               |                       |        | 0.2 x V <sub>L</sub> | V     |

| Logic Input Voltage High                        | V <sub>IH</sub>         |                                                                                               | 0.8 x V <sub>L</sub>  |        |                      | V     |

| Logic Input Leakage Current                     | I <sub>LEAK</sub>       | Logic input = GND or V <sub>L</sub>                                                           | -1                    |        | +1                   | μA    |

| DC CHARACTERISTICS / LO                         | GIC OUTPUTS (           | WU, IRQ, SDO/SDA, RX, LO/LI, MCLK)                                                            |                       |        |                      |       |

| Logic Output Voltage Low                        | V <sub>OL</sub>         | WU, SDO/SDA, RX, LO/LI, MCLK, I <sub>LOAD</sub> = -5mA                                        |                       |        | 0.2                  | V     |

| Logic Output Voltage High                       | V <sub>OH</sub>         | WU, SDO/SDA, RX, LO/LI, MCLK, I <sub>LOAD</sub> = +5mA                                        | V <sub>L</sub> - 0.3V |        |                      | V     |

| IRQOpen-Drain High<br>Impedance Leakage Current | I <sub>LK_OD</sub>      | IRQnot asserted                                                                               | -1                    |        | +1                   | μΑ    |

| SDO/SDA Leakage Current                         | I <sub>LK_SDO</sub>     | $\overline{SPI}/I^2C = Iow, \overline{CS}/A0 = high$                                          | -1                    |        | +1                   | μA    |

| RX, LO/LI Leakage Current                       | I <sub>LK_RXLI</sub>    | RX = LO/LI = GND or V <sub>L</sub> ,DO_EN = 1                                                 | -1                    |        | +1                   | μA    |

| DC CHARACTERISTICS / THI                        | ERMAL CHARA             | CTERISTICS                                                                                    |                       |        |                      |       |

| C/Q or DO/DI Per-Driver<br>Shutdown Temperature | T <sub>SHUT_DRV</sub>   | Driver temperature rising, C/Q or DO/<br>DI driver fault bit is set and driver is<br>disabled |                       | +150   |                      | °C    |

| C/Q or DO/DI Per-Driver<br>Shutdown Hysteresis  | T <sub>SHUT_DHYS</sub>  | Driver temperature falling, driver is automatically reenabled                                 |                       | 8      |                      | °C    |

| IC Thermal Warning<br>Threshold                 | T <sub>WRN</sub>        | Die temperature rising, THERMW and THERMWINT bits are set                                     |                       | +147   |                      | °C    |

| IC Thermal Warning<br>Threshold Hysteresis      | T <sub>WRN_HYS</sub>    | Die temperature falling, THERMW bit is cleared                                                |                       | 9      |                      | °C    |

| IC Thermal Shutdown<br>Threshold                | T <sub>SHUT_IC</sub>    | Die temperature rising                                                                        |                       | +170   |                      | °C    |

| IC Thermal Shutdown<br>Hysteresis               | T <sub>SHUT_ICHYS</sub> | Die temperature                                                                               |                       | 17     |                      | °C    |

#### **AC Electrical Characteristics**

$(V_{24} = 18 \text{V to } 30 \text{V}, V_5 = 4.5 \text{V to } 5.5 \text{V}, V_L = 2.5 \text{V to } 5.5 \text{V}, V_{DGND} = V_{SGND} = V_{GND} = 0 \text{V}, \text{All logic inputs at V}_L \text{ or GND}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER                    | SYMBOL               | CON                                                          | MIN                                       | TYP    | MAX  | UNITS |      |

|------------------------------|----------------------|--------------------------------------------------------------|-------------------------------------------|--------|------|-------|------|

| AC ELECTRICAL CHARACTE       | RISTICS / C/Q,       | DO/DI DRIVER                                                 |                                           |        |      |       |      |

| Driver Low-to-High           | t <sub>PDLH_PP</sub> | CQLOSLEW[1:0]<br>or                                          | Push-pull or PNP mode                     |        | 0.74 | 1     | lie. |

| Propagation Delay            | t <sub>PDLH_OC</sub> | DOLOSLEW[1:0]<br>= 00, <u>Figure 1</u>                       | NPN mode                                  |        | 1    |       | μs   |

| Driver High-to-Low           | t <sub>PDHL_PP</sub> | CQLOSLEW[1:0]<br>or                                          | Push-pull or NPN mode                     |        | 0.99 | 1.4   | μs   |

| Propagation Delay            | t <sub>PDHL_OC</sub> | DOLOSLEW[1:0]<br>= 00, <u>Figure 1</u>                       | PNP mode                                  |        | 1    |       | μσ   |

| Driver Skew                  | t <sub>SKEW</sub>    | t <sub>PDLH</sub> - t <sub>PDHL</sub>  , C<br> DOLOSLEW[1:0] | CQLOSLEW[1:0] or<br>= 00                  | -0.575 |      | +0.1  | μs   |

|                              |                      |                                                              | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 00 | 0.1    | 0.2  | 0.325 |      |

| D D T.                       | Push-pull or PNP     | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 01                    |                                           | 0.40   |      | ı     |      |

| Driver Rise Time             | <sup>t</sup> RISE    | mode, V <sub>24</sub> (max) = 30V, <u>Figure 1</u>           | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 10 |        | 1.22 |       | · µs |

|                              |                      |                                                              | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 11 |        | 4.7  |       |      |

|                              |                      |                                                              | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 00 | 0.2    | 0.34 | 0.475 |      |

| Division in the second       | ,                    | Push-pull or NPN                                             | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 01 |        | 0.66 |       |      |

| Driver Fall Time             | <sup>†</sup> FALL    | mode, V <sub>24</sub> (max)<br>= 30V, <u>Figure 1</u>        | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 10 |        | 1.64 |       | μs   |

|                              |                      |                                                              | CQLOSLEW[1:0] or<br>DOLOSLEW[1:0]<br>= 11 |        | 7.1  |       |      |

| C/Q Driver Enable Time High  | t <sub>ENH</sub>     | Push-pull or PNP mode, Figure 2                              |                                           |        | 0.74 | 1.1   | μs   |

| C/Q Driver Enable Time Low   | t <sub>ENL</sub>     | Push-pull or NPN                                             | mode, Figure 3                            |        | 0.3  | 0.45  | μs   |

| C/Q Driver Disable Time High | t <sub>DISH</sub>    | Push-pull or PNP                                             |                                           | 1.8    |      | μs    |      |

| C/Q Driver Disable Time Low  | t <sub>DISL</sub>    | Push-pull or NPN                                             | mode, Figure 3                            |        | 1.8  |       | μs   |

## **AC Electrical Characteristics (continued)**

$(V_{24}=18V\text{ to }30V,\ V_5=4.5V\text{ to }5.5V,\ V_L=2.5V\text{ to }5.5V,\ V_{DGND}=V_{SGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ T_A=-40^{\circ}C\ to+125^{\circ}C,\ unless\ otherwise\ noted.$  (Note 2)

| PARAMETER                                           | SYMBOL               | CONDITIONS        |                     | MIN     | TYP    | MAX    | UNITS |  |

|-----------------------------------------------------|----------------------|-------------------|---------------------|---------|--------|--------|-------|--|

| AC ELECTRICAL CHARACTERISTICS / C/Q, DO/DI RECEIVER |                      |                   |                     |         |        |        |       |  |

| C/Q Receiver Low-to-High                            | _                    | Figure 4          | RXFILTER = 1        | 0.75    | 1.2    | 1.7    |       |  |

| Propagation Delay                                   | <sup>t</sup> PRLH_CQ | Figure 4          | RXFILTER = 0        | 0.2     | 0.33   | 0.475  | μs    |  |

| C/Q Receiver High-to-Low                            | 4                    | Figure 4          | RXFILTER = 1        | 0.7     | 1.13   | 1.65   |       |  |

| Propagation Delay                                   | tprhl_cq             | Figure 4          | RXFILTER = 0        | 0.125   | 0.25   | 0.375  | μs    |  |

| DO/DI Receiver Low-to-High                          | <b>t</b>             | Figure 4          | DIFILTER = 1        | 1.3     | 2.1    | 2.9    | 110   |  |

| Propagation Delay                                   | <sup>t</sup> PRLH_DI | Figure 4          | DIFILTER = 0        | 0.7     | 1.2    | 1.65   | μs    |  |

| DO/DI Receiver High-to-Low                          | too o.               | Figure 4          | DIFILTER = 1        | 1.1     | 1.8    | 2.55   | 116   |  |

| Propagation Delay                                   | <sup>t</sup> PRHL_DI | <u>Figure 4</u>   | DIFILTER = 0        | 0.55    | 0.91   | 1.3    | μs    |  |

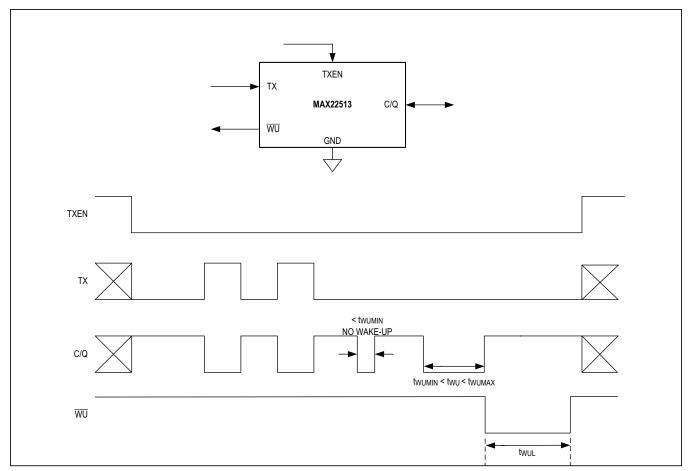

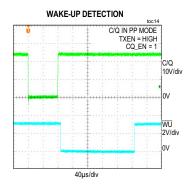

| AC ELECTRICAL CHARACTE                              | RISTICS / WAK        | E-UP DETECTION    | (Figure 5)          |         |        |        |       |  |

| Wake-Up Input Minimum<br>Pulse Width                | twumin               | C/Q load capacita | ance = 3nF          | 59.4    | 66     | 72.6   | μs    |  |

| Wake-Up Input Maximum<br>Pulse Width                | t <sub>WUMAX</sub>   |                   |                     | 85.5    | 95     | 104.5  | μs    |  |

| WU Output Low Time                                  | t <sub>WUL</sub>     | Valid wake-up co  | ndition on C/Q      | 180     | 200    | 220    | μs    |  |

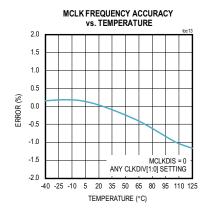

| AC ELECTRICAL CHARACTE                              | ERISTICS / MCLI      | K CLOCK           |                     |         |        |        |       |  |

|                                                     |                      | CLKDIV[1:0] = 00  | CLKDIV[1:0] = 00    |         | 3.686  | 3.779  | MHz   |  |

| MCLK Frequency                                      | formula              | CLKDIV[1:0] = 01  |                     | 7.188   | 7.373  | 7.557  |       |  |

| MOLK Frequency                                      | fMCLK                | CLKDIV[1:0] = 10  |                     | 14.377  | 14.746 | 15.114 |       |  |

|                                                     |                      | CLKDIV[1:0] = 11  |                     | 1.797   | 1.843  | 1.889  |       |  |

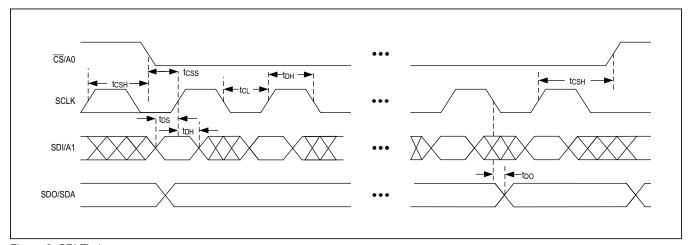

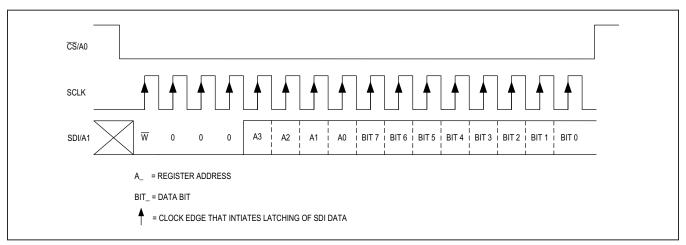

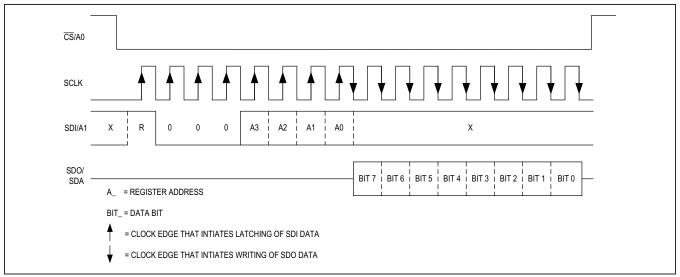

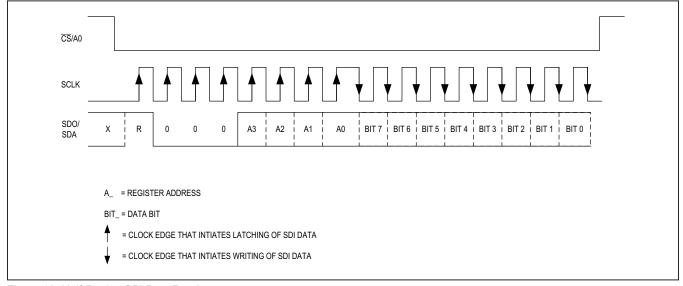

| AC ELECTRICAL CHARACTE                              | RISTICS / SPI T      | IMING (CS/A0, SC  | LK, SDI/A1, SDO/SDA | (Figure | 6)     |        |       |  |

| Maximum SCLK Frequency                              | f <sub>SPI_MAX</sub> | Read/write        |                     |         |        | 12     | MHz   |  |

| SCLK Clock Period                                   | t <sub>CH+CL</sub>   | Read/write        |                     | 80      |        |        | ns    |  |

| SCLK Pulse Width High                               | t <sub>CH</sub>      | Write only        |                     | 20      |        |        | ns    |  |

| SCLK Pulse Width Low                                | t <sub>CL</sub>      | Write only        |                     | 20      |        |        | ns    |  |

| CS/A0 Fall to SCLK Rise Time                        | t <sub>CSS</sub>     |                   |                     | 10      |        |        | ns    |  |

| SCLK Rise to CS/A0 Rise<br>Hold Time                | <sup>t</sup> CSH     |                   |                     | 10      |        |        | ns    |  |

| SDI/A1 Hold Time                                    | t <sub>DH</sub>      |                   |                     | 5       |        |        | ns    |  |

| SDI/A1 Setup Time                                   | t <sub>DS</sub>      |                   |                     | 5       |        |        | ns    |  |

| SDO/SDA Output Data<br>Propagation Delay            | t <sub>DO</sub>      |                   |                     |         |        | 32     | ns    |  |

| SDO/SDA Rise and Fall<br>Times                      | t <sub>FT</sub>      |                   |                     | 1.5     |        | ns     |       |  |

| Minimum CS/A0 Pulse                                 | t <sub>CSW</sub>     |                   |                     | 5       |        | ns     |       |  |

#### **AC Electrical Characteristics (continued)**

$(V_{24} = 18 \text{V to } 30 \text{V}, V_5 = 4.5 \text{V to } 5.5 \text{V}, V_L = 2.5 \text{V to } 5.5 \text{V}, V_{DGND} = V_{SGND} = V_{GND} = 0 \text{V}, \text{All logic inputs at V}_L \text{ or GND}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.} \text{ (Note 2)}$

| PARAMETER                                                                                    | SYMBOL              | CONDITIONS                                 | MIN  | TYP | MAX | UNITS |  |  |

|----------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|------|-----|-----|-------|--|--|

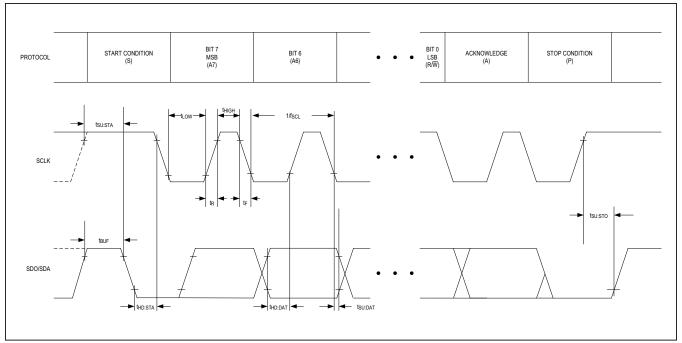

| AC ELECTRICAL CHARACTERISTICS / I <sup>2</sup> C COMPATIBLE TIMING SPECIFICATIONS (Figure 7) |                     |                                            |      |     |     |       |  |  |

| Maximum I <sup>2</sup> C Clock<br>Frequency                                                  | fsclk               |                                            |      |     | 2   | MHz   |  |  |

| Maximum Clock Period                                                                         | tscl_max            |                                            | 100  |     |     | μs    |  |  |

| Bus Free Time Between STOP and START Conditions                                              | t <sub>BUF</sub>    |                                            | 0.2  |     |     | μs    |  |  |

| START Condition Setup Time                                                                   | t <sub>SU:STA</sub> |                                            | 0.1  |     |     | μs    |  |  |

| Repeat START Condition<br>Setup Time                                                         | tsu:sta             | 90% to 90%                                 | 0.1  |     |     | μs    |  |  |

| START Condition Hold Time                                                                    | t <sub>HD:STA</sub> | 10% of SDA/SDO to 90% of SCLK              | 0.15 |     |     | μs    |  |  |

| STOP Condition Setup Time                                                                    | t <sub>SU:STO</sub> | 90% of SCLK to 10% of SDA/SDO              | 0.1  |     |     | μs    |  |  |

| Clock Low Period                                                                             | t <sub>LOW</sub>    | 10% to 10%                                 | 0.1  |     |     | μs    |  |  |

| Clock High Period                                                                            | <sup>t</sup> HIGH   | 90% to 90%                                 | 0.15 |     |     | μs    |  |  |

| Data Valid to SCLK Rise Time                                                                 | t <sub>SU:DAT</sub> | Write setup time                           | 50   |     |     | ns    |  |  |

| Data Hold Time                                                                               | t <sub>HD:DAT</sub> | Write hold time                            |      |     | 0   | ns    |  |  |

| Maximum SDO/SDA Drive<br>Low Time                                                            | t <sub>DATLOW</sub> |                                            | 1.0  | 1.1 | 1.2 | ms    |  |  |

| ESD AND EMC CHARACTERI                                                                       | STICS               |                                            |      |     |     |       |  |  |

| ESD Protection                                                                               |                     | IEC 61000-4-2 Contact Discharge            |      | ±2  |     | kV    |  |  |

| (C/Q, DO/DI, V <sub>24</sub> Pins)                                                           |                     | IEC 61000-4-2 Airgap Discharge             |      | ±3  |     | N.V   |  |  |

| ESD Protection<br>(All Other Pins)                                                           |                     | Human Body Model                           |      | ±2  |     | kV    |  |  |

| Surge Protection<br>(C/Q, DO/DI, V <sub>24</sub> Pins)                                       | V <sub>SRG</sub>    | IEC 61000-4-5, 500Ω 8/20μs surge to ground |      | ±1  |     | kV    |  |  |

Note 2: All devices 100% productions tested at 25°C. Limits over the operating temperature range are guaranteed by design.

Note 3: Not production tested. Guaranteed by design.

Note 4: V<sub>DROP</sub> is measured as the voltage from the driver output to GND (V<sub>DRIVER</sub> - V<sub>GND</sub>) when measuring thelow-side driver current limit and as (V<sub>24</sub> - V<sub>DRIVER</sub>) when measuring the high-side driver current limit.

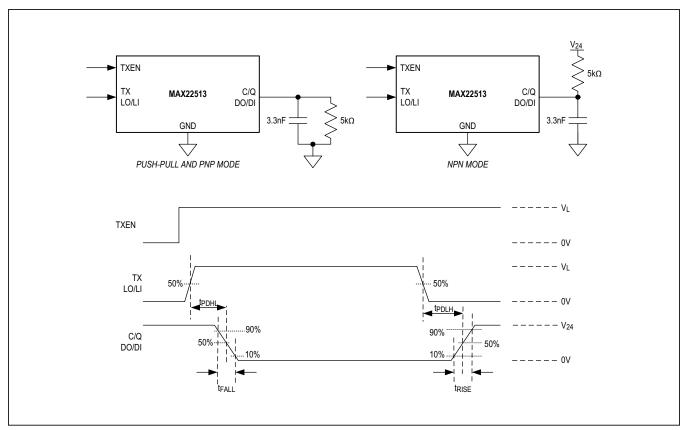

Figure 1. C/Q and DO/DI Driver Propagation Delays

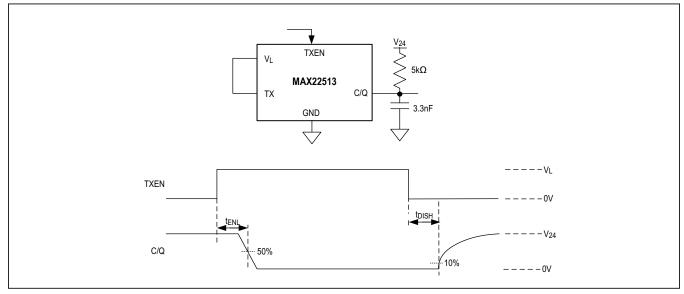

Figure 2. C/Q Driver Enable Low and Disable High Timing

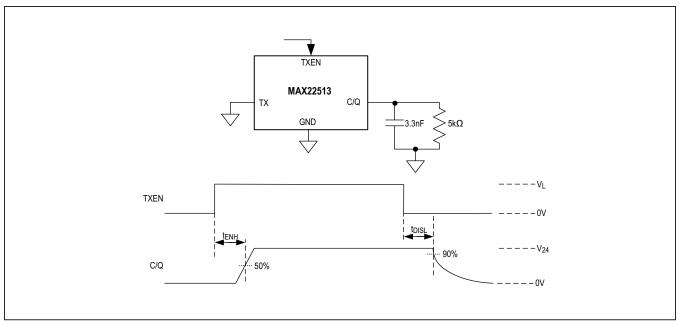

Figure 3. C/Q Driver Enable/Disable Timing

Figure 4. C/Q Receiver Timing

Figure 5. Wake-Up Timing

Figure 6. SPI Timing

Figure 7. I<sup>2</sup>C Timing

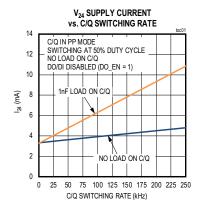

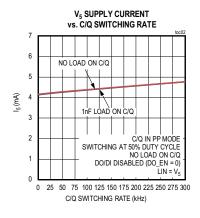

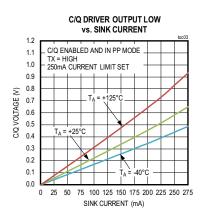

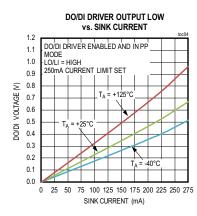

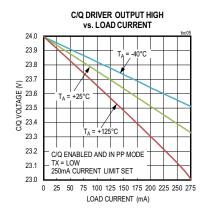

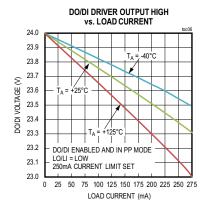

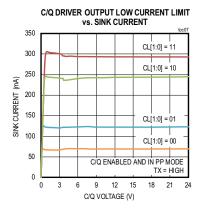

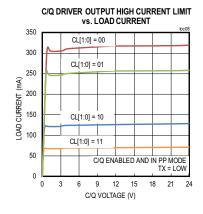

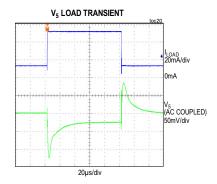

### **Typical Operating Characteristics**

$(V_{24} = 24V, V_5 = 5V, DC-DC regulator enabled, V_L = V_{33}, T_A = +25$ °C, unless otherwise noted)

## **Typical Operating Characteristics (continued)**

$(V_{24} = 24V, V_5 = 5V, DC-DC regulator enabled, V_L = V_{33}, T_A = +25^{\circ}C, unless otherwise noted)$

## **Typical Operating Characteristics (continued)**

$(V_{24} = 24V, V_5 = 5V, DC-DC regulator enabled, V_L = V_{33}, T_A = +25^{\circ}C, unless otherwise noted)$

## **Pin Configurations**

## **Pin Description**

| PIN      |               |                  |                                                                                                                                                                                                                                                   |  |  |  |  |

|----------|---------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TQFN     | WLP           | NAME             | FUNCTION                                                                                                                                                                                                                                          |  |  |  |  |

| SUPPLY   | l.            |                  |                                                                                                                                                                                                                                                   |  |  |  |  |

| 1        | B1            | V <sub>CCB</sub> | Internal 5V Supply Regulator Output. Bypass $V_{CCB}$ to GND with a 1 $\mu$ F capacitor as close to the device as possible. $V_{CCB}$ can supply an external load up to 5mA.                                                                      |  |  |  |  |

| 3        | A2            | GND              | Ground                                                                                                                                                                                                                                            |  |  |  |  |

| 4        | A3            | PV24             | Active Diode Output and DC-DC Input. Bypass PV24 with an external 1µF capacitor as close to the device as possible.                                                                                                                               |  |  |  |  |

| 5        | В3            | LIN              | 5V Linear Regulator Input. Connect LIN to the output of the DC-DC circuit, to the PV24 supply, or to an external supply between 6V and 36V. Bypass LIN to GND with a $1\mu$ F capacitor. Connect LIN to $V_5$ to disable the 5V linear regulator. |  |  |  |  |

| 6        | A4            | V <sub>5</sub>   | 5V Linear Regulator Output/Supply Input. $V_5$ is the output of the internal 5V linear regulator. Bypass $V_5$ to GND with a $1\mu F$ capacitor as close to the device as possible. To disable the 5V linear regulator, connect LIN to $V_5$ .    |  |  |  |  |

|          |               | -                | 5V is required on $V_5$ for normal operation. If the 5V regulator is disabled, apply an external 5V power supply to $V_5$ .                                                                                                                       |  |  |  |  |

| 12       | B6, B7,<br>B8 | V <sub>24</sub>  | Supply Voltage Input. Apply a 24V (typ) supply to $V_{24}$ . Bypass $V_{24}$ to GND with a 10nF capacitor as close to the device as possible.                                                                                                     |  |  |  |  |

|          | Бо            |                  | When using the WLP package, connect all V <sub>24</sub> bumps together.                                                                                                                                                                           |  |  |  |  |

| 14       | D8            | DGND             | C/Q and DO/DI Driver IO-Link Ground. Connect DGND to the L-terminal of the IO-Link connector and to GND. See the <i>Layout and Grounding</i> section for more information.                                                                        |  |  |  |  |

| 24       | D2            | VL               | Logic Supply Input. Bypass $V_L$ to GND with a $1\mu F$ capacitor as close to the device as possible. $V_L$ sets the logic levels for all logic signals. Connect $V_L$ to $V_{33}$ , $V_5$ , or to an external voltage between 2.5V and 5.5V.     |  |  |  |  |

| 25       | D1            | SGND             | Signal Ground. Connect SGND to GND. See the <i>Layout and Grounding</i> section for more information.                                                                                                                                             |  |  |  |  |

| 26       | C2            | V <sub>33</sub>  | 3.3V Linear Regulator Output. Bypass $V_{33}$ to GND with a 1 $\mu$ F capacitor as close to the device as possible.                                                                                                                               |  |  |  |  |

| EP       | -             | EP               | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                   |  |  |  |  |

| DC-DC RE | GULATOR       |                  |                                                                                                                                                                                                                                                   |  |  |  |  |

| 2        | A1            | LX               | Switching Output of the Integrated DC-DC Converter. Connect an inductor between LX and the output capacitor to generate a voltage with the DC-DC circuit. See the <i>Integrated DC-DC Regulator</i> section for more information.                 |  |  |  |  |

| 10       | A6            | FREQ             | DC-DC Buck Regulator Frequency Select Input. Connect FREQ to GND to operate the DC-DC regulator at a switching frequency of 921kHz (typ). Connect FREQ to V <sub>CCB</sub> to operate the regulator at a switching frequency of 1.229MHz (typ).   |  |  |  |  |

| 27       | C1            | FB               | DC-DC Buck Regulator Feedback Input. Connect FB to the tap of a resistor divider between the output of the DC-DC and GND. See <u>Table 1</u> for recommended component values to set the DC-DC output between 2.5V and 12V.                       |  |  |  |  |

|          |               |                  | Connect FB to V <sub>CCB</sub> if the DC-DC is not used.                                                                                                                                                                                          |  |  |  |  |

## **Pin Description (continued)**

| Р          | IN        | NAME    | FUNCTION                                                                                                                                                                                                                                     |       |                                                                                                                                                                                                                                                                          |  |  |

|------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN       | WLP       | NAME    | FUNCTION                                                                                                                                                                                                                                     |       |                                                                                                                                                                                                                                                                          |  |  |

| 24V LINE I | INTERFACE |         |                                                                                                                                                                                                                                              |       |                                                                                                                                                                                                                                                                          |  |  |

| 11         | A7, A8    | DO/DI   | DO Auxiliary Driver Output/DI Auxiliary Digital Input. Use the register bits to select between digital output (DO) and digital input (DI) functionality for DO/DI. The DO/DI driver is disabled at started.                                  |       |                                                                                                                                                                                                                                                                          |  |  |

|            |           |         | When using the WLP package, only one of the DO/DI bumps need to be soldered. However, Maxim recommends connecting both bumps whenever possible.                                                                                              |       |                                                                                                                                                                                                                                                                          |  |  |

| 40         | 07.00     | 6/0     | IO-Link Transceiver Input/Output. The C/Q driver is disabled at startup. Set CQ_EN = 1 and TXEN = high to enable the C/Q driver.                                                                                                             |       |                                                                                                                                                                                                                                                                          |  |  |

| 13         | C7, C8    | C/Q     | When using the WLP package, only one of the C/Q bumps needs to be connected. However, Maxim recommends connecting both C/Q bumps whenever possible.                                                                                          |       |                                                                                                                                                                                                                                                                          |  |  |

| CONTROL    | INTERFAC  | Ē       |                                                                                                                                                                                                                                              |       |                                                                                                                                                                                                                                                                          |  |  |

| 7          | B4        | ĪRQ     | Active-Low Open-Drain Interrupt Request Output. $\overline{IRQ}$ asserts low when a bit is set in the INTERRUPT register. See the <i>Register Map</i> section for more information.                                                          |       |                                                                                                                                                                                                                                                                          |  |  |

|            |           |         | Dual Function Active-Low Reset Input and Open-Drain Power-OK (POK) Output. Drive RESET low to set the MAX22513 in reset mode. The C/Q and DO/DI outputs are disabled and all registers are reset to default values when RESET is driven low. |       |                                                                                                                                                                                                                                                                          |  |  |

| 8          | A5        | A5      | A5                                                                                                                                                                                                                                           | RESET | The MAX22513 asserts $\overline{\text{RESET}}$ low when any of the V <sub>24</sub> , V <sub>5</sub> , or DC-DC output voltages are below their respective undervoltage lockout (UVLO) thresholds. Only V <sub>5</sub> is monitored when the DC-DC regulator is disabled. |  |  |

|            |           |         | The MAX22513 deasserts RESET 4ms (typ) after the power supplies rise above their UVLO thresholds.                                                                                                                                            |       |                                                                                                                                                                                                                                                                          |  |  |

|            |           |         | Connect $\overline{\text{RESET}}$ to $V_{CCB}$ or $V_L$ with a $10k\Omega$ (typ) resistor for normal operation.                                                                                                                              |       |                                                                                                                                                                                                                                                                          |  |  |

| 9          | B5        | LO/LI   | DO/DI Driver Logic Input/Receiver Logic Output. LO/LI is an output by default (DO_EN = 0 in the DOCONFIG register). In this configuration, LO/LI is inverted relative to the logic state of the DO/DI input.                                 |       |                                                                                                                                                                                                                                                                          |  |  |

| 9          | B3        | LO/LI   | LO/LI is configured as an input when the DO/DI driver is enabled (DO_EN = 1 in the DOCONFIG register). In this configuration, DO/DI driver is inverted relative to the LO/LI logic state.                                                    |       |                                                                                                                                                                                                                                                                          |  |  |

| 15         | D7        | WU      | IO-Link Wake-Up Request Output. WU asserts low for 200μs (typ) when a valid IO-Link wake-up pulse is detected on the C/Q line.                                                                                                               |       |                                                                                                                                                                                                                                                                          |  |  |

| 19         | D5        | SDO/SDA | Serial Data Output/Serial Data I/O. In SPI mode, SDO/SDA is the serial data output (MISO). SDO/SDA is high impedance when $\overline{\text{CS}}/\text{A0}$ is high.                                                                          |       |                                                                                                                                                                                                                                                                          |  |  |

|            |           |         | In I <sup>2</sup> C mode, SDO/SDA operates as the serial data I/O line.                                                                                                                                                                      |       |                                                                                                                                                                                                                                                                          |  |  |

| 20         | D4        | SCLK    | Serial Clock Input.                                                                                                                                                                                                                          |       |                                                                                                                                                                                                                                                                          |  |  |

| 21         | C4        | SDI/A1  | Serial Data Input/Address Select Input 1. In SPI mode, SDI/A1 operates as the serial data input (MOSI).                                                                                                                                      |       |                                                                                                                                                                                                                                                                          |  |  |

|            |           |         | In I <sup>2</sup> C mode, connect SDA/A1 high or low to set the I <sup>2</sup> C slave address for the device.                                                                                                                               |       |                                                                                                                                                                                                                                                                          |  |  |

## **Pin Description (continued)**

| Р         | IN       | NAME                                                                                                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN      | WLP      | NAME                                                                                                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                              |

| 22        | C3 CS/A0 |                                                                                                                         | SPI Chip-Select Input/I <sup>2</sup> C Address Input 0. In SPI mode, drive $\overline{CS}$ /A0 low to start a read/ write cycle. The cycle ends when $\overline{CS}$ /A0 is driven high.                                                                                                                                                                                                              |

|           |          | In I <sup>2</sup> C mode, drive $\overline{\text{CS}}/\text{A0}$ high or low to set the I <sup>2</sup> C slave address. |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28        | B2       | SPI/I <sup>2</sup> C                                                                                                    | SPI or I <sup>2</sup> C Control Interface Selection Input. Connect SPI/I <sup>2</sup> C low for SPI operation. Connect SPI/I <sup>2</sup> C high for I <sup>2</sup> C operation.                                                                                                                                                                                                                      |

| UART INTI | ERFACE   |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16        | C6       | RX                                                                                                                      | C/Q Receiver Logic Output. RX is inverted relative to the logic state of C/Q by default. Set the INVCQ bit in the CQCONFIG register to set RX to the same logic state as C/Q. Connect RX to the RX input of the UART for IO-Link communication.                                                                                                                                                       |

| 17        | D6       | TXEN                                                                                                                    | C/Q Driver Enable Logic Input. Drive TXEN high and set the CQ_EN bit in the CONTROL register to enable the C/Q driver. Drive TXEN low to disable the C/Q driver. Connect TXEN to the RTS output of a microcontroller for IO-Link communication.                                                                                                                                                       |

| 18        | C5       | TX                                                                                                                      | C/Q Driver Logic Input. TX is inverted relative to the logic state of C/Q by default. Set the INVCQ bit in the CQCONTROL register to set TX to the same logic state as C/Q. Connect TX to the TX output of the UART for IO-Link communication.                                                                                                                                                        |

| CLOCK O   | JTPUT    |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23        | D3       | MCLK                                                                                                                    | Microcontroller Clock Output. Set the MCLK frequency by setting the CLKDIV bits in the CLKCONFIG register. The frequency of the MCLK signal can be trimmed by setting the CKTRIM bits in the CKTRIM register. Connect MCLK to an external microcontroller for comparison and trimming. The MCLK frequency is 3.686MHz by default but can be disabled or programmed to 14.74MHz, 7.37MHz, or 1.843MHz. |

## **Functional Diagrams**

#### **Detailed Description**

The MAX22513 industrial sensor output driver/IO-Link device transceiver integrates the high voltage functionality commonly found in sensors, including two 24V line drivers (C/Q and DO/DI), an integrated DC-DC buck regulator, 5V and 3.3V linear regulators, and a digital input (DO/DI). The MAX22513 can be configured and monitored with either an SPI or I<sup>2</sup>C serial bus.

#### 24V Interface (C/Q and DO/DI)

#### **Overcurrent Limiting**

The C/Q and DO/DI drivers feature a programmable current limit. Select the current limit for both drivers by setting the CL[1:0] bits in the CURRLIM register. Current limit thresholds can be set to 50mA (min), 100mA (min), 200mA (min), or 250mA (min). When the load attempts to draw more current than the current limit threshold setting, the C/Q and DO/DI driver actively limits the load current so a higher load current does not flow.

#### **Continuous Current Limiting with Blanking Time**

A programmable current limit blanking time allows the device to drive large capacitive or incandescent lamp loads without triggering a current limit fault. Select the blanking time by setting the CL\_BL[1:0] bits in the CURRLIM register. Set the CL\_BL[1:0] bits for a 128µs, 500µs, 1ms, or 5ms blanking time.