# **Low Power Analog Front End**

#### **■FEATURES**

Supply Voltage +2.4 to +3.6V Low Current Consumption 4µA (OPA,OPB),

150µA (ADC)

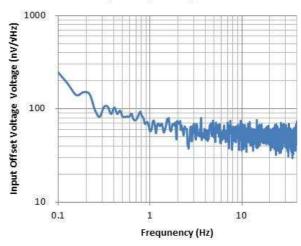

Low Noise Amplifier 1.3µVpp typ. (0.1 to 10Hz)

●Low Offset Voltage Amplifier 300µV max.

•RF immunity Amplifier

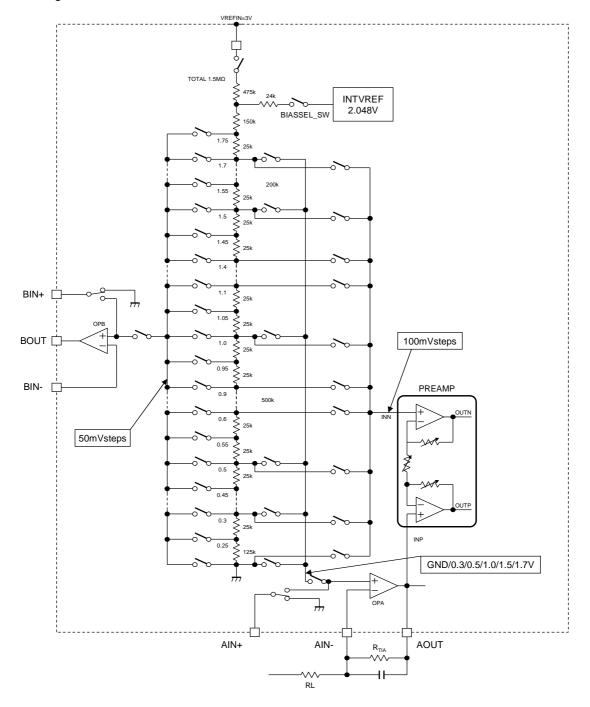

• Programmable Cell Bias Voltage

OPA: 0.3V to 1.7V (7 steps) OPB:

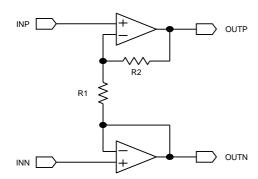

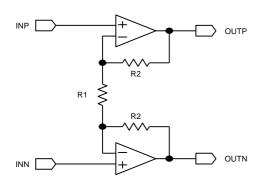

0.25V to 1.75V (50mV step) Programmable Gain Pre-Amplifier 1V/V to 8V/V

•High resolution Programmable Gain ADC

1V/V to 8V/V, 16-Bit (NFB), 32sps to 2k sps

System Calibration for offset & gain drift

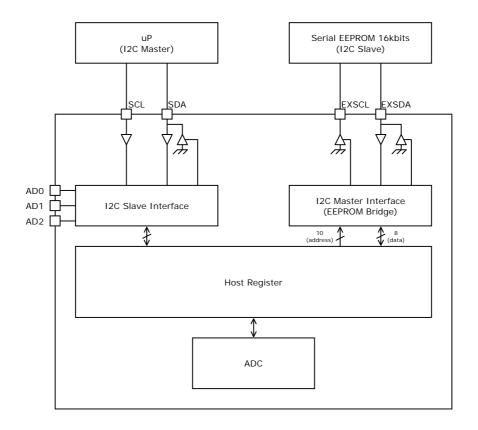

Control external EEPROM as a Master device

Ambient Operating Temperature -40°C to +85°C

I<sup>2</sup>C (3-Bit selectable slave address) Interface

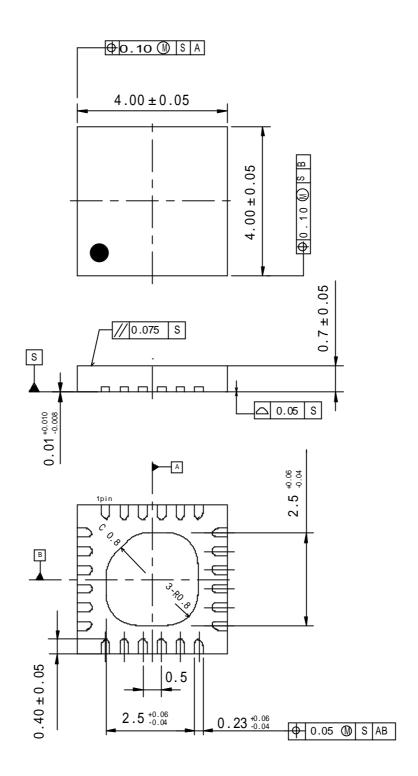

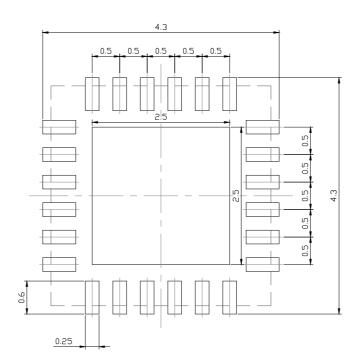

Package EQFN-24-LE (4mm x 4mm)

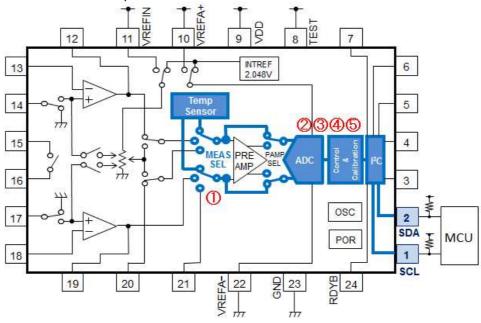

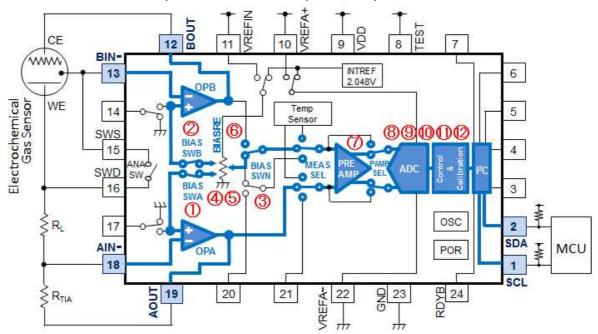

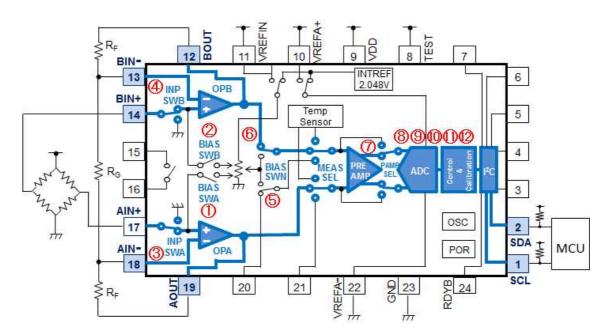

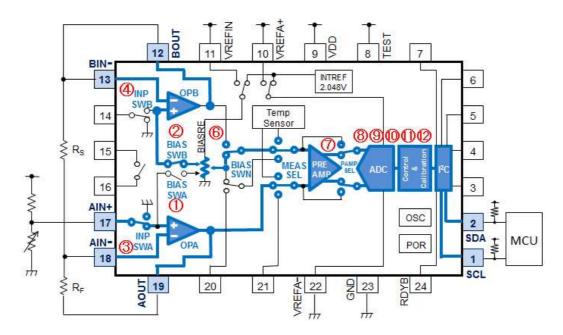

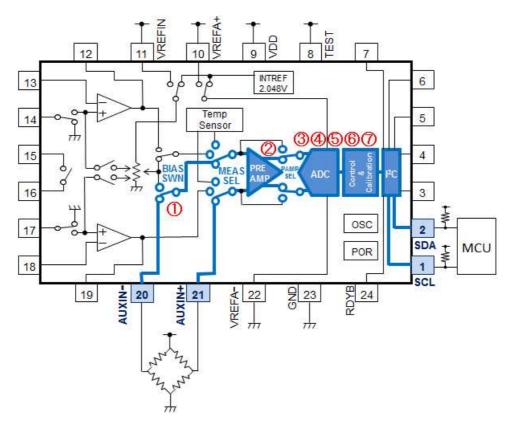

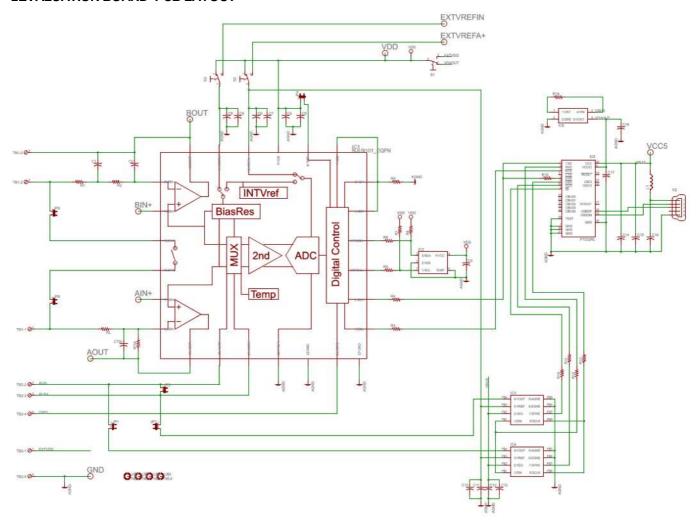

#### **■GENERAL DESCRIPTION**

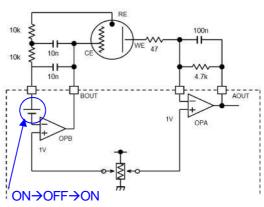

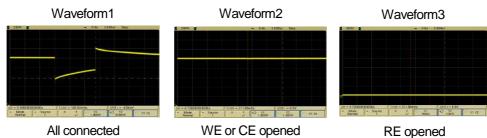

NJU9101 is a Low Power Analog Front End IC for use in micro-power sensing applications,

especially electrochemical sensors. It provides a complete signal processing solution between sensor and micro-processor as smart-sensor module.

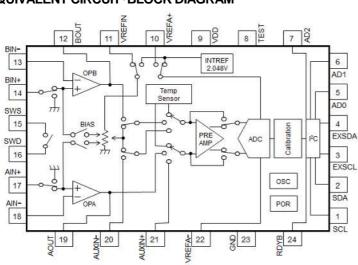

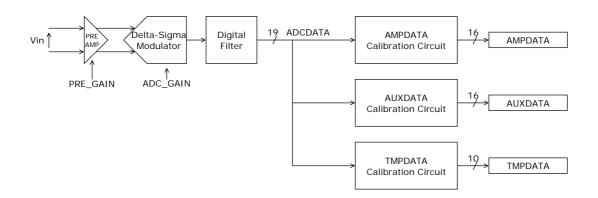

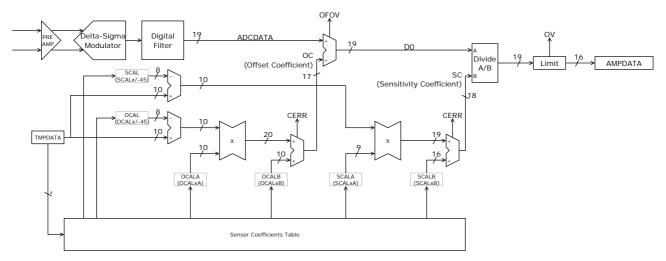

NJU9101 has 2 channel low power operational amplifiers. These amplifiers provide potentiostat and trans-impedance-amplifiers to constitute gas sensor systems. The NJU9101 has calibration circuit by using output data of built-in high precision ADC. It is suitable for temperature variation of sensor.

NJU9101 operates over voltage range of 2.4V to 3.6V. Total average current consumption can be less than 5μΑ.

### **■APPLICATION**

- Gas Monitor

- Blood Glucose Meter

- Current Sensing Systems

- Low Power Systems

- Photodiode Sensing Systems

- Portable equipment

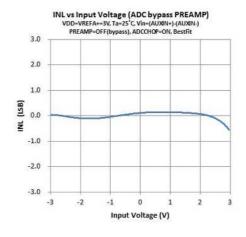

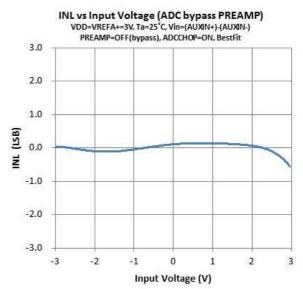

## ■INL vs Input Voltage (ADC)

### **■EQUIVALENT CIRCUIT · BLOCK DIAGRAM**

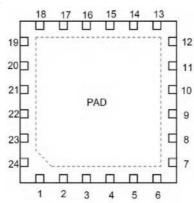

### **■PIN CONFIGURATION**

## EQFN-24-LE

| PIN NO. | SYMBOL   | DESC                                 | RIPTION                                      | Pin Type               |  |  |

|---------|----------|--------------------------------------|----------------------------------------------|------------------------|--|--|

| 1       | SCL      | l <sup>2</sup> C serial              | Digital Input                                |                        |  |  |

| 2       | SDA      | l <sup>2</sup> C serial dat          | a input / output                             | Digital Input / Output |  |  |

|         |          | `                                    | an pull-up resistor)                         | Digital Impat/ Odipat  |  |  |

| 3       | EXSCL    | '                                    | t for external EEPROM                        | Digital Output         |  |  |

|         | <u> </u> | ` -                                  | an pull-up register)                         | Digital Output         |  |  |

| 4       | EXSDA    | -                                    | tput for external EEPROM                     | Digital Input / Output |  |  |

|         |          | ` .                                  | an pull-up resister)                         |                        |  |  |

| 5       | AD0      | Chip address selection input 0       | Select 7 chip address from "000" to          | Digital Input          |  |  |

| 6       | AD1      | Chip address selection input 1       | "110". Do not select address "111",          | Digital Input          |  |  |

| 7       | AD2      | Chip address selection input 2       | which address is for production test purpose | Digital Input          |  |  |

| 8       | TEST     | TEST terminal (This terminal is used | d for production test. Connect to VDD)       | Analog Input           |  |  |

| 9       | VDD      | Voltage                              | e Supply                                     | Power Supply           |  |  |

| 10      | VREFA+   | Positive voltage ref                 | erence input for ADC                         | Analog Input           |  |  |

| 11      | VREFIN   | Voltage reference in                 | nput for Bias Registor                       | Analog Input           |  |  |

| 12      | BOUT     | Voltage output                       | for Bch. OpAmp                               | Analog Output          |  |  |

| 13      | BIN-     | Negative voltage ir                  | nput for Bch. OpAmp                          | Analog Input           |  |  |

| 14      | BIN+     | Positive voltage in                  | put for Bch. OpAmp                           | Analog Input           |  |  |

| 15      | SWS      | Switch So                            | ource Input 1                                | Swtich                 |  |  |

| 16      | SWD      | Switch D                             | rain Input 2                                 | Swtich                 |  |  |

| 17      | AIN+     | Positive voltage in                  | put for Ach. OpAmp                           | Analog Input           |  |  |

| 18      | AIN-     | Negative voltage ir                  | nput for Ach. OpAmp                          | Analog Input           |  |  |

| 19      | AOUT     | Voltage output                       | for Ach. OpAmp                               | Analog Output          |  |  |

| 20      | AUXIN-   | Auxiliary p                          | ositive input                                | Analog Input           |  |  |

| 21      | AUXIN+   | Auxiliary n                          | egative input                                | Analog Input           |  |  |

| 22      | VREFA-   | Negative voltage re                  | Negative voltage reference input for ADC     |                        |  |  |

|         | VINLI A  | (connect to GND                      | Analog Input                                 |                        |  |  |

| 23      | GND      | G                                    | GND                                          |                        |  |  |

| 24      | RDYB     | RDYB ou                              | RDYB output / GPIO                           |                        |  |  |

| PAD     | EXPPAD   | Exposed PAD on bac                   | kside (connect to GND)                       | GND                    |  |  |

### **■MARK INFORMATION**

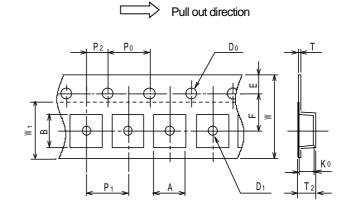

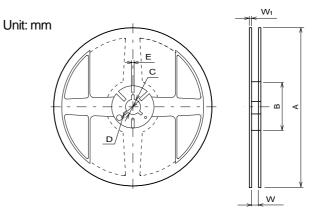

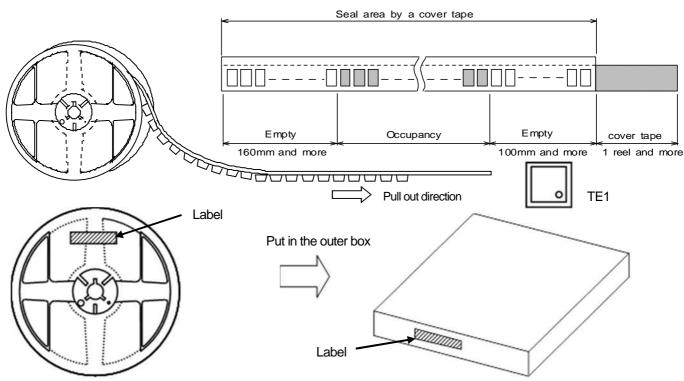

#### **■ORDERING INFORMATION**

| PART NUMBER | PACKAGE<br>OUTLINE | RoHS | HALOGEN-<br>FREE | TERMINAL<br>FINISH | MARKING | WEIGHT<br>(mg) | MOQ(pcs) |

|-------------|--------------------|------|------------------|--------------------|---------|----------------|----------|

| NJU9101MLE  | EQFN-24-LE         | 0    | 0                | Sn-2Bi             | 9101    | 31             | 1,000    |

#### **■ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                              | SYMBOL           | RATINGS                                                         | UNIT |

|--------------------------------------------------------|------------------|-----------------------------------------------------------------|------|

| Power Supply Voltage                                   | $V_{DD}$         | 5                                                               | V    |

| Analog Input Voltage <sup>(1)</sup>                    | $V_{IA}$         | -0.3 to $V_{DD}$ +0.3 not exceeding 5                           | V    |

| Digital Input Voltage                                  | $V_{\text{ID}}$  | -0.3 to 6                                                       | V    |

| Switch Input Voltage <sup>(1)</sup>                    | V <sub>IS</sub>  | -0.3 to $V_{DD}$ +0.3 not exceeding 5                           | V    |

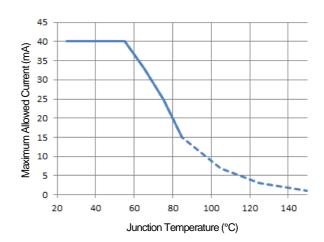

| On State Switch Current                                | I <sub>SO</sub>  | -40 to +40 <sup>(3)</sup>                                       | mA   |

| Power Dissipation(T <sub>a</sub> =25°C) <sup>(2)</sup> | P <sub>D</sub>   | 830 <sup>(4)</sup> / 2100 <sup>(5)</sup><br>(2-layer / 4-layer) | mW   |

| Operating Temperature Range                            | T <sub>opr</sub> | -40 to +85                                                      | °C   |

| Storage Temperature Range                              | T <sub>stg</sub> | -40 to +150                                                     | °C   |

- (1): The input pins have clamp diodes to the power supply pins. Limit the input current to 10mA or less whenever input signals exceed the power supply rail by 0.3V.

- (2): Power dissipation is the power that can be consumed by the IC at  $T_a$ =25°C, and is the typical measured value based on JEDEC condition. When using the IC over  $T_a$ =25°C subtract the value [mW/°C] =  $P_D/T_{st}$  max.- 25) per temperature.

- (3): Mounted on glass epoxy board.

(101.5x114.5x1.6mm: based on EIA/JEDEC standard, 2Layers FR-4, with Exposed Pad)

(4): Mounted on glass epoxy board.

(101.5×114.5×1.6mm: based on EIA/JEDEC standard, 4Layers FR-4, with Exposed Pad)

(For 4Layers: Applying 99.5×99.5mm inner Cu area and a thermal via hole to a board based on JEDEC standard JESD51-5)

### **■RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                   | SYMBOL           | RATINGS      | UNIT |

|-----------------------------|------------------|--------------|------|

| Power Supply Voltage        | $V_{DD}$         | +2.4 to +3.6 | V    |

| Operating Temperature Range | T <sub>opr</sub> | -40 to +85   | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -40 to +150  | °C   |

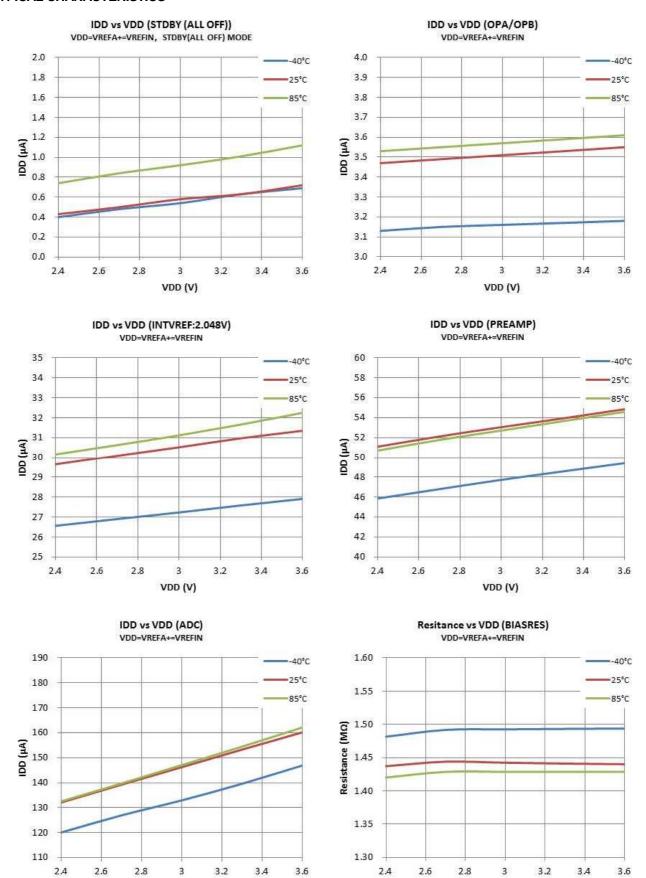

### **■ELECTRICAL CHARACTERISTICS**

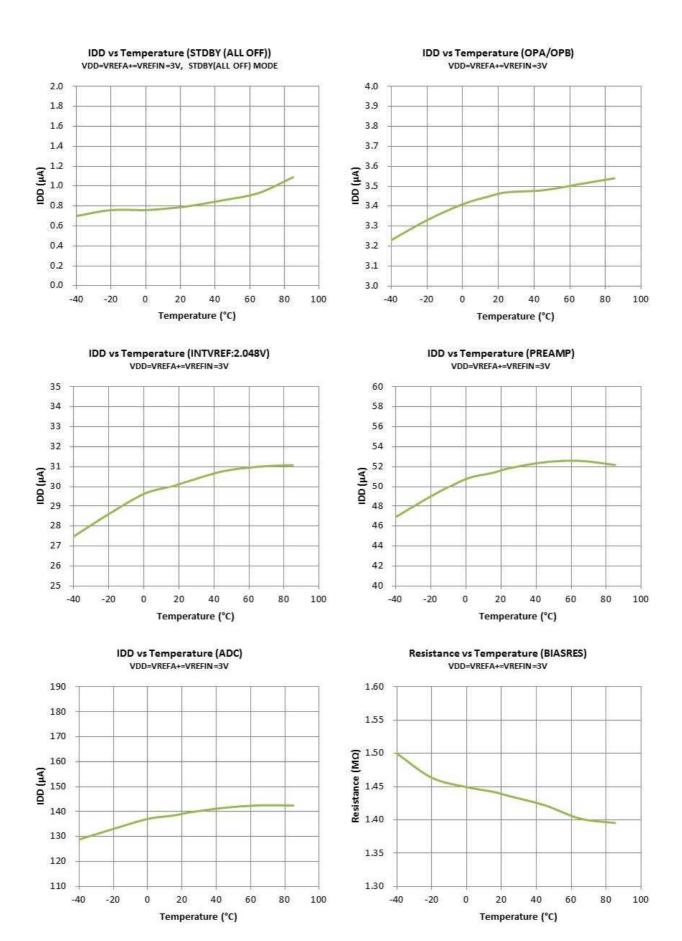

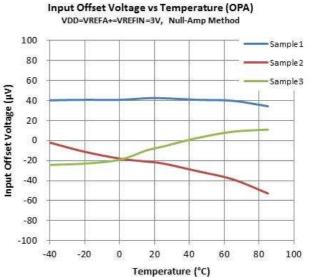

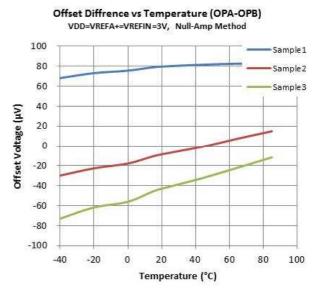

Unless otherwise specified, all limits ensured for  $T_a = 25$  °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$

| PARAMETER                       | SYMBOL                   | TEST CONDITION                          | MIN. | TYP. | MAX. | UNIT         |  |

|---------------------------------|--------------------------|-----------------------------------------|------|------|------|--------------|--|

| OPA, OPB                        |                          |                                         |      |      |      |              |  |

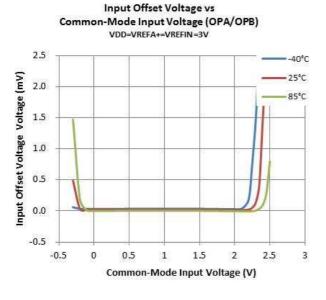

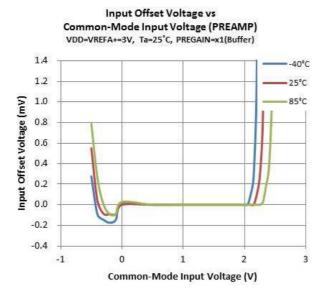

| Input Offset Voltage            | V <sub>IO</sub>          | $V_{ICM} = V_{DD}/2$ , $R_s = 50\Omega$ | -    | -    | ±300 | μV           |  |

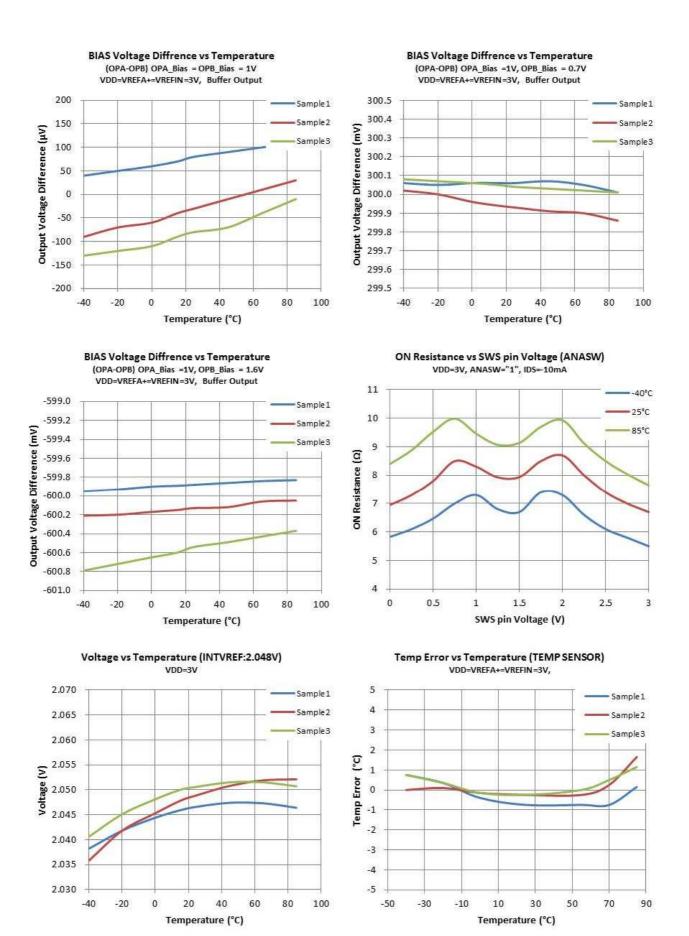

| Input Offset Voltage Drift      | $\Delta V_{IO}/\Delta T$ |                                         | -    | ±1   | -    | μV/°C        |  |

| Input Bias Current              | I <sub>B</sub>           |                                         | -    | 10   | -    | рА           |  |

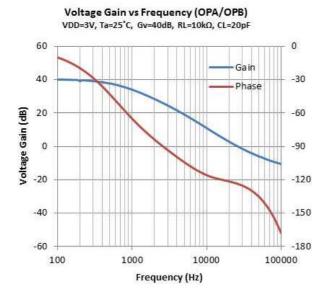

| Open Loop Gain                  | $A_V$                    |                                         | -    | 100  | -    | dB           |  |

| Common Mode Rejection Ratio     | CMR                      | $V_{ICM}$ = GND to 2V                   | 65   | 80   | -    | dB           |  |

| Common Mode Input Voltage Range | $V_{ICM}$                | CMR ≥ 65dB                              | GND  | -    | 2    | V            |  |

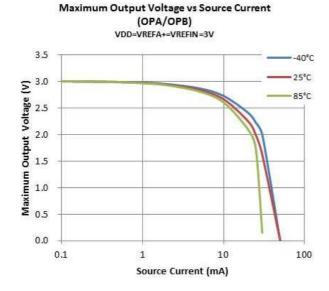

| Maximum Output Voltage          | $V_{OH}$                 | $I_{SOUECE} = 1mA$                      | 2.8  | 2.85 | -    | V            |  |

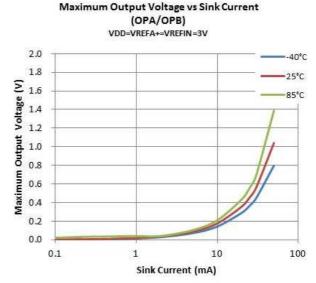

| waxiinum Ouput voitage          | $V_{OL}$                 | $I_{SINK} = 1mA$                        | -    | 0.15 | 0.2  | V            |  |

| Gain Band Width                 | GBW                      |                                         | -    | 30   | -    | kHz          |  |

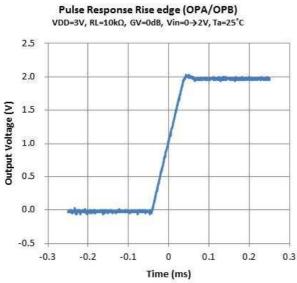

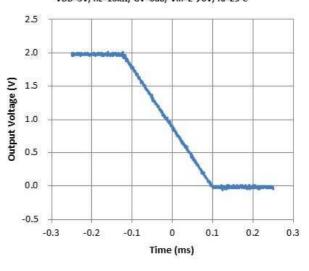

| Slew Rate                       | SR                       |                                         | -    | 0.01 | -    | V/µs         |  |

| Equivalent Input Noise Voltage  |                          | $f = 100Hz$ , $R_S = 50\Omega$          | -    | 50   | -    | nV/√Hz       |  |

| Equivalent input Noise voltage  | e <sub>n</sub>           | f = 0.1Hz to 10Hz                       | -    | 1.3  | -    | $\mu V_{pp}$ |  |

Unless otherwise specified, all limits ensured for  $T_a$  = 25°C,  $V_{DD}$  =  $V_{REFIN}$  =  $V_{REFA+}$  = 3V, ADC reference Voltage = External

| PARAMETER                        | SYMBOL                               | TEST CONDITION  | MIN. | TYP.           | MAX.          | UNIT  |  |

|----------------------------------|--------------------------------------|-----------------|------|----------------|---------------|-------|--|

|                                  | OPA, OPB with BIASRES (Potentiostat) |                 |      |                |               |       |  |

| OPA referred to OPB Input Offset | V <sub>IO1A-B</sub>                  | OPA BIAS = 1V   | _    | _              | ±0.6          | mV    |  |

| Voltage 1                        | V IO1A-B                             | OPB BIAS = 1V   |      |                | <u> -</u> 0.0 | 1111  |  |

| OPA referred to OPB Input Offset | $\Delta V_{\text{IO1A-B}}$           | OPA BIAS = 1V   | _    | ±2             | _             | μV/°C |  |

| Drift 1                          | / ΔT                                 | OPB BIAS = 1V   | _    | <del>1</del> 2 | _             | μν/ Ο |  |

| OPA referred to OPB Input Offset |                                      | OPA BIAS = 1V   | 295  | 300            | 305           | mV    |  |

| Voltage 2                        | V <sub>IO2A-B</sub>                  | OPB BIAS = 0.7V | 293  | 300            | 303           | IIIV  |  |

| OPA referred to OPB Input Offset | $\Delta V_{IO2A-B}$                  | OPA BIAS = 1V   |      | . 5            |               | \//oC |  |

| Drift 2                          | / ΔT                                 | OPB BIAS = 0.7V | _    | ±5             | -             | μV/°C |  |

| OPA referred to OPB Input Offset | \/                                   | OPA BIAS = 1V   | COE  | 600            | FOF           | m\/   |  |

| Voltage 3                        | V <sub>IO3A-B</sub>                  | OPB BIAS = 1.6V | -605 | -600           | -595          | mV    |  |

| OPA referred to OPB Input Offset | $\Delta V_{IO3A-B}$                  | OPA BIAS = 1V   |      | .0             |               | \//oC |  |

| Drift 3                          | / ΔT                                 | OPB BIAS = 1.6V | -    | ±8             | -             | μV/°C |  |

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$

| oriodo ou for vido opodifica, all littilo oficaroc | 1101 Ta - 20 V     | O, TOD TREFIN TREFAT OT                              |      |      |      |      |

|----------------------------------------------------|--------------------|------------------------------------------------------|------|------|------|------|

| PARAMETER                                          | SYMBOL             | TEST CONDITION                                       | MIN. | TYP. | MAX. | UNIT |

| Analog Switch (ANASW)                              |                    |                                                      |      |      |      |      |

| On State Resistance                                | R <sub>ON</sub>    | Analog Switch = ON $I_{DS}$ = -10mA                  |      | 10   | 30   | Ω    |

| Off Leakage Current                                | I <sub>LOFFD</sub> | Analog Switch = OFF $V_{SWS}=2V/1V,$ $V_{SWD}=1V/2V$ | 1    | ±1   | 1    | nA   |

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$ , Temperature Input Mode

| PARAMETER                      | SYMBOL            | TEST CONDITION          | MIN. | TYP. | MAX. | UNIT |

|--------------------------------|-------------------|-------------------------|------|------|------|------|

| Temperature Sensor             |                   |                         |      |      |      |      |

| Temperature Accuracy (Error) 1 | T <sub>ACC1</sub> | $T_a = 25$ °C           | -    | ±1   | ±5   | °C   |

| Temperature Accuracy (Error) 2 | T <sub>ACC2</sub> | $T_a = -40$ °C to +85°C | -    | ±3   | -    | °C   |

| Temperature Resolution         | T <sub>RES</sub>  |                         | -    | 0.25 | -    | °C   |

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = 3V$

| PARAMETER                  | SYMBOL                         | TEST CONDITION                                      | MIN.  | TYP.  | MAX.  | UNIT   |

|----------------------------|--------------------------------|-----------------------------------------------------|-------|-------|-------|--------|

| Internal Reference         |                                |                                                     |       |       |       |        |

| Internal Reference Voltage | $V_{IREF}$                     | ±1%                                                 | 2.028 | 2.048 | 2.068 | V      |

| Internal Reference Drift   | $\Delta V_{IREF}$ / $\Delta T$ | $T_a = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | -     | 30    | -     | ppm/°C |

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$ , Auxiliary Differential Input Mode

| REFIN REFAT OUT TO THE STATE OF |                    |                           |       |      |                    |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|-------|------|--------------------|------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYMBOL             | TEST CONDITION            | MIN.  | TYP. | MAX.               | UNIT |

| PREAMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                           |       |      |                    |      |

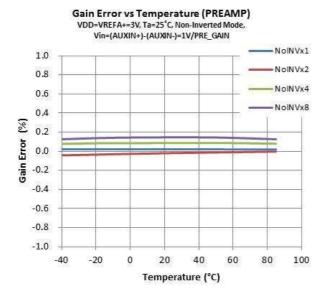

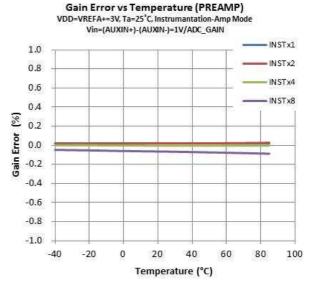

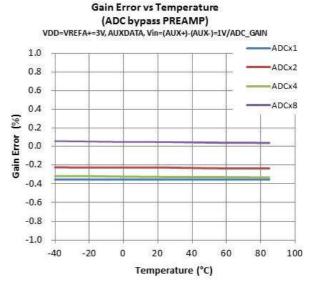

| PREAMP Gain Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | G                  | PREAMP Gain =             |       | ±0.1 | -                  | %    |

| FREAIVIF GAILI EITOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $G_{ACCP}$         | 1V/1V to 8V/V             | -     | ±0.1 |                    | /0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | PREAMP Gain = 1V/V        |       |      |                    |      |

| PREAMP Common Mode Rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CMR <sub>PRE</sub> | AUXIN+ = AUXIN- =         | 70    | 90   | -                  | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | GND+0.05 to $V_{DD}$ -1   |       |      |                    |      |

| PREAMP Common Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \/                 | PREAMP Gain = 1V/V        | GND   |      | \/ 1               | \/   |

| Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>ICMP</sub>  | CMR <sub>PRE</sub> ≥ 70dB | +0.05 | 1    | V <sub>CC</sub> -1 | ٧    |

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$ , Auxiliary Input Mode ADC Chopping = ON, ADC Reference Voltage = External, ADC Gain = 1V/V, ADC Decimation Ratio = "320"

| PARAMETER                              | SYMBOL             | TEST CONDITION                            | MIN. | TYP.              | MAX.            | UNIT  |

|----------------------------------------|--------------------|-------------------------------------------|------|-------------------|-----------------|-------|

| ADC                                    |                    |                                           |      |                   | •               |       |

| Resolution                             | N                  | No missing code <sup>(6)</sup>            | 16   | -                 | -               | Bit   |

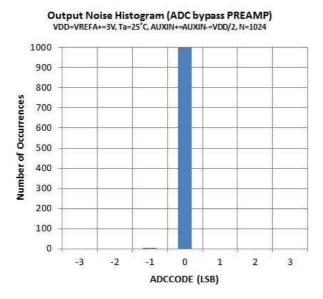

| Noise Free Bit                         | NFB                |                                           | -    | 16                | -               | Bit   |

| Conversion Time                        | DR                 | See p.22 "ADC Conversion Time"            | 1    | -                 | -               | SPS   |

| Output Noise                           | $V_{nADC}$         | VREFA+=3V                                 | 1    | 13.9              | -               | μVrms |

| Integral Non Linearity                 | INL                |                                           | -    | ±1                | -               | LSB   |

| Gain Error                             |                    | ADC Gain =<br>1V/1V to 8V/1V              | -    | ±0.1              | -               | %     |

| Offset Error                           |                    | AUXIN+= AUXIN-=<br>V <sub>DD</sub> /2     | 1    | ±1                | -               | LSB   |

| Differential Input Voltage Range       | V <sub>IDADC</sub> | V <sub>REF</sub> =<br> (VREFA+)-(VREFA-)  | ı    | ±V <sub>REF</sub> | -               | V     |

| ADC Common Mode Rejection              | CMR <sub>ADC</sub> | AUXIN+= AUXIN-=<br>GND to V <sub>DD</sub> | 80   | 90                | -               | dB    |

| ADC Common Mode Input Voltage<br>Range | V <sub>ICADC</sub> | CMR <sub>ADC</sub> ≥80dB                  | GND  | -                 | V <sub>DD</sub> | V     |

(6) This Parameter is not production tested, please refer Typical Characteristics.

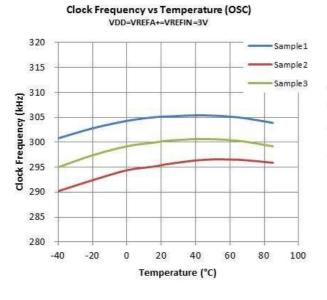

Unless otherwise specified, all limits ensured for  $T_a = 25$ °C,  $V_{DD} = V_{REFIN} = V_{REFA+} = 3V$

| PARAMETER          | SYMBOL            | TEST CONDITION                         | MIN. | TYP. | MAX. | UNIT |

|--------------------|-------------------|----------------------------------------|------|------|------|------|

| Power Supply / OSC |                   |                                        |      |      |      |      |

| Voltage Range      | $V_{DD}$          |                                        | 2.4  | -    | 3.6  | V    |

| Bias Resistance    | R <sub>BIAS</sub> |                                        | -    | 1.5  | -    | ΜΩ   |

| Supply Current 1   | I <sub>DD1</sub>  | All Circuit Block Off                  | -    | 0.5  | 1    | μA   |

| Supply Current 2   | I <sub>DD2</sub>  | OPA, OPB                               | -    | 4    | 5.5  | μA   |

| Supply Current 3   | I <sub>DD3</sub>  | Internal Reference<br>Voltage (2.048V) | -    | 31   | 40   | μΑ   |

| Supply Current 4   | I <sub>DD4</sub>  | PREAMP                                 | -    | 55   | 75   | μA   |

| Supply Current 5   | I <sub>DD5</sub>  | ADC                                    | -    | 150  | 200  | μA   |

| OSC Frequency      | f <sub>OSC</sub>  | ±10%                                   | 276  | 307  | 338  | kHz  |

# ■CHARACTERISTICS OF I/O STAGES FOR I<sup>2</sup>C-BUS Compatible (SDA, SCL)

I<sup>2</sup>C BUS Load Conditions

STANDARD MODE: Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 200pF (Connected to GND) FASE MODE: Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 50pF (Connected to GND)

| PARAMETER                                        | SYM             | SYM Standard Mode |      |             |      | Fast Mod | ast Mode |      |  |

|--------------------------------------------------|-----------------|-------------------|------|-------------|------|----------|----------|------|--|

| PARAIVIETER                                      | BOL             | MIN.              | TYP. | MAX.        | MIN. | TYP.     | MAX.     | UNIT |  |

| Low Level Input Voltage                          | $V_{IL}$        | 0.0               | -    | $0.3V_{DD}$ | 0.0  | -        | 1.5      | V    |  |

| High Level Input Voltage                         | V <sub>IH</sub> | $0.7V_{DD}$       | -    | 5.5         | 2.7  | -        | 5.5      | V    |  |

| Low Level Output Voltage                         | V <sub>OL</sub> | 0                 |      | 0.4         | 0    | _        | 0.4      | V    |  |

| (3mA at SDA pin)                                 | V OL            | U                 | _    | 0.4         | U    | _        | 0.4      |      |  |

| Input current each I/O pin with an input voltage |                 | -10               |      | 10          | -10  | _        | 10       |      |  |

| between $0.1V_{DD}$ and $0.9V_{DD}$ max.         | li<br>I         | -10               | _    | 10          | -10  | _        | 10       | μΑ   |  |

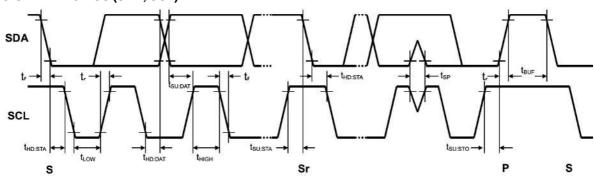

# ■CHARACTERISTICS OF BUS LINES (SDA, SCL) FOR I<sup>2</sup>C-BUS Compatible Devices

I<sup>2</sup>C BUS Load Conditions

STANDARD MODE: Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 200pF (Connected to GND) FASE MODE: Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 50pF (Connected to GND)

| DADAMETED                                        | SYM                 | Sta  | ndard Mo | ode  |      | Fast Mod | de   | LINUT |

|--------------------------------------------------|---------------------|------|----------|------|------|----------|------|-------|

| PARAMETER                                        | BOL                 | MIN. | TYP.     | MAX. | MIN. | TYP.     | MAX. | UNIT  |

| SCL clock frequency                              | f <sub>SCL</sub>    | 10   | -        | 100  | 10   | -        | 400  | kHz   |

| Hold time (repeated) START condition             | t <sub>HD:STA</sub> | 4.0  | -        | -    | 0.6  | -        | 1    | μs    |

| Low period of the SCL clock                      | t <sub>LOW</sub>    | 4.7  | -        | -    | 1.3  | -        | 1    | μs    |

| High period of the SCL clock                     | t <sub>HIGH</sub>   | 4.0  | -        | -    | 0.6  | -        | 1    | μs    |

| Set-up time for a repeated START condition       | t <sub>SU:STA</sub> | 4.7  | -        | -    | 0.6  | -        | -    | μs    |

| Data hold time                                   | t <sub>HD:DAT</sub> | 0    | -        | -    | 0    | -        | 1    | μs    |

| Data set-up time                                 | t <sub>SU:DAT</sub> | 250  | -        | -    | 100  | -        | 1    | ns    |

| Rise time of both SDA and SCL signals            | t <sub>r</sub>      | -    | -        | 1000 | -    | -        | 300  | ns    |

| Fall time of both SDA and SCL signals            | t <sub>f</sub>      | -    | -        | 300  | -    | -        | 300  | ns    |

| Set-up time for STOP condition                   | t <sub>SU:STO</sub> | 4.0  | -        | -    | 0.6  | -        | -    | μs    |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    | 4.7  | -        | -    | 1.3  | -        | -    | μs    |

| Capacitive load for each bus line                | C <sub>b</sub>      | -    | -        | 400  | -    | -        | 400  | pF    |

| Noise margin at the Low Level                    | $V_{nL}$            | 0.5  | -        | -    | 0.5  | -        |      | V     |

| Noise margin at the High Level                   | $V_{nH}$            | 1    | -        | -    | 1    | -        | -    | V     |

$C_{\mbox{\scriptsize b}}$ : Total capacitance of one bus line in pF.

# ■TIMING ON THE I<sup>2</sup>C BUS (SDA, SCL)

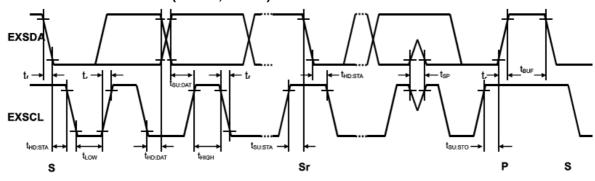

# ■CHARACTERISTICS OF I/O STAGES FOR EEPROM I<sup>2</sup>C-BUS (EXSDA, EXSCL)

I<sup>2</sup>C BUS Load Conditions

Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 50pF (Connected to GND)

| PARAMETER                                        | SYMBOL          | MIN.        | TYP. | MAX.        | UNIT |

|--------------------------------------------------|-----------------|-------------|------|-------------|------|

| Low Level Input Voltage                          | $V_{IL}$        | 0.0         | 1    | $0.3V_{DD}$ | V    |

| High Level Input Voltage                         | V <sub>IH</sub> | $0.7V_{DD}$ | 1    | -           | V    |

| Low Level Output Voltage                         | \/              | 0           | _    | 0.4         | V    |

| (3mA at SDA pin)                                 | V <sub>OL</sub> | O           |      | 0.4         |      |

| Input current each I/O pin with an input         | ı               | 10          |      | 10          |      |

| voltage between $0.1V_{DD}$ and $0.9V_{DD}$ max. | l <sub>i</sub>  | -10         | -    | 10          | μΑ   |

### ■CHARACTERISTICS OF BUS LINES (EXSDA, EXSCL)

I<sup>2</sup>C BUS Load Conditions

Pull up resistance  $4k\Omega$  (Connected to  $V_{DD}$ ), Load capacitance 50pF (Connected to GND)

| ,                                                |                     |      | `     | ,     |      |

|--------------------------------------------------|---------------------|------|-------|-------|------|

| PARAMETER                                        | SYMBOL              | MIN. | TYP.  | MAX.  | UNIT |

| EXSCL clock frequency                            | f <sub>SCL</sub>    | 92   | 102.3 | 112.7 | kHz  |

| Hold time (repeat) START condition               | t <sub>HD:STA</sub> | 7.2  | 6.5   | 5.9   | μs   |

| Low period of the EXSCL clock                    | t <sub>LOW</sub>    | 7.2  | 6.5   | 5.9   | μs   |

| High period of the EXSCL clock                   | t <sub>HIGH</sub>   | 3.6  | 3.3   | 3.0   | μs   |

| Set-up time for a repeated START condition       | t <sub>SU:STA</sub> | 7.2  | 6.5   | 5.9   | μs   |

| Data hold time (EXSDA input)                     | t <sub>HD:DAT</sub> | 0    | -     | -     | μs   |

| Data hold time (EXSDA output)                    | t <sub>HD:DAT</sub> | 7.2  | 6.5   | 5.9   | μs   |

| Data Set-up time (EXSDA input)                   | t <sub>SU:DAT</sub> | 0    | -     | -     | μs   |

| Data Set-up time (EXSDA output)                  | t <sub>SU:DAT</sub> | 7.2  | 6.5   | 5.9   | μs   |

| Rise time of both SDA and SCL signals            | t <sub>r</sub>      | -    | -     | 300   | ns   |

| Fall time of SDA and SCL signals                 | t <sub>f</sub>      | -    | -     | 300   | ns   |

| Set-up time for STOP condition                   | t <sub>su:sto</sub> | 7.2  | 6.5   | 5.9   | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    | 7.2  | 6.5   | 5.9   | μs   |

| Capacitive load for each bus line                | C <sub>b</sub>      | -    | -     | 400   | pF   |

| Noise margin at the Low level                    | V <sub>nL</sub>     | 0.5  | -     | -     | V    |

| Noise margin at the High level                   | $V_{nH}$            | 1    | -     | -     | V    |

C<sub>b</sub>: total capacitance of one bus line in pF.

## ■TIMING ON THE EEPROM I2C BUS (EXSDA, EXSCL)

### **■REGISTER DESCRIPTION**

NJU9101 has register (list shown below) which can access it through I<sup>2</sup>C bus.

It can control the external EEPROM address corresponding to each register address from NJU9101.

| REGISTER | EEPROM  | REGISTER  |               |                          |        | Е          | П         |                |            |            |  |

|----------|---------|-----------|---------------|--------------------------|--------|------------|-----------|----------------|------------|------------|--|

| ADDRESS  | ADDRESS | NAME      | D7            | D6                       | D5     | D4         | D3        | D2             | D1         | D0         |  |

| 0x00     | -       | CTRL      | -             | RST                      | SENS   | 6CK [1:0]  | MEAS      | MEAS_S         | SEL [1:0]  | MEAS_SC    |  |

| 0x01     | -       | STATUS    | -             | -                        | BOOT   | CLKRUN     | RDYB      | OV             | CERR       | OFOV       |  |

| 0x02     | -       | AMPDATA0  |               | •                        |        | AMPDA      | TA [15:8] |                | •          |            |  |

| 0x03     | -       | AMPDATA1  |               |                          |        | AMPD/      | ATA [7:0] |                |            |            |  |

| 0x04     | -       | AUXDATA0  |               |                          |        | AUXDA      | TA [15:8] |                |            |            |  |

| 0x05     | -       | AUXDATA1  |               |                          |        | AUXDA      | ATA [7:0] |                |            |            |  |

| 0x06     | -       | TMPDATA0  |               |                          |        | TMPDA      | ATA [9:2] |                |            |            |  |

| 0x07     | -       | TMPDATA1  | TMPDA         | ATA [1:0]                | -      | -          | -         | -              | -          | -          |  |

| 0x08     | -       | ID        |               |                          |        | ID         | [7:0]     |                |            |            |  |

| 0x09     | -       | ROMADR0   | -             | -                        | -      | -          | -         |                | ROMADR [10 | :8]        |  |

| 0x0A     | -       | ROMADR1   |               |                          |        | ROMA       | DR [7:0]  |                |            |            |  |

| 0x0B     | -       | ROMDATA   |               |                          |        | ROMDA      | ATA [7:0] |                |            |            |  |

| 0x0C     | -       | ROMCTRL   | -             | -                        | ROMERR | ROMBUSY    | ROMSTOP   | ROMACT         | ROMN       | /ODE [1:0] |  |

| 0x0D     | -       | TEST      |               |                          |        | TES        | Γ [7:0]   |                |            |            |  |

| 0x0E     | 0x000   | ANAGAIN   | -             | -                        | -      | -          | PRE_G     | AIN [1:0]      | ADC_       | GAIN [1:0] |  |

| 0x0F     | 0x001   | BLKCONN0  | -             | BIASSWA BIASSWB PRE_BIAS |        |            |           |                |            |            |  |

| 0x10     | 0x002   | BLKCONN1  |               | OPA_BIAS [2:0            | )]     |            | (         | OPB_BIAS [4:0] |            |            |  |

| 0x11     | 0x003   | BLKCONN2  | PREMODE       | INPSWA                   | INPSWB | ANASW      | BIASSWN   | PAMPSEL        | BIASSEL    | VREFSEL    |  |

| 0x12     | 0x004   | BLKCTRL   |               |                          |        | BLKCT      | RL [7:0]  |                |            |            |  |

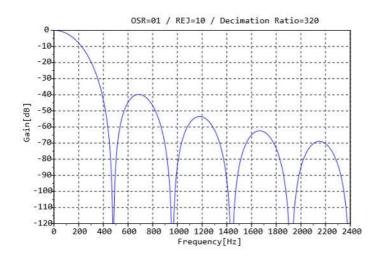

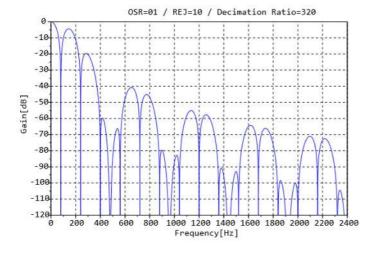

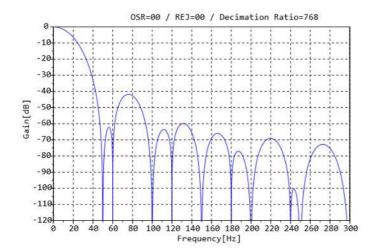

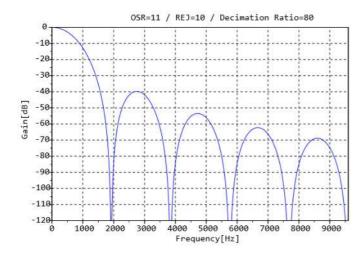

| 0x13     | 0x005   | ADCCONV   | -             | ADCCHOP                  | CLKE   | OIV [1:0]  | REJ       | [1:0]          | 08         | SR [1:0]   |  |

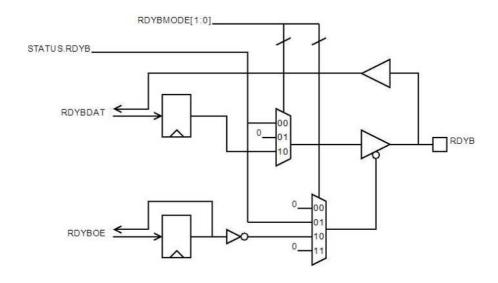

| 0x14     | 0x006   | SYSPRESET | RDYBOE        | RDYBDAT                  | RDYBM  | 10DE [1:0] | -         | -              | -          | AMPAUX     |  |

| 0x15     | 0x007   | SCAL1A0   | -             | -                        | -      | -          | -         | -              | -          | SCAL1A [8] |  |

| 0x16     | 0x008   | SCAL1A1   |               |                          |        | SCAL       | 1A [7:0]  |                |            |            |  |

| 0x17     | 0x009   | SCAL2A0   | -             | -                        | -      | -          | •         | -              | -          | SCAL2A [8] |  |

| 0x18     | 0x00A   | SCAL2A1   |               |                          |        | SCAL       | 2A [7:0]  |                |            |            |  |

| 0x19     | 0x00B   | SCAL3A0   | -             | -                        | -      | -          | -         | -              | -          | SCAL3A [8] |  |

| 0x1A     | 0x00C   | SCAL3A1   |               |                          |        | SCAL       | 3A [7:0]  |                |            |            |  |

| 0x1B     | 0x00D   | SCAL4A0   | -             | -                        | -      | -          | 1         | -              | -          | SCAL4A [8] |  |

| 0x1C     | 0x00E   | SCAL4A1   |               |                          |        | SCAL       | 4A [7:0]  |                |            |            |  |

| 0x1D     | 0x00F   | SCAL1B0   |               |                          |        | SCAL1      | B [15:8]  |                |            |            |  |

| 0x1E     | 0x010   | SCAL1B1   |               |                          |        | SCAL       | 1B [7:0]  |                |            |            |  |

| 0x1F     | 0x011   | SCAL2B0   |               | SCAL2B [15:8]            |        |            |           |                |            |            |  |

| 0x20     | 0x012   | SCAL2B1   | SCAL2B [7:0]  |                          |        |            |           |                |            |            |  |

| 0x21     | 0x013   | SCAL3B0   |               |                          |        | SCAL       | BB [15:8] |                |            |            |  |

| 0x22     | 0x014   | SCAL3B1   | SCAL3B [7:0]  |                          |        |            |           |                |            |            |  |

| 0x23     | 0x015   | SCAL4B0   | SCAL4B [15:8] |                          |        |            |           |                |            |            |  |

| 0x24     | 0x016   | SCAL4B1   | SCAL4B [7:0]  |                          |        |            |           |                |            |            |  |

| 0x25     | 0x017   | OCAL1A0   | OCAL1A [      |                          |        |            |           |                | L1A [9:8]  |            |  |

| 0x26     | 0x018   | OCAL1A1   |               | •                        |        | OCAL       | 1A [7:0]  |                | •          |            |  |

| 0x27 | 0x019 | OCAL2A0  | - | -               | - | -                 | -             | - | OCAL2A [9:8] |  |  |

|------|-------|----------|---|-----------------|---|-------------------|---------------|---|--------------|--|--|

| 0x28 | 0x01A | OCAL2A1  |   | OCAL2A [7:0]    |   |                   |               |   |              |  |  |

| 0x29 | 0x01B | OCAL3A0  | - | -               | - | -                 | -             | - | OCAL3A [9:8] |  |  |

| 0x2A | 0x01C | OCAL3A1  |   | OCAL3A [7:0]    |   |                   |               |   |              |  |  |

| 0x2B | 0x01D | OCAL4A0  | - | OCAL4A [        |   |                   |               |   |              |  |  |

| 0x2C | 0x01E | OCAL4A1  |   |                 |   | OCAL <sup>4</sup> | 4A [7:0]      |   | •            |  |  |

| 0x2D | 0x01F | OCAL1B0  | - |                 |   |                   | OCAL1B [14:8] |   |              |  |  |

| 0x2E | 0x020 | OCAL1B1  |   |                 |   | OCAL              | 1B [7:0]      |   |              |  |  |

| 0x2F | 0x021 | OCAL2B0  | - |                 |   |                   | OCAL2B [14:8] |   |              |  |  |

| 0x30 | 0x022 | OCAL2B1  |   |                 |   | OCAL              | 2B [7:0]      |   |              |  |  |

| 0x31 | 0x023 | OCAL3B0  | - |                 |   |                   | OCAL3B [14:8] |   |              |  |  |

| 0x32 | 0x024 | OCAL3B1  |   |                 |   | OCAL              | 3B [7:0]      |   |              |  |  |

| 0x33 | 0x025 | OCAL4B0  | - |                 |   |                   | OCAL4B [14:8] |   |              |  |  |

| 0x34 | 0x026 | OCAL4B1  |   |                 |   | OCAL              | 4B [7:0]      |   |              |  |  |

| 0x35 | 0x027 | SCAL1    |   |                 |   | SCAL              | .1 [7:0]      |   |              |  |  |

| 0x36 | 0x028 | SCAL2    |   |                 |   | SCAL              | 2 [7:0]       |   |              |  |  |

| 0x37 | 0x029 | SCAL3    |   |                 |   | SCAL              | .3 [7:0]      |   |              |  |  |

| 0x38 | 0x02A | OCAL1    |   |                 |   | OCAL              | 1 [7:0]       |   |              |  |  |

| 0x39 | 0x02B | OCAL2    |   |                 |   | OCAL              | 2 [7:0]       |   |              |  |  |

| 0x3A | 0x02C | OCAL3    |   |                 |   | OCAL              | .3 [7:0]      |   |              |  |  |

| 0x3B | 0x02D | AUXSCAL0 |   | AUX_SCAL [15:8] |   |                   |               |   |              |  |  |

| 0x3C | 0x02E | AUXSCAL1 |   | AUX_SCAL [7:0]  |   |                   |               |   |              |  |  |

| 0x3D | 0x02F | AUXOCAL0 |   | AUX_OCAL [15:8] |   |                   |               |   |              |  |  |

| 0x3E | 0x030 | AUXOCAL1 |   | AUX_OCAL [7:0]  |   |                   |               |   |              |  |  |

| 0x3F | -     | CHKSUM   |   |                 |   | CHKSL             | JM [7:0]      |   |              |  |  |

## **■EVERY REGISTER DESCRIPTION**

**CTRL** Register

Register Address: 0x00, EEPROM Address: -

|          | CTRL |     |              |            |      |                |    |         |  |  |

|----------|------|-----|--------------|------------|------|----------------|----|---------|--|--|

| BIT      | [7]  | [6] | [5] [4]      |            | [3]  | [2] [1]        |    | [0]     |  |  |

| BIT NAME | -    | RST | SENSCK [1:0] |            | MEAS | MEAS_SEL [1:0] |    | MEAS_SC |  |  |

| R/W      | -    | WS  | R'           | RW         |      | RW             |    | RW      |  |  |

| RESET    | -    | -   | 0:           | <b>(</b> 0 | 0    | 0              | x0 | 0       |  |  |

| BIT   | BIT NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]   | RST      | Write Software Reset. When read this bit, always return "0".  0: No effect 1: Reset                                                                                                                                                                                                                                                                                                                                                                                          |

| [5:4] | SENSCK   | Change offset voltage of OPB to check sensor diagnostic.  00: OFF (No change) 01: Plus Offset (Change Offset Voltage ≈ +5.0mV) 10: Minus Offset (Change Offset Voltage ≈ -5.0mV) 11: Reserve                                                                                                                                                                                                                                                                                 |

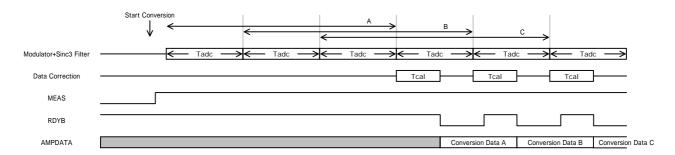

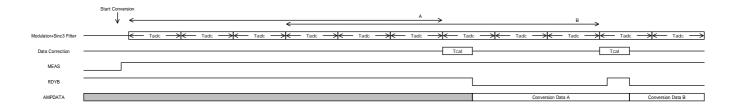

| [3]   | MEAS     | Measurement Switch When write "1", ADC conversion starts. When read this bit, returns "1" in case of under conversion, "0" in case of idle condition. When select "Single Conversion" mode, this bit is set to "0" automatically after conversion completion. When select "Continuous Conversion" mode and write "0", ADC conversion stop and return to an idol state.  O: Measurement OFF (Operating condition of this chip follows "BLKCTRL" condition)  1: Measurement ON |

| [2:1] | MEAS_SEL | Measurement Mode Selection.  00: Temperature sensor input mode 01: Amplifier input mode 10: Auxiliary input mode 11: Reserve                                                                                                                                                                                                                                                                                                                                                 |

| [0]   | MEAS_SC  | Measurement Mode for ADC  0: Single Conversion  1: Continuous Conversion                                                                                                                                                                                                                                                                                                                                                                                                     |

## **STATUS Register**

Register Address: 0x01, EEPROM Address: -

|          | STATUS |     |      |        |      |     |      |      |  |

|----------|--------|-----|------|--------|------|-----|------|------|--|

| BIT      | [7]    | [6] | [5]  | [4]    | [3]  | [2] | [1]  | [0]  |  |

| BIT NAME | -      | ı   | BOOT | CLKRUN | RDYB | OV  | CERR | OFOV |  |

| R/W      | -      | -   | R    | R      | R    | R   | R    | R    |  |

| RESET    | -      | -   | 1    | -      | 1    | 0   | 0    | 0    |  |

| BIT | BIT NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5] | воот     | Booting flag for IC.  NJU9101 reads initial register value from external EEPROM as booting.  This bit returns "1" until the reading of the initial register value is completed from start.  0: Completion of booting  1: Under booting                                                                                                                                                                                                                                                     |

| [4] | CLKRUN   | System Clock Condition.  0: System Clock is sleeping 1: System Clock is operating                                                                                                                                                                                                                                                                                                                                                                                                          |

| [3] | RDYB     | Data Ready Flag. When conversion data is updated, this bit is cleared to "0".  When either "AMPDATA0", "AUXDATA0", or "TMPDATA" is read, this bit is set to "1".  0: New ADC data is ready  1: New ADC data is not ready                                                                                                                                                                                                                                                                   |

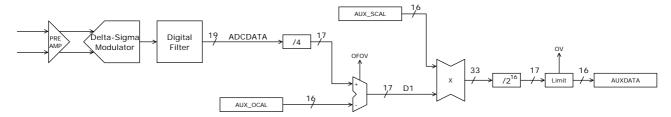

| [2] | OV       | Overflow flag in sensitivity calibration of ADC output data.  When over flow is occurred in sensitivity calibration of ADC conversion data, this bit is set to "1". When this bit is "1", ADC output data ("AMPDATA" or "AUXDATA") is set to 0x7FFF (positive over flow) or 0x8000 (negative over flow). When either "AMPDATA0", "AUXDATA0", or "TMPDATA" is read, this bit is cleared to "0".  0: ADC conversion data is valid 1: ADC conversion data is over flow (set 0x7FFF or 0x8000) |

| [1] | CERR     | Overflow flag in calibration coefficient data.  When over flow is occurred in setting of calibration coefficient data, this bit is set to "1". In case of "1", ADC output data is invalid value.  When either "AMPDATAO", "AUXDATAO" or "TMPDATA" is read, this bit is cleared to "0".  0: No overflow in calibration coefficient calculation  1: Overflow in calibration coefficient calculation (Output data is invalid)                                                                 |

| [0] | OFOV     | Overflow flag in offset calibration of ADC output data.  When over flow is occurred in offset calibration of ADC conversion data, this bit is set to "1".  In case of "1", ADC output data is invalid value.  When either "AMPDATAO", "AUXDATAO" or "TMPDATA" is read, this bit is cleared to "0".  O: No overflow in offset calibration data  1: Overflow in offset calibration data (Output data is invalid)                                                                             |

## AMPDATA0 / AMPDATA1 Register

Register Address: 0x02 / 0x03, EEPROM Address: -

|          |                        | AMPDATA0                                                    |  |  |  |  |   |      |         |                        | AMPDATA1 |  |  |  |  |  |  |

|----------|------------------------|-------------------------------------------------------------|--|--|--|--|---|------|---------|------------------------|----------|--|--|--|--|--|--|

|          | Register Address: 0x02 |                                                             |  |  |  |  |   |      |         | Register Address: 0x03 |          |  |  |  |  |  |  |

| BIT      | [7]                    | [7] [6] [5] [4] [3] [2] [1] [0] [7] [6] [5] [4] [3] [2] [1] |  |  |  |  |   |      |         |                        | [0]      |  |  |  |  |  |  |

| BIT NAME |                        |                                                             |  |  |  |  | Α | MPDA | TA [15: | 0]                     |          |  |  |  |  |  |  |

| R/W      |                        | R                                                           |  |  |  |  |   |      |         |                        |          |  |  |  |  |  |  |

| RESET    |                        |                                                             |  |  |  |  |   |      | -       |                        |          |  |  |  |  |  |  |

| BIT                                   | BIT NAME      | FUNCTION                                                               |

|---------------------------------------|---------------|------------------------------------------------------------------------|

| AMPDATA0 [7:0]<br>+<br>AMPDATA1 [7:0] | AMPDATA[15:0] | ADC output data register for amplifier input mode. Singed 16-Bit data. |

## **AUXDATA0 / AUXDATA1 Register**

Register Address: 0x04 / 0x05, EEPROM Address: -

| 7107127117107 | to / / to / Ext. / to gisto! |                                                                 |  |  |  |  |   |                        | ogioto.  | , .aa. oc |     | ., одос | , <u> </u> |  | , .aa. 00 | <u> </u> |

|---------------|------------------------------|-----------------------------------------------------------------|--|--|--|--|---|------------------------|----------|-----------|-----|---------|------------|--|-----------|----------|

|               |                              | AUXDATA0                                                        |  |  |  |  |   |                        | AUXDATA1 |           |     |         |            |  |           |          |

|               | Register Address: 0x04       |                                                                 |  |  |  |  |   | Register Address: 0x05 |          |           |     |         |            |  |           |          |

| BIT           | [7]                          | [7] [6] [5] [4] [3] [2] [1] [0] [7] [6] [5] [4] [3] [2] [1] [0] |  |  |  |  |   |                        |          |           | [0] |         |            |  |           |          |

| BIT NAME      |                              |                                                                 |  |  |  |  | Α | UXDA                   | TA [15:  | 0]        |     |         |            |  |           |          |

| R/W           |                              | R                                                               |  |  |  |  |   |                        |          |           |     |         |            |  |           |          |

| RESET         |                              |                                                                 |  |  |  |  |   |                        | -        |           |     |         |            |  |           |          |

| BIT                                   | BIT NAME      | FUNCTION                                                               |

|---------------------------------------|---------------|------------------------------------------------------------------------|

| AUXDATA0 [7:0]<br>+<br>AUXDATA1 [7:0] | AUXDATA[15:0] | ADC output data register for Auxiliary input mode. Signed 16-Bit data. |

## TMPDATA0 / TMPDATA1 Register

Register Address: 0x06 / 0x07, EEPROM Address: -

|          |                        |                                 |  | TMPD | OATA0 |   |  |     |                        |     | TMPDATA1 |     |     |     |     |     |

|----------|------------------------|---------------------------------|--|------|-------|---|--|-----|------------------------|-----|----------|-----|-----|-----|-----|-----|

|          | Register Address: 0x06 |                                 |  |      |       |   |  |     | Register Address: 0x07 |     |          |     |     |     |     |     |

| BIT      | [7]                    | [7] [6] [5] [4] [3] [2] [1] [0] |  |      |       |   |  | [0] | [7]                    | [6] | [5]      | [4] | [3] | [2] | [1] | [0] |

| BIT NAME |                        | TMPDATA [9:0]                   |  |      |       |   |  |     |                        |     | -        | -   | -   | -   | -   | -   |

| R/W      |                        | R.W                             |  |      |       |   |  |     |                        | -   |          |     |     |     |     |     |

| RESET    |                        |                                 |  |      |       | - |  |     |                        |     | -        | -   | -   | -   | -   | -   |

| ビット            | ビット名         | 機能                                                                            |

|----------------|--------------|-------------------------------------------------------------------------------|

|                |              | ADC output data register for Temperature sensor input mode.                   |

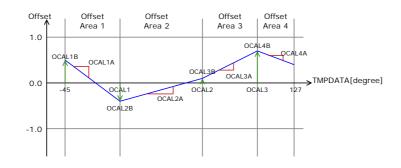

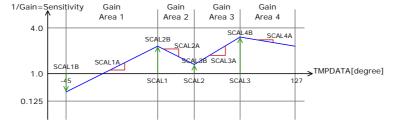

| TMPDATA0 [7:0] |              | Signed 8.2 fixed point format. (-45°C to +127.75°C)                           |

| +              | TMPDATA[9:0] | Temperature calibration calculation is executed by value of TEMPDATA.         |

| TMPDATA1 [7:6] |              | When calibration is executed by using external temperature sensor, write data |

|                |              | which getting from external temperature sensor to this register.              |

## **ID Register**

Register Address: 0x08, EEPROM Address: -

|          |     |          |     | ID  |     |     |     |     |  |

|----------|-----|----------|-----|-----|-----|-----|-----|-----|--|

| BIT      | [7] | [6]      | [5] | [4] | [3] | [2] | [1] | [0] |  |

| BIT NAME |     | ID [7:0] |     |     |     |     |     |     |  |

| R/W      |     | R        |     |     |     |     |     |     |  |

| RESET    |     | 0x55     |     |     |     |     |     |     |  |

| BIT   | BIT NAME | FUNCTION                                                                     |

|-------|----------|------------------------------------------------------------------------------|

| [7:0] | ID       | Fixed value "0x55" is stored as a chip identification code in this register. |

## ROMADR0/ROMADR1 Register

Register Address: 0x09 / 0x0A, EEPROM Address: -

|          |                        | ROMADR0 |     |     |     |               |                        |     | ROMADR1 |     |     |     |     |     |     |     |

|----------|------------------------|---------|-----|-----|-----|---------------|------------------------|-----|---------|-----|-----|-----|-----|-----|-----|-----|

|          | Register Address: 0x09 |         |     |     |     |               | Register Address: 0x0A |     |         |     |     |     |     |     |     |     |

| BIT      | [7]                    | [6]     | [5] | [4] | [3] | [2]           | [1]                    | [0] | [7]     | [6] | [5] | [4] | [3] | [2] | [1] | [0] |

| BIT NAME | -                      | -       | -   | -   | -   | ROMADR [10:0] |                        |     |         |     |     |     |     |     |     |     |

| R/W      | -                      | -       | -   | -   | -   |               |                        |     |         |     | RW  |     |     |     |     |     |

| RESET    | -                      | -       | -   | -   | -   |               |                        |     |         |     | 0x0 |     |     |     |     |     |

| ビット           | ビット名         | 機能                                                                        |

|---------------|--------------|---------------------------------------------------------------------------|

| ROMADR0 [2:0] |              |                                                                           |

| +             | ROMADR[10:0] | This is EEPROM address selection register that read/write from/to EEPROM. |

| ROMADR1 [7:0] |              |                                                                           |

<sup>\*</sup>Be sure to set ROMADR0[4:3] = "00" to control EEPROM.

# **ROMDATA Register**

Register Address: 0x0B, EEPROM Address: -

|          |     |                                 |  | ROMDATA |  |  |  |  |  |  |

|----------|-----|---------------------------------|--|---------|--|--|--|--|--|--|

| BIT      | [7] | [7] [6] [5] [4] [3] [2] [1] [0] |  |         |  |  |  |  |  |  |

| BIT NAME |     | ROMDATA [7:0]                   |  |         |  |  |  |  |  |  |

| R/W      |     | RW                              |  |         |  |  |  |  |  |  |

| RESET    |     | 0x00                            |  |         |  |  |  |  |  |  |