# XRT82L24A

REV. 1.1.2

#### QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

#### AUGUST 2004

# **GENERAL DESCRIPTION**

The XRT82L24A is a fully integrated Quad (four channels) short-haul line interface unit for E1(2.048Mbps)  $75\Omega$  or  $120\Omega$  applications. Each channel consists of a receiver with equalizer for reliable data and clock recovery, and a transmitter which accepts either single or dual-rail digital inputs for signal transmission to the line using a low output impedance line driver. The device also includes a crystal-less jitter attenuator which, depending on system requirements, can be selected in the receive or transmit path through the Host or Hardware Mode control.

XRT82L24A is a low power CMOS device operating on a single 3.3V supply with 5V tolerant digital inputs.

#### FEATURES

- Fully integrated quad, short-haul PCM transceivers for E1 applications.

- On Chip Receive Equalizer and Transmit Pulse Shaper for CEPT 75Ω and 120Ω line terminations

- On chip clock recovery circuit

- Transformer or capacitor coupled receiver inputs

- Crystal-less jitter attenuator can be selected in the transmit or receive path

- High receiver interference immunity

- Per-channel transmit power shutdown

- Tri-state transmit output capability

- On chip per-channel driver failure monitoring circuit

- On chip HDB3/B8ZS/AMI encoder/decoder functions

- Supports Gapped Clock for Multiplexer Mapper Applications

- Transmit return loss meets or exceeds ETSI 300

166 standard

- Meets or exceeds specifications in ITU G.703, G.775, G.736 and G.823; ETSI 300-166

- Meets or exceeds G.783 and G.823 Jitter Specifications

- 3.3V or 5.0V Logic level inputs

- Single +3.3V Supply Operation

- New Patent# 6,313,671B1 Low Power IC I/O Buffer

#### APPLICATIONS

- Digital cross connects (DSX-1)

- · Channel Banks

- · High speed data transmission line cards

- E1 Multiplexer

- Public switching systems and PBX interfaces

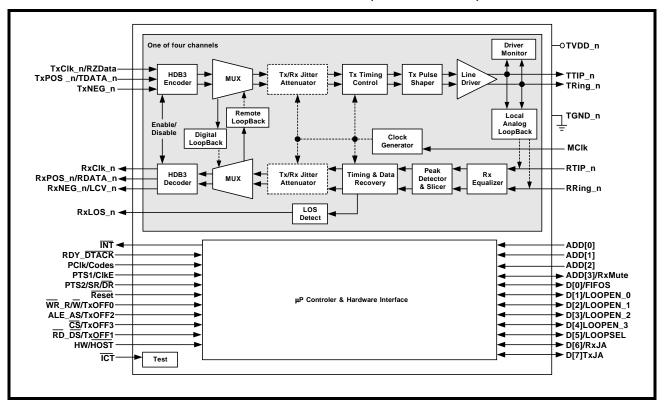

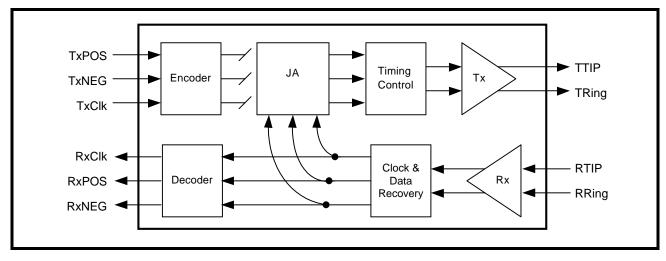

#### FIGURE 1. BLOCK DIAGRAM OF THE XRT82L24A E1 LIU (HOST MODE)

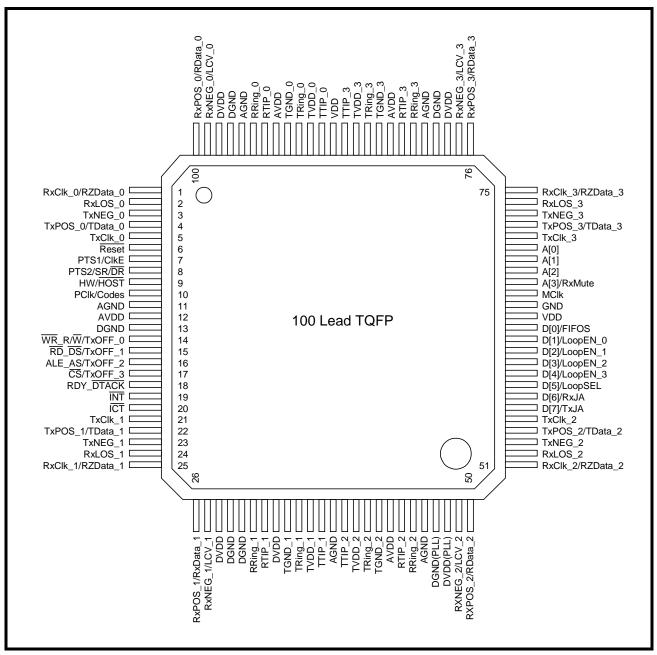

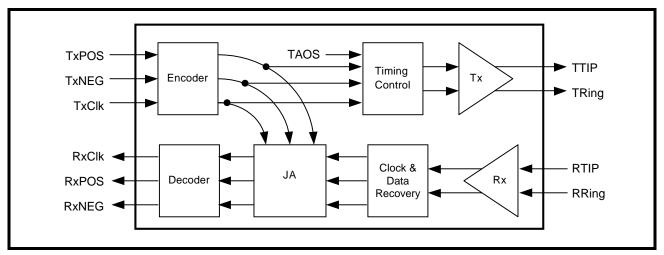

#### FIGURE 2. BLOCK DIAGRAM OF THE XRT82L24A T1/E1/J LIU (HARDWARE MODE)

ORDERING INFORMATION

| PART NUMBER | PACKAGE                         | OPERATING TEMPERATURE RANGE |  |

|-------------|---------------------------------|-----------------------------|--|

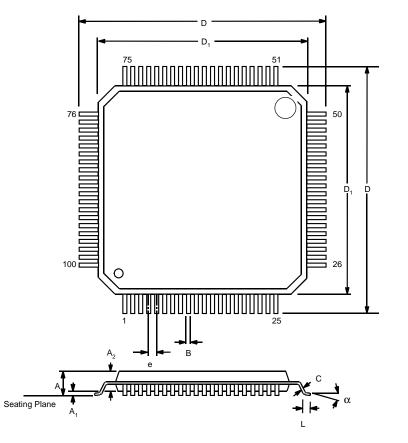

| XRT82L24AIV | 100 Lead TQFP (14 x 14 x 1.4mm) | -40°C to +85°C              |  |

# TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                                | 1  |

|----------------------------------------------------------------------------------------------------|----|

| Features                                                                                           | 1  |

| APPLICATIONS                                                                                       |    |

| Figure 1. Block Diagram of the XRT82L24A E1 LIU (Host Mode)                                        | 1  |

| Figure 2. Block Diagram of the XRT82L24A T1/E1/J LIU (Hardware Mode)                               |    |

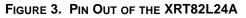

| Figure 3. Pin Out of the XRT82L24A                                                                 |    |

| TABLE OF CONTENTS                                                                                  |    |

| PIN DESCRIPTION                                                                                    |    |

|                                                                                                    |    |

| RECEIVER SECTIONS                                                                                  |    |

| TRANSMITTER SECTIONS                                                                               |    |

|                                                                                                    |    |

| Сьоска                                                                                             |    |

| JITTER ATTENUATOR                                                                                  |    |

| CONTROL                                                                                            |    |

| Power Supplies and Grounds                                                                         |    |

| SYSTEM-FUNCTIONAL DESCRIPTION                                                                      |    |

| RECEIVER                                                                                           | 10 |

| JITTER ATTENUATOR                                                                                  |    |

| GAPPED CLOCK (JA MUST BE ENABLED IN THE TRANSMIT PATH)                                             |    |

| TABLE 1: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS                                     | 10 |

| HDB3/AMI DECODER                                                                                   | 10 |

| RECEIVER LOSS OF SIGNAL (LOS)                                                                      | 10 |

| CONDITIONS FOR DECLARING AND CLEARING LOS IN THE E1 MODE.                                          | 11 |

| RECEIVE DATA MUTING                                                                                | 11 |

| LOOP-BACK MODES                                                                                    | 11 |

| REMOTE LOOP-BACK (RLOOP) MODE                                                                      |    |

| DIGITAL LOCAL LOOP-BACK (DLOOP) MODE                                                               |    |

| ANALOG LOCAL LOOP-BACK (ALOOP) MODE                                                                |    |

| Figure 4. Remote Loop-Back with jitter attenuator selected in receive path                         |    |

| Figure 5. Remote Loop-Back with jitter attenuator selected in transmit path                        |    |

| Figure 6. Digital Local Loop-Back with option to transmit all "ones" to the line (JA selected & in |    |

| ceive path)                                                                                        |    |

| Figure 7. Digital Local Loop-Back with option to transmit all "ones" to the line (JA selected & in |    |

| transmit path)                                                                                     |    |

| Figure 8. Analog Local Loop-Back signal flow Jitter Attenuator selected & in Receive path          |    |

| Figure 9. Analog Local Loop-Back signal flow Jitter Attenuator selected & in transmit path         |    |

| Reset Operation                                                                                    |    |

| RECEIVER MODES OF OPERATION                                                                        |    |

| RECEIVE DATA INVERT MODE                                                                           |    |

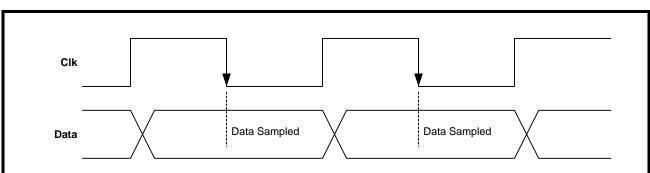

| Figure 10. Data changes on rising edge of Clk and Data is sampled on falling edge                  |    |

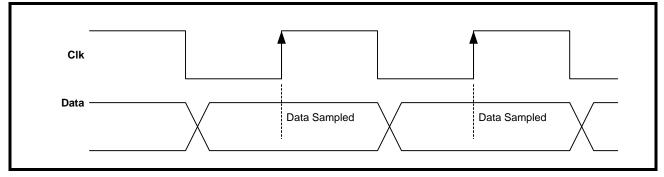

| Figure 10. Data changes on falling edge of Clk and is sampled on rising edge                       |    |

| TRANSMIT CLOCK SAMPLING EDGE                                                                       |    |

| SINGLE RAIL, DUAL RAIL                                                                             |    |

|                                                                                                    |    |

| TRANSMIT ALL ONES (TAOS)                                                                           |    |

| HDB3/AMI ENCODER                                                                                   |    |

| TRANSMIT PULSE SHAPER                                                                              |    |

|                                                                                                    |    |

|                                                                                                    |    |

| INTERFACING THE XRT 82L24A TO THE LINE                                                             |    |

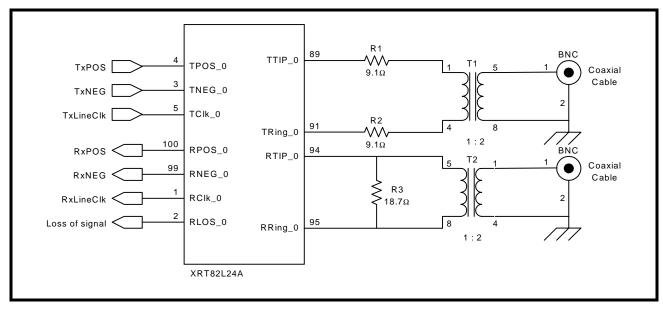

| Figure 12. XRT 82L24A Channel 1in an E1 unbalanced 75 W application                                |    |

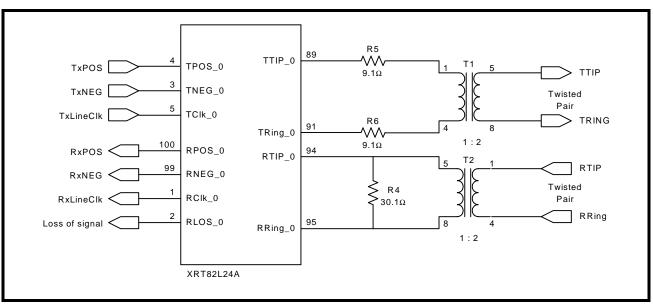

| Figure 13. XRT 82L24A Channel 1 - E1 120 W balanced application                                    |    |

| TABLE 2: E1 RECEIVER ELECTRICAL CHARACTERISTICS                                                    | 18 |

REV. 1.1.2

| TABLE 3: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS                                        | . 19 |

|-------------------------------------------------------------------------------------------|------|

| TABLE 4: TRANSMIT PULSE MASK SPECIFICATION                                                | . 19 |

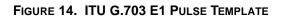

| Figure 14. ITU G.703 E1 Pulse Template                                                    | 20   |

| TABLE 5: DC ELECTRICAL CHARACTERISTICS                                                    |      |

| TABLE 6: POWER CONSUMPTION (TA=-40°C TO 85°C, VDD=3.3V + 5%, UNLESS OTHERWISE SPECIFIED.) | 21   |

| ABSOLUTE MAXIMUM RATINGS                                                                  | . 21 |

| TABLE 7: AC ELECTRICAL CHARACTERISTICS                                                    | . 21 |

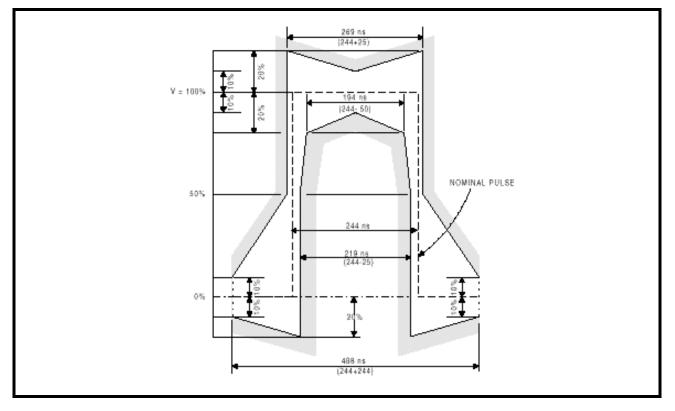

| Figure 15. Transmit Clock and Input Data Timing                                           | 22   |

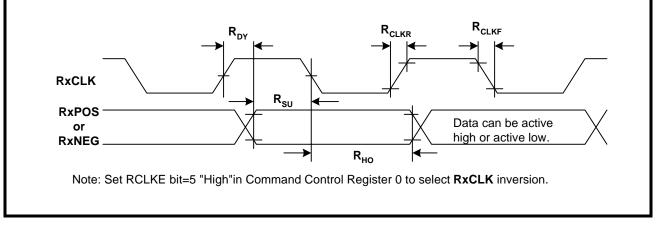

| Figure 16. Receive Clock and Output Data Timing                                           | . 22 |

| TABLE 8: MICROPROCESSOR INTERFACE SIGNAL                                                  |      |

| TABLE 9: MICROPROCESSOR REGISTER MAP                                                      | . 24 |

| TABLE 10: COMMAND CONTROL REGISTER 0                                                      | . 25 |

| TABLE 11: COMMAND CONTROL REGISTER 1                                                      | . 26 |

| TABLE 12: CHANNEL STATUS REGISTER                                                         | . 27 |

| TABLE 13: CHANNEL MASK REGISTER                                                           | -    |

| TABLE 14: CHANNEL CONTROL REGISTER                                                        | . 29 |

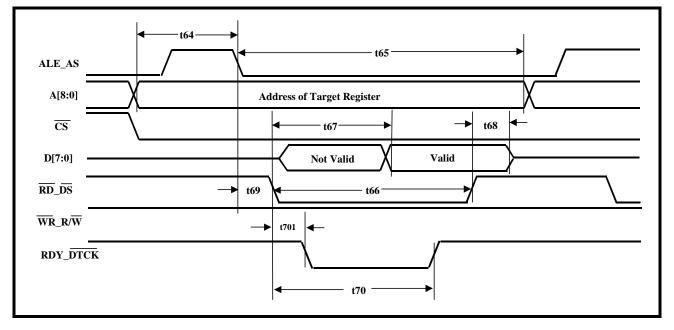

| Figure 17. Intel Interface Timing (Read)                                                  | . 30 |

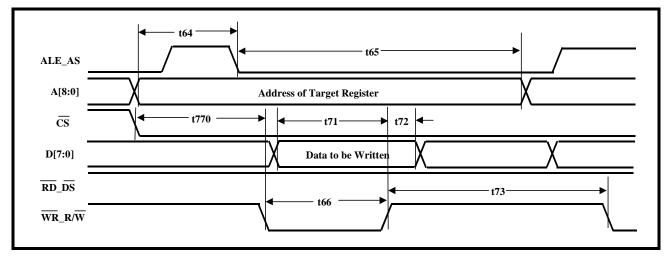

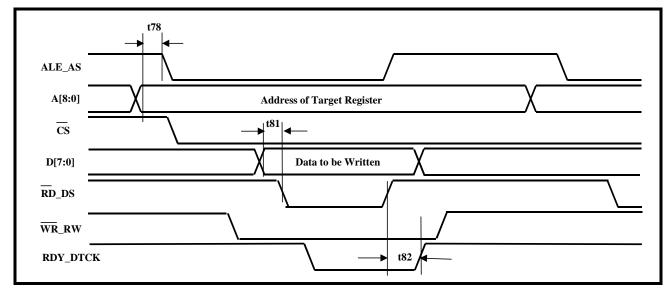

| Figure 18. Intel Interface Timing (Write)                                                 | . 30 |

| TABLE 15: INTEL INTERFACE TIMING SPECIFICATIONS                                           | -    |

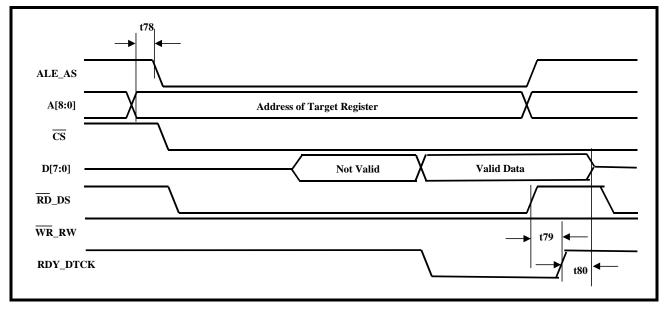

| Figure 19. Microprocessor Interface Timing - Motorola Type Programmed I/O Read Operation  |      |

| Figure 20. Microprocessor Interface Timing - Motorola Type Programmed I/O Write Operation |      |

| Figure 21. Microprocessor Interface Timing - Reset Pulse Width                            |      |

| TABLE 16: MOTOROLA INTERFACE TIMING SPECIFICATION                                         |      |

| JITTER TOLERANCE                                                                          |      |

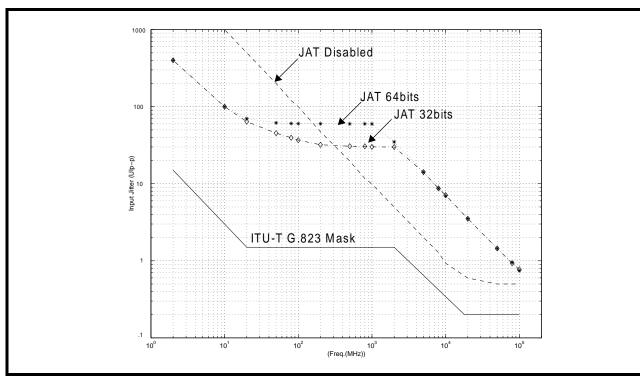

| Figure 22. Receive Maximum Jitter Tolerance                                               |      |

| Figure 23. Receiver Jitter Transfer Function (Jitter Attenuator disabled)                 | . 35 |

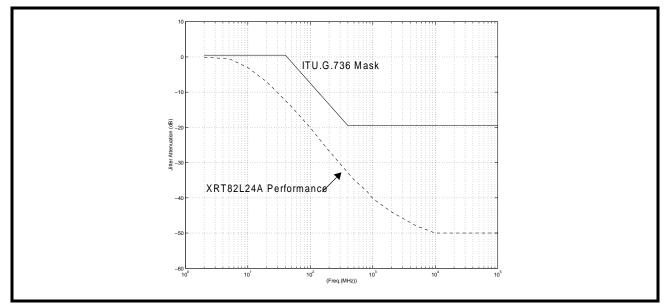

| Figure 24. Jitter Attenuation Function                                                    |      |

| Ordering Information                                                                      |      |

| PACKAGE DIMENSIONS 100 LEAD TQFP 14x14MM                                                  |      |

| REVISION HISTORY                                                                          | . 37 |

# **PIN DESCRIPTION**

| PIN #                 | Nаме                                                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RECEI                 | RECEIVER SECTIONS                                                            |      |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 1<br>25<br>51<br>75   | RxCLK_0/RZData_0<br>RxCLK_1/RZData_1<br>RxCLK_2/RZData_2<br>RxCLK_3/RZData_3 | 0    | Receiver_n Clock Output<br>Rzdata Output:<br>In Data Slicer Mode, (register 0, bit 7 = 1) or in Hardware Mode when MCIk is<br>absent, this signal is OR-ed RZdata after the slicers.                                                                                                                                                                                                     |  |  |  |  |  |

| 2<br>24<br>52<br>74   | RxLOS_0<br>RxLOS_1<br>RxLOS_2<br>RxLOS_3                                     | 0    | <b>Receiver_n Loss of Signal</b> . This signal is asserted "High" to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 100<br>26<br>50<br>76 | RxPOS_0/RData_0<br>RxPOS_1/RData_1<br>RxPOS_2/RData_2<br>RxPOS_3/RData_3     | 0    | Receiver 1 Positive Data Output:<br>In dual-rail mode, this signal is the receive P-rail output data.<br>Receiver 1 NRZ Data Output:<br>In single-rail mode, this signal is the receive output data.                                                                                                                                                                                     |  |  |  |  |  |

| 99<br>27<br>49<br>77  | RxNEG_0/LCV_0<br>RxNEG_1/LCV_1<br>RxNEG_2/LCV_2<br>RxNEG_3/LCV_3             | 0    | Receiver_n Negative Data Output:<br>In dual-rail mode, n-rail data are sent to the framer.<br>Line Code Violation Output - Channel_n:<br>In single-rail mode, this signal output "High" for one receive clock cycle to indi-<br>cate a code violation is detected in the received data. If AMI coding is selected,<br>every bipolar violation received will cause this pin to go "High". |  |  |  |  |  |

| 95<br>31<br>45<br>81  | RRing_0<br>RRing_1<br>RRing_2<br>RRing_3                                     | Ι    | Receiver_n Differential Negative Input.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 94<br>32<br>44<br>82  | RTIP_0<br>RTIP_1<br>RTIP_2<br>RTIP_3                                         | I    | Receiver_n Differential Positive Input.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 67                    | RXMUTE                                                                       | I    | Hardware Mode, Receive Muting:<br>Connect this pin "High" to mute RxPOS/RxNEG output to a low state upon<br>receive LOS condition to prevent data chattering. Connect Low to disable mut-<br>ing function.                                                                                                                                                                               |  |  |  |  |  |

| TRANS                 | MITTER SECTIONS                                                              |      |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 3<br>23<br>53<br>73   | TxNEG_0<br>TxNEG_1<br>TxNEG_2<br>TxNEG_3                                     | Ι    | <b>Transmitter_n Negative NRZ Data Input</b> . In dual-rail mode, this signal is the n-<br>rail input data for transmitter 0. In single-rail mode, this pin can be left uncon-<br>nected.                                                                                                                                                                                                |  |  |  |  |  |

| 4<br>22<br>54<br>72   | TxPOS_0/TData_0<br>TxPOS_1/TData_1<br>TxPOS_2/TData_2<br>TxPOS_3/TData_3     | I    | Transmitter_n Positive Data Input. In dual-rail mode, this signal is the p-rail input data for transmitter 0.         Transmitter 0 Data Input. In single-rail mode, this pin is used as the NRZ input data for transmitter 0.                                                                                                                                                           |  |  |  |  |  |

XRT82L24A QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.1.2

| Pin #                | NAME                                     | Түре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                          | DESCRIPTION                                   |  |  |  |

|----------------------|------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|-----------------------------------------------|--|--|--|

| 5<br>21<br>55<br>71  | TxClk_0<br>TxClk_1<br>TxClk_2<br>TxClk_3 | I    | <b>Transmitter_n Clock Input: E1 rate at 2.048MHz ± 50ppm.</b><br>During normal operation both in Host Mode and Hardware Mode, <b>TxClk</b> is used<br>for sampling input data at <b>TxPOS/TData</b> and <b>TxNEG</b> , while <b>MCLK</b> is used as<br>the timing reference for the transmit pulse shaping circuit. If <b>TxClk</b> is active<br>while <b>MClk</b> is not present, <b>TxPOS</b> and <b>TxNEG</b> accepts NRZ data input and the<br>transmit pulse width is determined by <b>TxClk</b> clock duty cycle. If <b>TxClk</b> is tied to<br>"Low", <b>TxPOS</b> and <b>TxNEG</b> input accepts <b>RZ</b> data format and the pulse width is<br>determined by the duty cycle of the input data. In <b>RZ</b> Mode, single-rail data for-<br>mat is not supported.<br><b>In Hardware Mode</b> , if TxClk is tied "High" for more than 10 μs, then TAOS (a<br>continuous all one's AMI signal) will be transmitted to the line using <b>MCLK</b> as<br>timing reference.<br>If TxClk_0 is tied "Low" for more than 10 μs, the transmitter will be powered<br>down and the output will be tri-stated. |                      |                          |                                               |  |  |  |

| 14<br>15<br>16<br>17 | TxOFF_0<br>TxOFF_1<br>TxOFF_2<br>TxOFF_3 | Ι    | set TTIP_n and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ode, tie<br>d TRing_ | this pin "<br>_n to higł | High" to power-down channel 0 transmitter and |  |  |  |

| 91<br>35<br>41<br>85 | TRing_0<br>TRing_1<br>TRing_2<br>TRing_3 | 0    | Transmitter_n Ring Output:<br>Negative Differential data output to the line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                          |                                               |  |  |  |

| 89<br>37<br>39<br>87 | TTIP_0<br>TTIP_1<br>TTIP_2<br>TTIP_3     | 0    | Transmitter_n Tip Output:<br>Positive Differential data output to the line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                          |                                               |  |  |  |

| MICRO                | PROCESSOR INTER                          | FACE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                          |                                               |  |  |  |

| 6                    | RESET                                    | I    | <b>Hardware Reset</b> (Active Low). When this pin is tied Low for more than $10\mu$ S, the device is put in the reset state.<br><b>Note:</b> Internally pulled -up with a 50k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                          |                                               |  |  |  |

| 7                    | PTS1                                     | I    | Processor Typ<br>Host Mode<br>In Host Mode t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                          | its are set in the command mode               |  |  |  |

|                      |                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTS1                 | PTS2                     |                                               |  |  |  |

|                      |                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                    | 0                        | 8HC11,8081,80C188 (async.)                    |  |  |  |

|                      |                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                    | 0                        | Motorola 68K (async.)                         |  |  |  |

|                      |                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                    | 1                        | Intel x86 (sync.)                             |  |  |  |

|                      |                                          |      | 1 1 Intel i906,Motorola 860 (sync.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |                          |                                               |  |  |  |

|                      | CIKE                                     | I    | Hardware Mode:         The state of the ClkE input controls the sampling edge of both TxClk and RxClk.         A "1" selects the positive edge of TxClk and RxClk         A "0" selects the negative edge of TxClk and RxClk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                          |                                               |  |  |  |

#### XRT82L24A QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR *REV. 1.1.2*

| PIN # | Nаме          | Түре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | De     | SCRIPTION                 |  |  |  |

|-------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------|--|--|--|

| 8     | PTS2<br>SR/DR | I    | Host Mode:         Processor Type Select Input bit 2:         See description for pin 7.         Hardware Mode         Single rail/Dual Rail Control         Connect this pin "Low" to select transmit and receive data format in dual-rail         mode. In this mode, HDB3 encoder and decoder are not available. Connect this         pin "High" to select single-rail data format.         Note: Internally pulled -downwith a 50kΩ resistor.               |        |                           |  |  |  |

| 9     | HW/HOST       | Ι    | Mode Control Input:<br>This pin is used to select the operating mode of the device, (Hardware Mode or<br>Host Mode.)<br>In Hardware Mode, the parallel Microprocessor interface is disabled and<br>enables all hardware control pin functions.<br>In Host Mode, the parallel microprocessor interface pins are used for control<br>functions.                                                                                                                   |        |                           |  |  |  |

|       |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin 9  | Operating Mode            |  |  |  |

|       |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | "Low"  | Host Mode                 |  |  |  |

|       |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | "High" | Hardware Mode             |  |  |  |

|       |               |      | <b>Note:</b> Internally pulled "High" with 50k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                       |        |                           |  |  |  |

| 10    | PCLK<br>Codes | I    | <ul> <li>Processor Clock Input.</li> <li>Input clock for synchronous microprocessor operation. Maximum clock rate is 16 MHz. This pin is internally pulled-up for asynchronous microprocessor interface when no clock is present.</li> <li>Coding/Decoding Select.</li> <li>In Hardware Mode, if single-rail data format is selected (pin 8 ="1"), connect this pin "High" to select AMI encoding and decoding. Connect this pin Low to select HDB3.</li> </ul> |        |                           |  |  |  |

| 14    | WR_R/W        | I    | <b>Write Input (Read/Write)</b> .<br>With Intel bus timing, a Low pulse on WR selects a write operation when $\overline{CS}$ pin is Low. When configured in Motorola bus timing, a "High" pulse on R/W selects a read operation and a Low pulse on R/W selects a write operation when $\overline{CS}$ is Low.                                                                                                                                                   |        |                           |  |  |  |

| 15    | RD_DS         | I    | <b>Read Input (Data Strobe).</b><br>With Intel bus timing, a Low pulse on $\overline{RD}$ selects a read operation when CS pin is Low. When configured in Motorola bus timing, a Low pulse on DS indicates a read or write operation when $\overline{CS}$ pin is Low.                                                                                                                                                                                           |        |                           |  |  |  |

| 16    | ALE_AS        | I    | Address Latch Input (Address Strobe).<br>With Intel bus timing, the address inputs are latched into the internal register on<br>the falling edge of ALE. When configured in Motorola bus timing, the address<br>inputs are latched into the internal register on the falling edge of AS.                                                                                                                                                                        |        |                           |  |  |  |

| 17    | CS            | Ι    | Chip Select Input.<br>This signal must be                                                                                                                                                                                                                                                                                                                                                                                                                       |        | access the parallel port. |  |  |  |

XRT82L24A QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| Pin #                                        | NAME                                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 18                                           | RDY_DTACK                                                    | 0    | <b>Ready Output (Data Transfer Acknowledge Output)</b> .<br>With Intel bus timing, RDY is asserted "High" to indicate the device has com-<br>pleted a read or write operation. When configured in Motorola bus timing,<br>DTACK is asserted Low to indicate the device has completed a read or write<br>cycle.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 67<br>68<br>69<br>70                         | A[3]<br>A[2]<br>A[1]<br>A[0]                                 | I    | Host Mode, Microprocessor Interface Address Bus [3]<br>Host Mode, Microprocessor Interface Address Bus [2]<br>Host Mode, Microprocessor Interface Address Bus [1]<br>Host Mode, Microprocessor Interface Address Bus [0].                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63 | D[7]<br>D[6]<br>D[5]<br>D[4]<br>D[3]<br>D[2]<br>D[1]<br>D[0] | I/O  | Data Bus[7:0].<br>Microprocessor read/write data bus pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| CLOCK                                        | (S                                                           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 66                                           | MCLK                                                         |      | Master Clock Input.<br>This signal is an independent 2.048MHz clock with accuracy better than<br>±50ppm and duty cycle within 40% to 60%. The function of MCLK is to provide<br>internal timing for the PLL clock recovery circuit, jitter attenuator block, refer-<br>ence clock during transmit all ones data and timing reference for the micropro-<br>cessor in Host Mode operation.<br>If MCIk is absent, all receive channels perform as analog front-end (AFE). The<br>OR-ed RZ data is also available at RxCIk output in this mode, instead. The<br>clock recovery function is disabled. |  |  |  |  |  |

| JITTER                                       | ATTENUATOR                                                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 56                                           | ТХЈА                                                         | I    | <b>Transmit Jitter Attenuator Select</b> .<br>In Hardware Mode, connect this pin "High" to select jitter attenuator in the trans-<br>mit path and connect Low to disable jitter attenuator.<br>Setting RXJA simultaneously "High" also disables jitter attenuator selection.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 57                                           | RXJA                                                         | I    | Receive Jitter Attenuator Select.<br>In Hardware Mode, connect this pin "High" to select jitter attenuator in the<br>receive path and connect Low to disable jitter attenuator.<br>Setting TXJA simultaneously "High" also disables jitter attenuator selection.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| CONTR                                        | ROL                                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 8                                            | SR/DR                                                        | I    | Single rail/Dual Rail Control:<br>Hardware Mode<br>Connect this pin "Low" to select transmit and receive data format in dual-rail<br>mode. In this mode, HDB3 encoder and decoder are not available. Connect this<br>pin "High" to select single-rail data format.<br>Note: Internally pulled -down with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 10                                           | Codes                                                        | I    | <b>Coding/Decoding Select</b> .<br><b>In Hardware Mode</b> , if single-rail data format is selected (pin 8 ="1"), connect this pin "High" to select AMI encoding and decoding. Connect this pin Low to select HDB3.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Pin #                      | NAME                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------------------|----------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 19                         | ĪNT                                          | 0    | <b>Interrupt Output</b> .<br>This pin is asserted Low to indicate an alarm condition has occurred within the device. Interrupt generation can be globally disabled by setting the GIE bit to a "0" in the command control register.<br><b>Note:</b> This pin is an open drain output and requires an external 10KΩ pull-up resistor. |  |  |  |  |

| 20                         | ІСТ                                          | I    | <b>In-Circuit Testing (Active Low)</b> .<br>When this pin is tied Low, all output pins are forced to high impedance state for in-circuit testing.<br><b>Note:</b> Internally pulled -up with $50k\Omega$ .                                                                                                                           |  |  |  |  |

| 58                         | LOOPSEL                                      | I    | <b>DLoop-back Mode Select</b> .<br>In Hardware Mode, if LOOPEN_(0-3) is "High", this pin is used for selecting<br>loop-back mode. Connect this pin "High" to select local loop-back and Low to<br>select remote loop-back. Digital Loop-back is not supported in Hardware Mode.                                                      |  |  |  |  |

| 62<br>61<br>60<br>59       | LOOPEN_0<br>LOOPEN_1<br>LOOPEN_2<br>LOOPEN_3 | I    | Loop-back Enable - Channel_n:<br>In Hardware Mode:<br>Connect this pin "High" to enable channel_n loop-back operation. Remote or<br>local loop-back is determined by pin 58 setting.                                                                                                                                                 |  |  |  |  |

| 63                         | FIFOS                                        | I    | FIFO Size Select.<br>In Hardware Mode, connect this pin "High" selects 64 bit FIFO depth and con-<br>nect Low to select 32 bit FIFO depth.                                                                                                                                                                                           |  |  |  |  |

| POWER SUPPLIES AND GROUNDS |                                              |      |                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 12                         | AVDD                                         | **** | Analog Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 28                         | DVDD                                         | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 33                         | DVDD                                         | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 90<br>36<br>40<br>86       | TVDD_0<br>TVDD_1<br>TVDD_2<br>TVDD_3         | ***  | Transmitter_n Analog Positive Supply(3.3V± 5%).                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 43                         | AVDD                                         | **** | Analog Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 48                         | DVDD                                         | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 64                         | DVDD                                         | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 78                         | DVDD                                         | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 11                         | AGND                                         | **** | Analog Ground                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 13                         | DGND                                         | **** | Digital Ground                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 29                         | DGND                                         | **** | Digital Ground                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 30                         | DGND                                         | **** | Digital Ground                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 92<br>34<br>42<br>84       | TGND_0<br>TGND_1<br>TGND_2<br>TGND_3         | ***  | Transmitter_n Analog Ground.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

XRT82L24A QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.1.2

| Pin # | NAME | Түре | DESCRIPTION                       |

|-------|------|------|-----------------------------------|

| 38    | AGND | **** | Analog Ground                     |

| 46    | AGND | **** | Analog Ground                     |

| 47    | DGND | **** | Digital Ground                    |

| 65    | DGND | **** | Digital Ground                    |

| 79    | DGND | **** | Digital Ground                    |

| 80    | AGND | **** | Analog Ground                     |

| 83    | AVDD | **** | Analog Positive Supply(3.3V± 5%)  |

| 88    | AVDD | **** | Analog Positive Supply(3.3V± 5%)  |

| 93    | AVDD | **** | Analog Positive Supply(3.3V± 5%)  |

| 96    | AGND | **** | Analog Ground                     |

| 97    | DGND | **** | Digital Ground                    |

| 98    | DVDD | **** | Digital Positive Supply(3.3V± 5%) |

# SYSTEM-FUNCTIONAL DESCRIPTION

A simplified single channel block diagram of the XRT 82L24A is presented in Figure 1. The XRT 82L24A consists of four identical transmit and receive channels for E1(2.048 Mbps) PCM systems. The operational mode of each channel of the line interface can be configured by the microprocessor interface (Host Mode) or by Hardware control.

## RECEIVER

At the receiver input, cable attenuated AMI signals can be coupled to the receiver using a capacitor or a 1:2 transformer. The receive signal first goes through the equalizer for signal conditioning before being applied to the data recovery circuit. The data recovery circuit includes a peak detector which is set typically at 50% for E1 of the equalizer output peak amplitude for data slicing. After the data slicers, the digital representation of the AMI signals goes to the clock recovery circuit for timing recovery and subsequently to the HDB3 decoder (if selected) before they are output via the RxPOS/RDATA and RxNEG/LCV pins. The digital data output can be in dual-rail or single-rail mode depending on the option selected. Clock and timing recovery is accomplished by means of a digital PLL scheme which can tolerate high input jitter and meets or exceeds the jitter tolerance requirements as specified in the ITU - G.823 standard.

#### JITTER ATTENUATOR

To reduce jitter in the transmit line signal or recovered clock and data signals, a crystal-less jitter attenuator with a 32x2 bit or 64x2 bit FIFO is provided for each channel. The jitter attenuator can be configured to op-

erate in either the transmit or receive path, or it can be disabled through Host or Hardware Mode control. The jitter attenuator design is based on a digital scheme that uses the MCLK signal as a reference input. No other high frequency clock is necessary. With the jitter attenuator selected, the typical throughput delay is 16 bits for a 32 bit FIFO depth or 32 bit for a 64 bit FIFO depth. The design of the jitter attenuator is such that if the write and read pointers of the FIFO are within two bits of overflowing or underflowing, the bandwidth of the jitter attenuator is automatically widened in order to permit the "Jitter Attenuator" PLL to track the short term input jitter to avoid data corruption. When this situation occurs, the jitter attenuator will not attenuate input jitter until the read/write pointer's position is outside the two bit window. Under normal condition, the jitter transfer characteristic meets the narrow bandwidth requirement as specified in ITU- G.736 and ITU- I.431standards.

# GAPPED CLOCK (JA MUST BE ENABLED IN THE TRANSMIT PATH)

The XRT82L24A LIU is ideal for multiplexer or mapper applications where the network data crosses multiple timing domains. As the higher data rates are de-multiplexed down to T1 or E1 data, stuffing bits are removed which can leave gaps in the incoming data stream. If the jitter attenuator is enabled in the transmit path, the 32-Bit or 64-Bit FIFO is used to smooth the gapped clock into a steady T1 or E1 output. The maximum gap width of the XRT82L24A is shown in Table 1.

| FIFO DEPTH | Maximum Gap Width |

|------------|-------------------|

| 32-Bit     | 20 UI             |

| 64-Bit     | 50 UI             |

TABLE 1: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS

**Note:** If the LIU is used in a loop timing system, the jitter attenuator should be enabled in the receive path.

# HDB3/AMI DECODER

The decoder function is only active if the chip has been configured to operate in the single-rail mode. When the single-rail mode is selected, the receive line signal will be decoded according to HDB3 rules for E1. Further, any bipolar violation of the HDB3 line coding scheme will be flagged as a Line Code Violation via the LCV output pin. The LCV output pin will be pulsed high for one RxClk cycle for each line code violation that is detected. Excessive number of zeros in the receive data stream are also flagged as a line code violation via the same output pin. If AMI decoding is selected in single-rail mode operation, every bipolar violation in the receive data stream is reported as error at the LCV pin.

# **RECEIVER LOSS OF SIGNAL (LOS)**

The receiver loss of signal monitoring function is implemented using both analog and digital detection schemes compatible with ITU G.775 requirements. When the amplitude of the E1line signal at RTIP/ RRING drops 16dB (typical) below the 0dB nominal level the digital circuit is activated to parse through and check for 32 consecutive zeros before LOS is asserted, to indicate loss of input signal. The number of

consecutive zeros before LOS is declared can be increased to 4096 bits. During extended LOS Mode, the LOS condition will be cleared when 4096 more valid data bits are present (when operating in the Host Mode). The LOS condition is cleared when the input signal rises above 16dB below 0dB nominal level and meets 12.5% density of 4 ones in a 32 bit window with no more than 16 consecutive zeros.

#### Clock signals generated when LOS is declared

The output signal at the RxClk output pin depends upon the type of LOS condition that is occurring.

# Complete Loss of Signal (Zero Amplitude)

If the XRT 82L24A experiences a complete Loss of Signal (e.g., no signal amplitude), then the XRT 82L24A Clock Recovery PLL enters the Training Mode, and Differentially begins to lock onto the signal applied to the MCLK input pin. As a consequence, the Clock Recovery PLL will begin to drive a clock signal to the Terminal Equipment (via the RxClk output pin), which is derived from the MCLK input pin.

# Degraded Type of Loss of Signal Event (Non-Zero Amplitude)

If the XRT 82L24A experiences a degraded type of LOS event (e.g., where there is still a small amount of discernible signal amplitude in the line signal, but small enough to qualify as an LOS event) then the Clock Recovery PLL could lock onto this degraded line signal and will subsequently drive the same frequency via the RxClk output pins.

# CONDITIONS FOR DECLARING AND CLEARING LOS IN THE E1 MODE.

Each E1 channel of the XRT 82L24A has two criteria for LOS Detection, **Analog** and **Digital**. A channel will declare a LOS condition when both of these LOS Detectors detect an LOS condition.

#### **Analog LOS Detector**

The Analog LOS Detector will declare an LOS condition, if it determines that the amplitude of the incoming line signal has dropped to less than

-15dB (below the nominal pulse amplitude of 3V for **twisted-pair**, or 2.37V for **coaxial-cable**) for at least 32 bit-periods.

The Analog LOS Detector will clear the LOS condition, if it determines that the incoming line signal is no more than 12.5dB below the nominal 3V pulse amplitude.

**Note:** The difference in the signal level required to declare and clear LOS is 2.5dB. This 2.5dB hysteresis is designed into the Analog LOS Detector circuitry, in order to prevent chattering in the LOS output pin or bit-field.

#### **Digital LOS Detector**

The Digital LOS Detector will declare an LOS condition, if it detects a string of at least 32 consecutive "0"s.

The Digital LOS Detector will clear the LOS condition, if it determines that the incoming E1 line signal has a pulse density of 12.5% or more without 16 consecutive "0's" for at least 32 consecutive bit periods.

**NOTE:** The pulse density requirement of 12.5% accounts for HDB3 coding.

#### **RECEIVE DATA MUTING**

The XRT 82L24A permits the user to "MUTE" the recovered data output signals anytime the LOS condition is declared. If the user invokes this function, then the RPOS/RDAT and RNEG output pins will be pulled to GND for the duration that the LOS condition exists. This feature is useful in that it prevents the LIU from routing electrical noise (which has been "recovered" by the Clock Recovery PLL) to the Framer IC and preventing it from declaring an LOS condition. This feature is enabled by setting the RXMUTE bit to a "1" in the Host Mode (Register 1, Bit 2 Location) or by connecting pin 67 High in the Hardware Mode.

#### LOOP-BACK MODES

Each channel within the XRT 82L24A can be configured to operate in any of the following loop-back modes:

- Remote Loop-Back Mode

- Digital Local Loop-Back Mode

- Analog Local Loop-Back Mode

Each of these loop-back modes are described in some detail below.

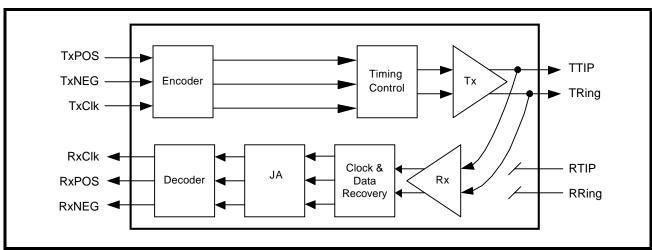

#### **REMOTE LOOP-BACK (RLOOP) MODE**

With Remote Loop-Back activated, (Channel Control Register bit 2 = "1") in Host Mode or in Hardware Mode with **LoopSEL** (pin 58) tied Low and **LoopEN** tied High received data after the jitter attenuator (if selected) is looped back to the transmit path using RxClk as transmit timing. In this mode the data/signals applied to the TxClk, TPOS/TDAT and TNEG input pins are ignored, while RxClk and received data will continue to be available at their respective output pins. Simultaneously setting RLOOP and ALOOP active is not allowed (see Loop-Back Mode in Figure 4 & Figure 5). Remote loop-back has priority over TAOS.

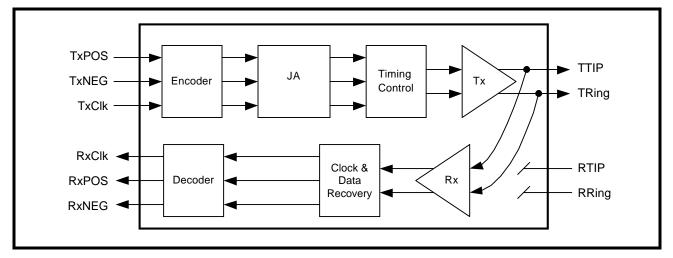

# DIGITAL LOCAL LOOP-BACK (DLOOP) MODE

The Digital Local Loop-Back mode allows the transmit clock and data to be looped back to the corresponding receiver output pins through the encoder/ decoder and the jitter attenuator. In this mode, the receive line signal is ignored, but the transmit data will

# XRT82L24A QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR REV. 1.1.2

be sent to the line uninterrupted. This loop back feature allows users to configure the line interface as a pure jitter attenuator. (see Loop-Back Mode in Figure 6 & Figure 7).

**Note:** Digital Local Loop-Back is not supported in Hardware Mode.

ANALOG LOCAL LOOP-BACK (ALOOP) MODE

With Analog Local Loop-Back activated, the transmit data at TTIP and TRING are looped-back to the analog input of the receiver. External inputs at RTIP/ RRING in this mode are ignored while valid transmit data continues to be sent to the line. Analog Loop-Back exercises most of the functional blocks of the line interface (see Loop-Back Mode in Figure 8 & Figure 9).

FIGURE 5. REMOTE LOOP-BACK WITH JITTER ATTENUATOR SELECTED IN TRANSMIT PATH

FIGURE 6. DIGITAL LOCAL LOOP-BACK WITH OPTION TO TRANSMIT ALL "ONES" TO THE LINE (JA SELECTED & IN RECEIVE PATH)

FIGURE 7. DIGITAL LOCAL LOOP-BACK WITH OPTION TO TRANSMIT ALL "ONES" TO THE LINE (JA SELECTED & IN TRANSMIT PATH)

FIGURE 9. ANALOG LOCAL LOOP-BACK SIGNAL FLOW JITTER ATTENUATOR SELECTED & IN TRANSMIT PATH

#### **RESET OPERATION**

The XRT 82L24A provides both Hardware and Software resets. In Hardware reset, with pin 6 forced to "0" for more than 10 $\mu$ s, the entire state of the device including the microprocessor R/W registers are reset. In Software reset, only the state of the interface is reset (the microprocessor registers are not affected).

# **RECEIVER MODES OF OPERATION**

Through the microprocessor interface or in Hardware Mode, XRT 82L24A offers several alternative receive

modes of operation making it flexible for different applications as dictated by the system requirements.

#### **RECEIVE DATA INVERT MODE**

Receive output data by default is active high at Rx-POS/RDATA and RxNEG/LCV pins. These signals can be changed to active Low by setting the DATAP bit in the interface register (Register 1, Bit 3 = "1"). In single rail mode DATAP = "1", (Register 0, Bit 7 = "1"), LCV output also becomes active Low. Data invert Mode is only available in Host Mode.

#### FIGURE 10. DATA CHANGES ON RISING EDGE OF CLK AND DATA IS SAMPLED ON FALLING EDGE

# **RxClk Clock Sampling Edge**

The sampling edge of the RxClk output can be changed through control bit RClkE within the interface register for receive output data re-timing. With RClkE="1", (Bit 5 = "1"), data is validated on the rising edge of RxClk and with RClkE="0", (Bit 5 = "0"),, receive data is validated on the falling edge of RxClk. In Hardware Mode, the state of pin 7 (ClkE) controls the rising or falling edge of RxClk for data re-timing.

# TRANSMIT CLOCK SAMPLING EDGE

NRZ Transmit data at TxPOS/TDATA or TxNEG is clocked serially into the device using TxClk. With the interface register bit 4 (TClkE="1"), input data is sampled on the rising edge of TxClk. The sampling edge is inverted when TClkE= "0". In Hardware Mode, the state of pin 7 (ClkE) controls the sampling edge of both TxClk and RxClk.

#### SINGLE RAIL, DUAL RAIL

Transmit data format can be in dual-rail (SR/ $\overline{DR}$ =1) or single-rail modes (SR/ $\overline{DR}$ =0). In Hardware Mode, dual or single-rail format is determined by the state of pin 8. For single-rail mode operation, NRZ data can be applied to TxPOS/TDATA with TxClk, while Tx-NEG input is left unconnected. The transmitter converts NRZ input data into differential signal for transmission to the line using low impedance output drivers.

#### TRANSMIT ALL ONES (TAOS)

In the Host Mode, individual channels can be programmed to transmit an all "Ones" AMI signal by setting the per channel bit control TAOS=1. In this mode, input data at TxPOS/TDATA and TxNEG are ignored. In Host Mode, reference clock for TAOS is TxClk. If TxClk is not available, MCLK is used for transmission. In Hardware Mode, if TxClk is not present and High for more than 10µs, TAOS is transmitted using MCLK as a reference. Remote Loop-Back has priority over TAOS request.

#### HDB3/AMI ENCODER

The encoder is only available in single-rail mode (SR/ $\overline{DR}$ =1) in Host Mode, or pin 8 set High in Hardware Mode. In an E1 system, if interface register CODES=0, HDB3 encoding is selected. Input data applied to TxPOS/TDATA which contains more than four consecutive zeros will be removed and replaced by "000V" or "B00V", where "B" indicates a pulse conforming with bipolar rule and "V" represents a pulse violating the rule. With register CODES="1", AMI coding is selected. In Hardware Mode, HDB3 or AMI coding selection is determined by the state of pin 10.

The choice of these codes is made such that an odd number of "B" pulses is transmitted between consecutive bipolar violation "V" pulses

#### TRANSMIT PULSE SHAPER

The transmit pulse shaper uses high a speed clock derived from MCLK to synthesize the shape and width of the transmitted pulse applied to TTIP and TRING. The internal high speed timing generator eliminates the need for a tightly controlled transmit clock TxClk duty cycle.

The intrinsic jitter at the transmit output using a jitterfree input clock source and with the jitter attenuator disabled will generate no more than 0.03Ulpp.

# **DRIVER MONITOR**

The driver monitor circuit is used for detecting transmit driver failure by monitoring the activity at TTIP and TRING. Driver failure may be caused by a shortcircuit in the primary of the transformer or system problems at the input.

In the Host Mode, when the driver monitor detects no transitions at TTIP and TRING for more than 128 clock cycles, the DMO bit (bit 7) in the interface register is set and results in an interrupt (INT) to be gener-

ated. Driver monitor function is not supported in Hardware Mode.

#### TxPOS/TDATA and TxNEG Polarity