# nRF24LU1

# Single Chip 2.4GHz Transceiver with USB Microcontroller and Flash Memory

# Product Specification v1.1

## **Key Features**

- nRF24L01 compatible RF transceiver

- Worldwide 2.4GHz ISM band operation

- Up to 2Mbps on air data rate

- Enhanced ShockBurst™ hardware link layer

- Air compatible with nRF24L01, nRF2401A, 02, E1 and E2

- Low cost external ±60ppm 16MHz crystal

- Full speed USB 2.0 compliant device controller

- Up to 12 Mbps USB transfer rate

- 2 control, 10 bulk/interrupt and 2 ISO endpoints

- · Dedicated 512 bytes endpoint buffer RAM

- Software controlled pull-up resistor for D+

- PLL for full-speed USB operation

- Voltage regulator, 4.0 to 5.25V supply range

- Enhanced 8-bit 8051 compatible microcontroller

- Reduced instruction cycle time

- 32-bit multiplication-division unit

- 16 kbytes of on-chip flash memory

- 2 kbytes of on-chip SRAM

- 6 general purpose digital input/output pins

- · Hardware SPI slave and master, UART

- 3 16-bit timers/counters

- AES encryption/decryption co-processor

- Supports firmware upgrade over USB

- Supports FS2 hardware debugger

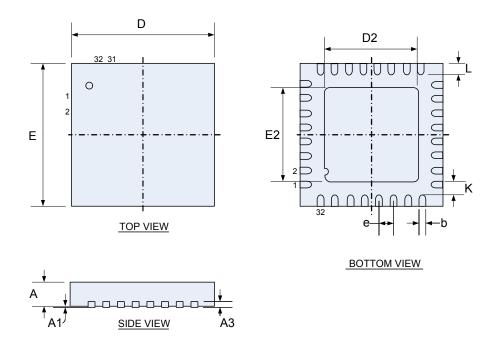

- Compact 32-pin 5x5mm QFN package

# **Applications**

- Compact USB dongles for wireless peripherals

- USB dongles for mouse, keyboards and remotes

- USB dongle 3-in-1 desktop bundles

- USB dongle for advanced media center remote controls

- USB dongle for game controllers

- Toys

# Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

All application information is advisory and does not form part of the specification.

## **Limiting values**

Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.

# Life support applications

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.

| Data sheet status                 |                                                                                                                                                                                                                           |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective product specification   | This product specification contains target specifications for product development.                                                                                                                                        |

| Preliminary product specification | This product specification contains preliminary data; supplementary data may be published from Nordic Semiconductor ASA later.                                                                                            |

| Product specification             | This product specification contains final product specifications. Nordic Semiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

#### Contact details

For your nearest dealer, please see www.nordicsemi.no

#### Main office:

Otto Nielsens vei 12 7004 Trondheim Phone: +47 72 89 89 00 Fax: +47 72 89 89 89

www.nordicsemi.no

# **Writing Conventions**

This product specification follows a set of typographic rules that makes the document consistent and easy to read. The following writing conventions are used:

- Commands, bit state conditions, and register names are written in Courier.

- Pin names and pin signal conditions are written in Courier bold.

- Cross references are <u>underlined and highlighted in blue</u>.

# **Revision History**

| Date          | Version | Description          |

|---------------|---------|----------------------|

| March 2008    | 1.0     |                      |

| November 2008 | 1.1     | Corrected schematics |

#### Attention!

Observe precaution for handling Electrostatic Sensitive Device.

# **Contents**

| 1          | Introduction                                 | 11 |

|------------|----------------------------------------------|----|

| 1.1        | Features                                     | 12 |

| 1.2        | Block diagram                                | 13 |

| 1.3        | Typical system usage                         | 14 |

| 2          | Pin Information                              | 15 |

| 2.1        | Pin Assignments                              | 15 |

| 2.2        | Pin Functions                                | 16 |

| 2.2.1      | Antenna pins                                 | 16 |

| 2.2.2      | USB pins                                     | 16 |

| 2.2.3      | Power supply pins                            |    |

| 2.2.4      | PROG pin                                     | 16 |

| 2.2.5      | Reference current pin                        | 16 |

| 2.2.6      | Port pins                                    |    |

| 2.2.7      | External RESET Pin                           |    |

| 2.2.8      | Crystal oscillator pins                      | 17 |

| 3          | Absolute Maximum Ratings                     | 18 |

| 4          | Operating Conditions                         | 19 |

| 5          | Electrical Specifications                    |    |

| 5.1        | Power consumption and timing characteristics |    |

| 5.2        | RF transceiver characteristics               |    |

| 5.3        | USB interface                                |    |

| 5.4        | Flash memory                                 |    |

| 5.5        | Crystal specifications                       |    |

| 5.6        | DC Electrical Characteristics                |    |

| 6          | RF Transceiver                               |    |

| 6.1        | Features                                     |    |

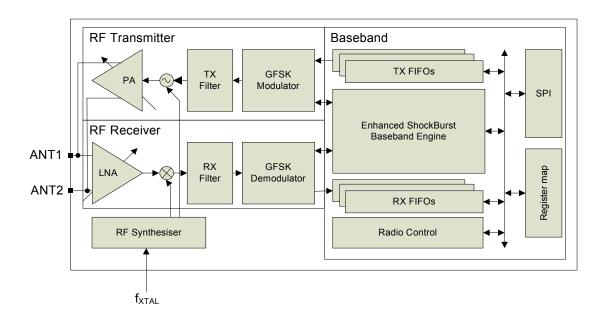

| 6.2        | Block diagram                                |    |

| 6.3        | Radio control                                |    |

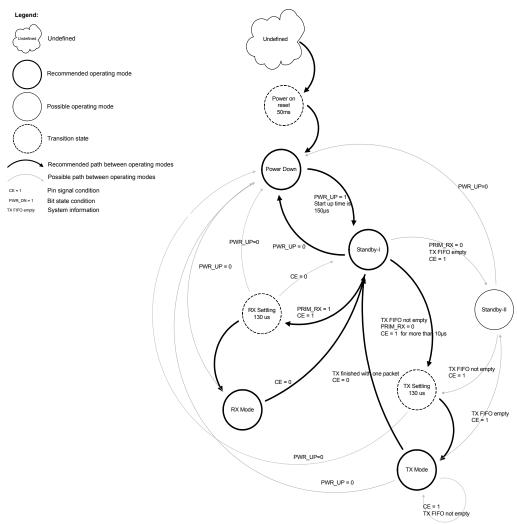

| 6.3.1      | Operational modes                            |    |

| 6.3.1.     | •                                            |    |

| 6.3.1.     |                                              |    |

| 6.3.1.     |                                              |    |

| 6.3.1.     | •                                            |    |

| 6.3.1.     |                                              |    |

| 6.3.1.     |                                              |    |

| 6.3.1.     |                                              |    |

| 6.3.2      | Air data rate                                |    |

| 6.3.3      | RF channel frequency                         |    |

| 6.3.4      | PA control                                   |    |

| 6.3.5      | LNA gain                                     |    |

| 6.3.6      | RX/TX control                                |    |

| 6.4        | Enhanced ShockBurst™                         |    |

| 6.4.1      | Features                                     |    |

| 6.4.2      | Enhanced ShockBurst™ overview                |    |

| J <u> </u> | 5004 000001 0                                | -0 |

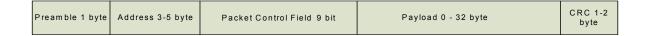

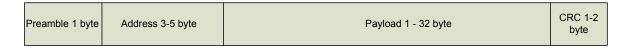

| 6.4.3    | Enhanced Shockburst™ packet format                         | 34 |

|----------|------------------------------------------------------------|----|

| 6.4.3.1  | Preamble                                                   | 34 |

| 6.4.3.2  | Address                                                    | 34 |

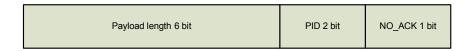

| 6.4.3.3  | Packet control field                                       | 34 |

| 6.4.3.4  | Payload                                                    | 35 |

| 6.4.3.5  | CRC (Cyclic Redundancy Check)                              | 35 |

| 6.4.4    | Automatic packet handling                                  | 35 |

| 6.4.4.1  | Static and dynamic payload length                          | 35 |

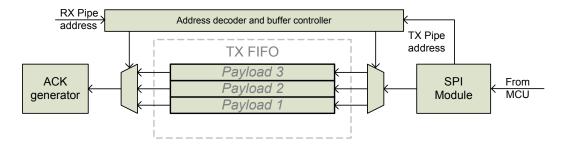

| 6.4.4.2  | Automatic packet assembly                                  | 36 |

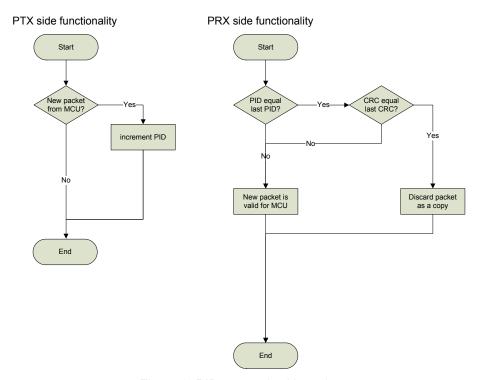

| 6.4.4.3  | Automatic packet validation                                | 37 |

| 6.4.4.4  | Automatic packet disassembly                               | 37 |

| 6.4.5    | Automatic packet transaction handling                      |    |

| 6.4.5.1  | Auto acknowledgement                                       | 38 |

| 6.4.5.2  | Auto Retransmission (ART)                                  | 38 |

| 6.4.6    | Enhanced Shockburst™ flowcharts                            | 40 |

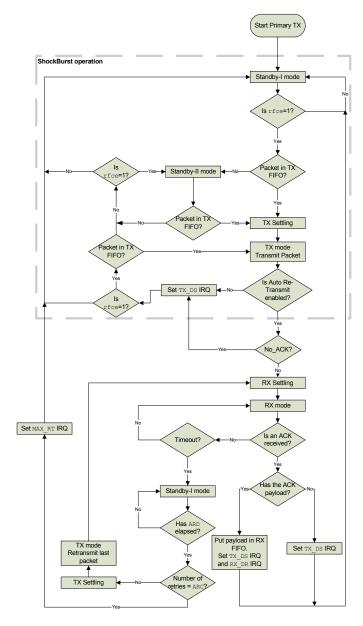

| 6.4.6.1  | PTX operation                                              | 40 |

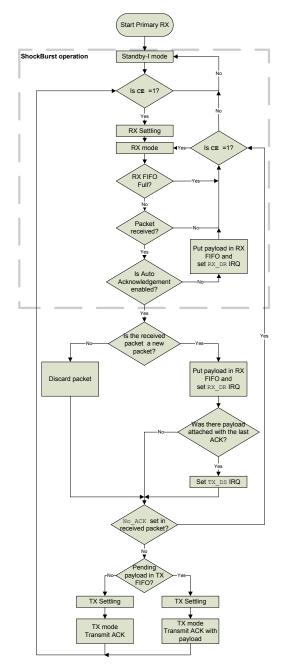

| 6.4.6.2  | PRX operation                                              | 42 |

| 6.4.7    | Multiceiver™                                               | 43 |

| 6.4.8    | Enhanced Shockburst™ timing                                | 46 |

| 6.4.9    | Enhanced Shockburst™ transaction diagram                   | 47 |

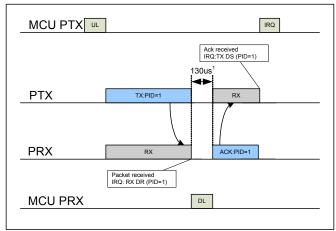

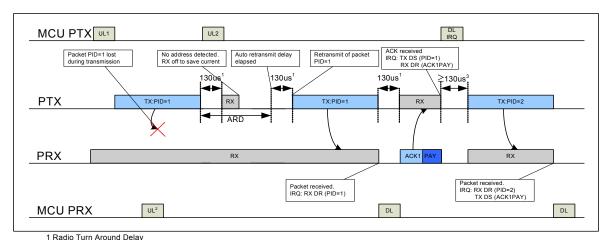

| 6.4.9.1  | Single transaction with ACK packet and interrupts          | 47 |

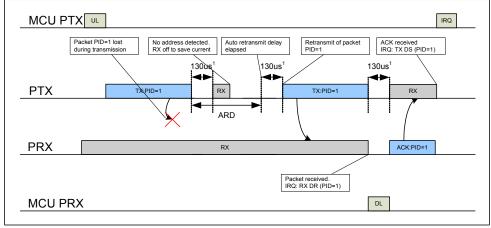

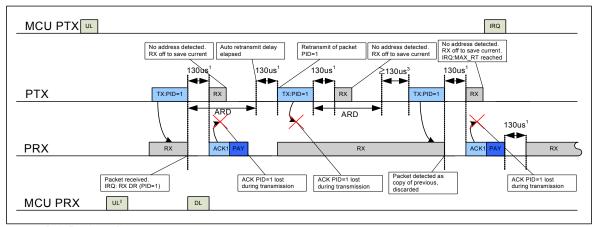

| 6.4.9.2  | Single transaction with a lost packet                      |    |

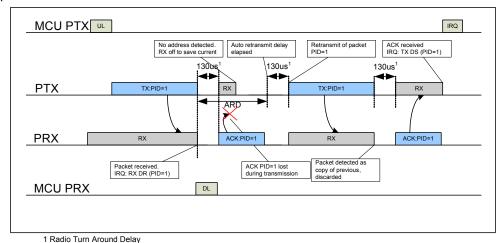

| 6.4.9.3  | Single transaction with a lost ACK packet                  | 49 |

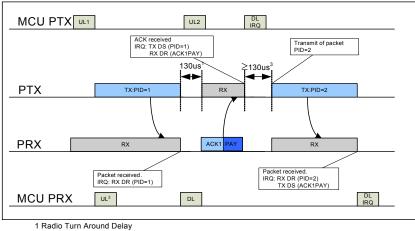

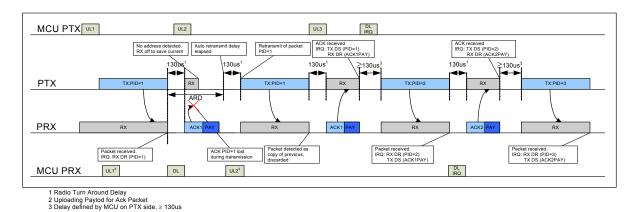

| 6.4.9.4  | Single transaction with ACK payload packet                 | 49 |

| 6.4.9.5  | Single transaction with ACK payload packet and lost packet | 50 |

| 6.4.9.6  | Two transactions with ACK payload packet and the first     |    |

|          | ACK packet lost                                            | 50 |

| 6.4.9.7  | Two transactions where max retransmissions are reached     | 51 |

| 6.4.10   | Compatibility with ShockBurst™                             | 51 |

| 6.4.10.1 | ShockBurst™ packet format                                  | 51 |

| 6.5      | Data and control interface                                 | 52 |

| 6.5.1    | SFR registers                                              |    |

| 6.5.2    | Command set                                                | 53 |

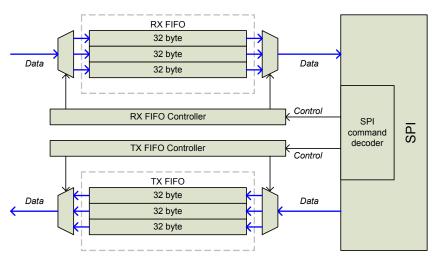

| 6.5.3    | Data FIFO                                                  | 55 |

| 6.5.4    | Interrupt                                                  | 56 |

| 6.6      | Register Map                                               | 56 |

| 6.6.1    | Register map table                                         | 56 |

| 7 USI    | B Interface                                                | 62 |

| 7.1      | Features                                                   | 62 |

| 7.2      | Functional                                                 | 63 |

| 7.3      | Control endpoints                                          | 66 |

| 7.3.1    | Control endpoint 0 implementation                          |    |

| 7.3.2    | Endpoint 0 registers                                       |    |

| 7.3.3    | Control transfer examples                                  |    |

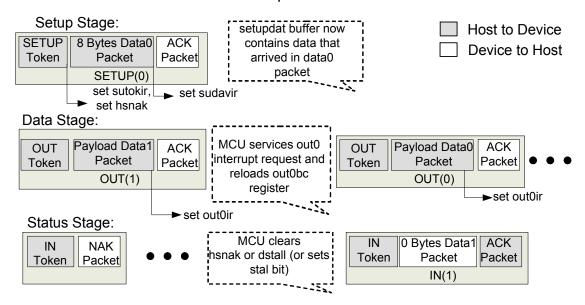

| 7.3.3.1  | Control write transfer example                             |    |

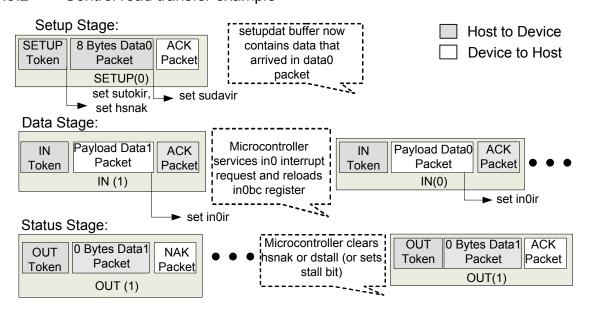

| 7.3.3.2  | Control read transfer example                              | 69 |

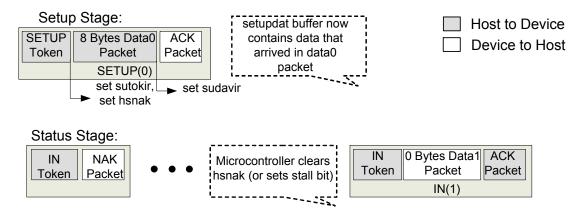

| 7.3.3.3 | No-data control transfer example                          | 69 |

|---------|-----------------------------------------------------------|----|

| 7.4     | Bulk/Interrupt endpoints                                  | 70 |

| 7.4.1   | Bulk/Interrupt endpoints implementation                   | 70 |

| 7.4.2   | Bulk/Interrupt endpoints registers                        |    |

| 7.4.3   | Bulk and interrupt endpoints initialization               | 71 |

| 7.4.3.1 | Bulk and interrupt transfers                              | 71 |

| 7.4.4   | Data packet synchronization                               | 72 |

| 7.4.5   | Endpoint pairing                                          | 73 |

| 7.4.5.1 | Paired IN endpoint status                                 | 73 |

| 7.4.5.2 | Paired OUT endpoint status                                | 73 |

| 7.5     | Isochronous endpoints                                     | 73 |

| 7.5.1   | Isochronous endpoints implementation                      | 73 |

| 7.5.2   | Isochronous endpoints registers                           |    |

| 7.5.3   | ISO endpoints initialization                              | 74 |

| 7.5.4   | ISO transfers                                             | 74 |

| 7.5.4.1 | ISO IN transfers                                          | 74 |

| 7.5.4.2 | ISO OUT transfers                                         | 75 |

| 7.6     | Memory configuration                                      | 75 |

| 7.6.1   | On-chip memory map                                        | 75 |

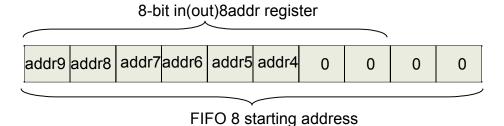

| 7.6.2   | Setting ISO FIFO size                                     | 76 |

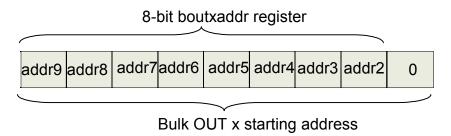

| 7.6.3   | Setting Bulk OUT size                                     |    |

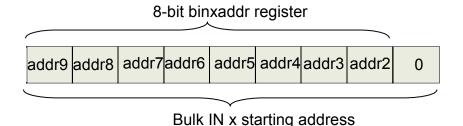

| 7.6.4   | Setting Bulk IN size                                      |    |

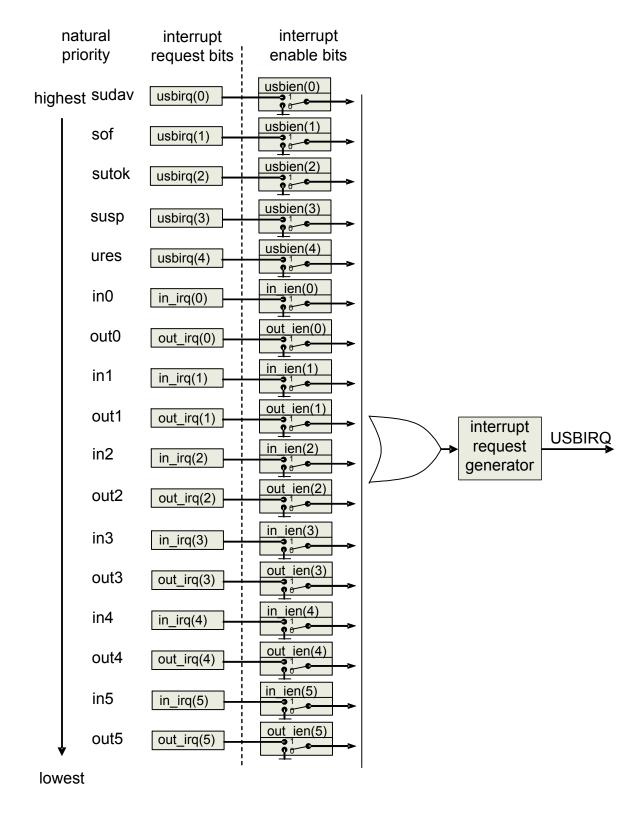

| 7.7     | The USB controller interrupts                             |    |

| 7.7.1   | Wakeup interrupt request                                  |    |

| 7.7.2   | USB interrupt request                                     |    |

| 7.7.3   | USB interrupt vectors                                     | 81 |

| 7.8     | The USB controller registers                              | 81 |

| 7.8.1   | Bulk IN data buffers (inxbuf)                             |    |

| 7.8.2   | Bulk OUT data buffers (outxbuf)                           | 82 |

| 7.8.3   | Isochronous OUT endpoint data FIFO (out8dat)              |    |

| 7.8.4   | Isochronous IN endpoint data FIFOs (in8dat)               | 82 |

| 7.8.5   | Isochronous data bytes counter (out8bch/out8bcl)          |    |

| 7.8.6   | Isochronous transfer error register (isoerr)              |    |

| 7.8.7   | The zero byte count for ISO OUT endpoints (zbcout)        |    |

| 7.8.8   | Endpoints 0 to 5 IN interrupt request register (in irq)   |    |

| 7.8.9   | Endpoints 0 to 5 OUT interrupt request register (out_irq) | 83 |

| 7.8.10  | The USB interrupt request register (usbirq)               |    |

| 7.8.11  | Endpoint 0 to 5 IN interrupt enables (In ien)             |    |

| 7.8.12  | Endpoint 0 to 5 OUT interrupt enables (out_ien)           | 84 |

| 7.8.13  | USB interrupt enable (usbien)                             |    |

| 7.8.14  | Endpoint 0 control and status register (ep0cs)            |    |

| 7.8.15  | Endpoint 0 to 5 IN byte count registers (inxbc)           |    |

| 7.8.16  | Endpoint 1 to 5 IN control and status registers (inxcs)   |    |

| 7.8.17  | Endpoint 0 to 5 OUT byte count registers (outxbc)         |    |

| 7.8.18  | Endpoint 1 to 5 OUT control and status registers (outxcs) |    |

| 7.8.19  | USB control and status register (usbcs)                   |    |

| 89                                                                                           |

|----------------------------------------------------------------------------------------------|

|                                                                                              |

| 89                                                                                           |

| 89                                                                                           |

| 89                                                                                           |

| 90                                                                                           |

| 90                                                                                           |

| 90                                                                                           |

| 90                                                                                           |

| 90                                                                                           |

| 90                                                                                           |

| 91                                                                                           |

| 91                                                                                           |

| 91                                                                                           |

| 91                                                                                           |

| 92                                                                                           |

| 92                                                                                           |

| 93                                                                                           |

| 93                                                                                           |

| 96                                                                                           |

| 96                                                                                           |

| 96                                                                                           |

| 97                                                                                           |

| 98                                                                                           |

|                                                                                              |

| 98                                                                                           |

| 98<br>98                                                                                     |

| 98                                                                                           |

| 98<br>99                                                                                     |

| 98<br>99<br><b>100</b>                                                                       |

| 98<br>99                                                                                     |

| 98<br>99<br><b>100</b><br>100                                                                |

| 98<br>99<br><b>100</b><br>100<br>100                                                         |

| 98<br>99<br><b>100</b><br>100<br>100                                                         |

| 98<br>99<br><b>100</b><br>100<br>100<br>101                                                  |

| 98<br>99<br>100<br>100<br>100<br>101<br>101                                                  |

| 98<br>99<br>100<br>100<br>100<br>101<br>101                                                  |

| 98<br>99<br>100<br>100<br>100<br>101<br>101<br>102                                           |

| 98<br>99<br>100<br>100<br>100<br>101<br>101<br>102<br>102                                    |

| 98<br>99<br>100<br>100<br>100<br>101<br>101<br>102<br>102<br>103                             |

| 98<br>99<br>100<br>100<br>100<br>101<br>102<br>102<br>103<br>103                             |

| 98<br>99<br>100<br>100<br>101<br>101<br>102<br>102<br>103<br>103                             |

| 98<br>99<br>100<br>100<br>100<br>101<br>102<br>102<br>103<br>103<br>103                      |

| 98<br>99<br>100<br>100<br>100<br>101<br>102<br>102<br>103<br>103<br>103<br>103               |

| 98<br>99<br>100<br>100<br>101<br>101<br>102<br>102<br>103<br>103<br>103<br>103               |

| 98<br>99<br>100<br>100<br>100<br>101<br>102<br>102<br>103<br>103<br>103<br>103<br>104<br>104 |

|                                                                                              |

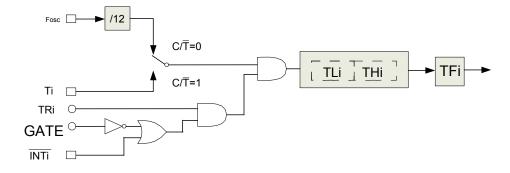

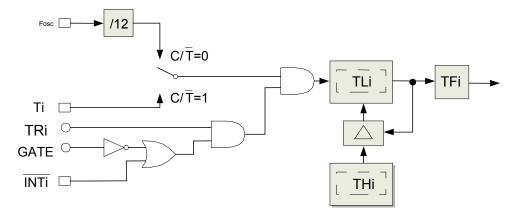

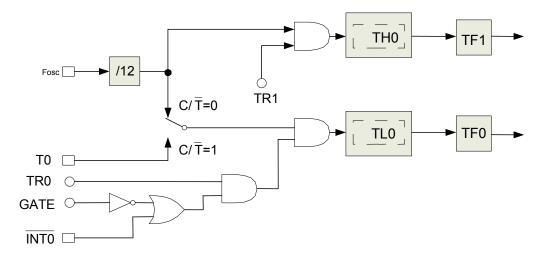

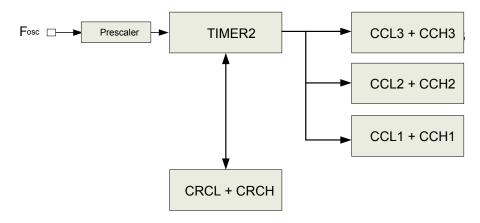

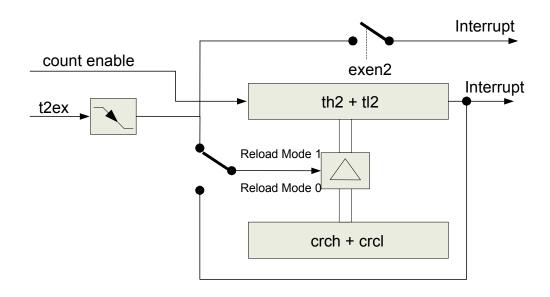

| 11.2.7   | Compare/Capture enable register – CCEN          | . 106 |  |  |

|----------|-------------------------------------------------|-------|--|--|

| 11.2.8   |                                                 |       |  |  |

| 11.2.9   | Compare/Reload/Capture register – CRCH, CRCL    | . 107 |  |  |

| 12 Seri  | ial Port (UART)                                 | .108  |  |  |

| 12.1     | Features                                        | . 108 |  |  |

| 12.2     | Functional description                          | . 108 |  |  |

| 12.2.1   | Serial Port 0 control register – S0CON          | . 108 |  |  |

| 12.2.2   | Serial port 0 data buffer – S0BUF               |       |  |  |

| 12.2.3   | Serial port 0 reload register – S0RELH, S0RELL  | . 109 |  |  |

| 12.2.4   | Serial Port 0 baud rate select register - WDCON | . 110 |  |  |

| 13 Inpu  | ut/Output port (GPIO)                           | .111  |  |  |

| 13.1     | Normal IO                                       | .111  |  |  |

| 13.2     | Expanded IO                                     | . 112 |  |  |

| 14 MC    | U                                               | .114  |  |  |

| 14.1     | Features                                        | . 114 |  |  |

| 14.2     | MCU registers                                   | . 115 |  |  |

| 14.3     | Arithmetic Logic Unit (ALU)                     | . 116 |  |  |

| 14.4     | Instruction set summary                         | . 116 |  |  |

| 14.5     | Opcode map                                      | . 120 |  |  |

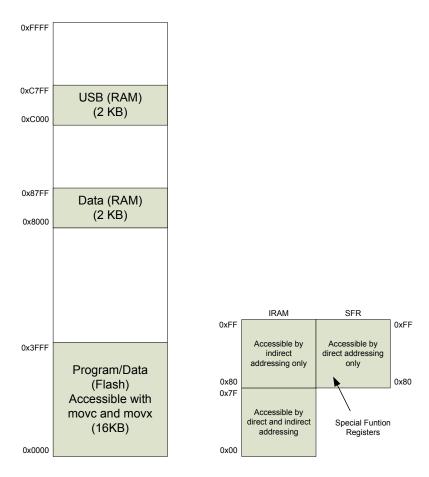

| 15 Mer   | mory and I/O organization                       | .122  |  |  |

| 15.1     | Special function registers                      | . 123 |  |  |

| 15.1.1   | Special function registers locations            | . 123 |  |  |

| 15.1.2   | Special function registers reset values         | . 124 |  |  |

| 15.1.3   | Accumulator - ACC                               | . 126 |  |  |

| 15.1.4   | B register – B                                  |       |  |  |

| 15.1.5   | Program Status Word register - PSW              |       |  |  |

| 15.1.6   | Stack Pointer – SP                              |       |  |  |

| 15.1.7   | Data Pointer – DPH, DPL                         | . 127 |  |  |

| 15.1.8   | Data Pointer 1 – DPH1, DPL1                     | . 128 |  |  |

| 15.1.9   | Data Pointer Select register – DPS              | . 128 |  |  |

| 16 Ran   | ndom Access Memory (RAM)                        | . 129 |  |  |

| 16.1     | Cycle control                                   | . 129 |  |  |

| 17 Flas  | sh Memory                                       | . 130 |  |  |

| 17.1     | Features                                        | . 130 |  |  |

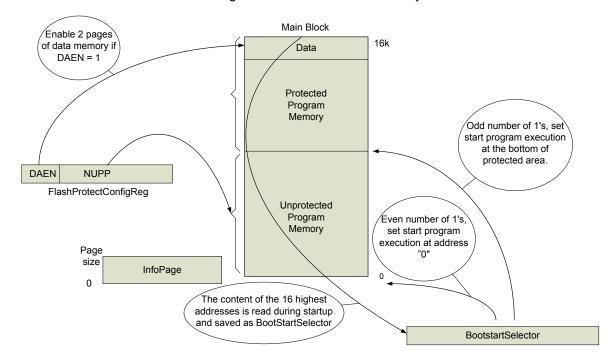

| 17.1.1   | Functional description                          | . 131 |  |  |

| 17.1.1.1 | Infopage content                                |       |  |  |

| 17.1.1.2 | Registers to control flash operations           | . 132 |  |  |

| 17.2     | Brown-out                                       |       |  |  |

| 17.3     | Flash programming from the MCU                  | . 132 |  |  |

| 17.3.1   | MCU write and erase of the main block           | . 132 |  |  |

| 17.3.2   | Boot, start of code execution                   |       |  |  |

| 17.4     | Flash programming through USB                   |       |  |  |

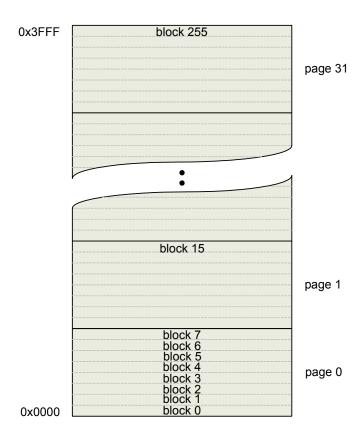

| 17.4.1   | Flash Layout                                    | . 134 |  |  |

| 17.4.2   | USB Protocol                                    |       |  |  |

| 17.4.2.1 | Firmware version (cmd 0x01)                     | . 135 |  |  |

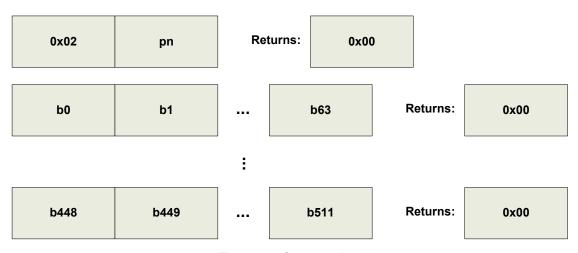

| 17.4.2.2 | Flash page write (cmd 0x02)                     | . 135 |  |  |

| Read flash block (cmd 0x03)                        | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash page erase (cmd 0x04)                        | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

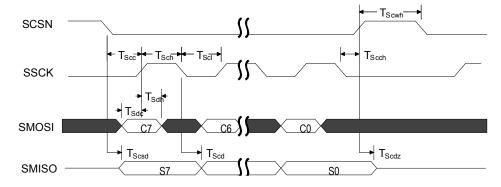

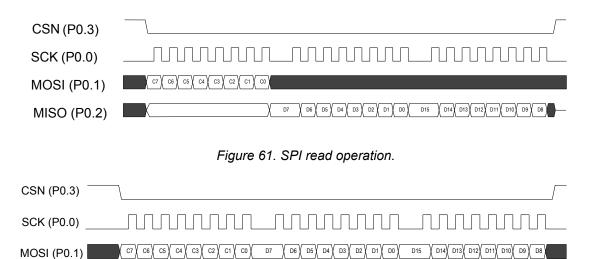

| Flash programming through SPI                      | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI commands                                       | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Write enable (WREN)                                | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Write disable (WRDIS)                              | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Read status register (RDSR)                        | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Write status register (WRSR)                       | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| READ                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PROGRAM                                            | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ERASE PAGE                                         | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ERASE ALL                                          | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Read Flash Protect Configuration register (RDFPCR) | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Read Disable Infopage (RDISIP)                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Enable Debugger (ENDEBUG)                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPI Readback disable                               | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Standalone programming requirements                | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Clock requirements                                 | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Power supply requirements                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Signal pin requirements                            | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| , e                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Features                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Functional description                             | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| •                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| b) Executing calculation                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| c) Reading the result from the MDx registers       | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| f) The mdef flag                                   | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| f) The mdef flagg) The mdov flag                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ,                                                  | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| g) The mdov flag                                   | 149<br><b>150</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

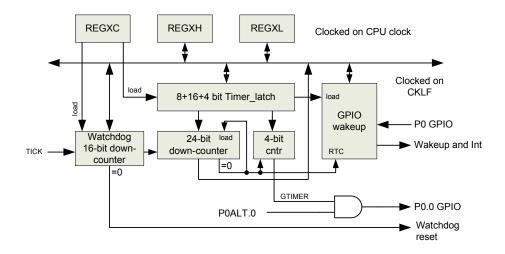

| g) The mdov flagchdog and wakeup functions         | 149150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| g) The mdov flagchdog and wakeup functions         | 149150150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| g) The mdov flag                                   | 149150150150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| g) The mdov flag                                   | 149<br>150<br>150<br>150<br>150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| g) The mdov flag                                   | 149150150150150150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| g) The mdov flag                                   | 149150150150150151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| g) The mdov flag                                   | 149150150150150151151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| g) The mdov flag                                   | 149150150150150151151151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| g) The mdov flag                                   | 149150150150150151151151154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                    | Flash programming through SPI SPI commands Write enable (WREN) Write disable (WRDIS) Read status register (RDSR) Write status register (WRSR) READ PROGRAM ERASE PAGE ERASE ALL Read Flash Protect Configuration register (RDFPCR) Read Disable Infopage (RDISIP) Read Disable MainBlock (RDISMB) Enable Debugger (ENDEBUG) SPI Readback disable Standalone programming requirements Clock requirements Power supply requirements Signal pin requirements In circuit programming over SPI SPI programming sequences Erasing the infopage U – Multiply Divide Unit Features Functional description a) Loading the MDx registers b) Executing calculation c) Reading the result from the MDx registers d) Normalizing e) Shifting |

| 20.2.2  | Power down control – PWRDWN                             | 156 |

|---------|---------------------------------------------------------|-----|

| 20.2.3  | Reset result – RSTRES                                   | 156 |

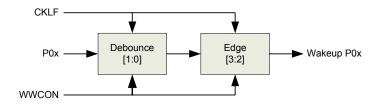

| 20.2.4  | Wakeup configuration register – WUCONF                  | 157 |

| 20.2.5  | Power control register - PCON                           | 157 |

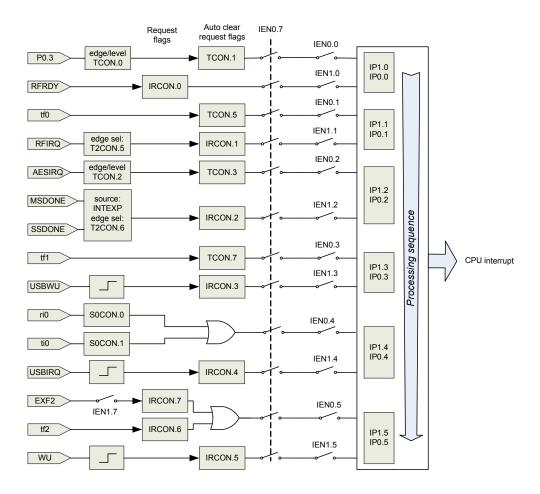

| 21 Inte | errupts                                                 |     |

| 21.1    | Features                                                | 158 |

| 21.2    | Functional description                                  | 159 |

| 21.2.1  | Interrupt enable 0 register – IEN0                      | 159 |

| 21.2.2  | Interrupt enable 1 register – IEN1                      | 159 |

| 21.2.3  | Interrupt priority registers – IP0, IP1                 | 160 |

| 21.2.4  | Interrupt request control registers – IRCON             | 161 |

| 22 HW   | debugger support                                        | 162 |

| 22.1    | Features                                                |     |

| 22.2    | Functional description                                  | 162 |

| 23 Per  | ripheral information                                    | 163 |

| 23.1    | Antenna output                                          |     |

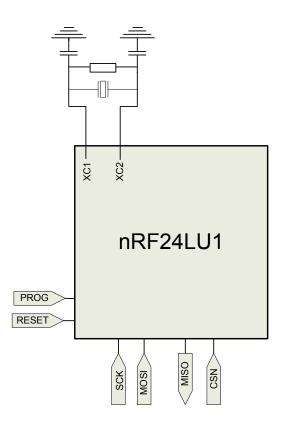

| 23.2    | Crystal oscillator                                      | 163 |

| 23.3    | PCB layout and decoupling guidelines                    | 163 |

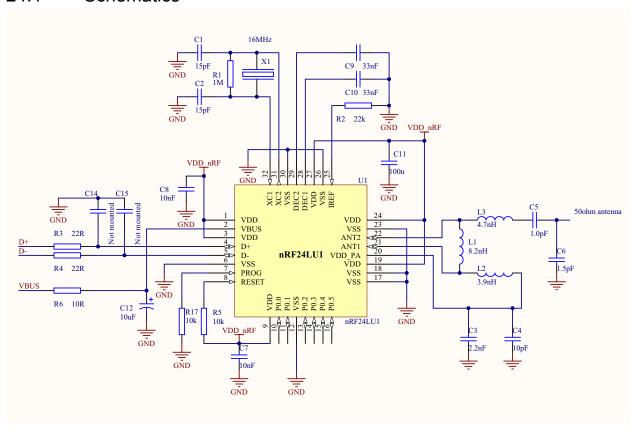

| 24 Ap   | olication example                                       |     |

| 24.1    | Schematics                                              |     |

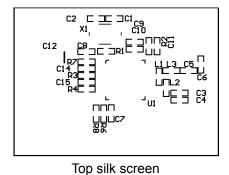

| 24.2    | Layout                                                  | 165 |

| 24.3    | Bill Of Materials (BOM)                                 | 166 |

| 25 Me   | chanical specifications                                 |     |

| 26 Ord  | lering information                                      | 168 |

| 26.1    | Package marking                                         | 168 |

| 26.1.1  | Abbreviations                                           | 168 |

| 26.2    | Product options                                         | 168 |

| 26.2.1  | RF silicon                                              | 168 |

| 26.2.2  | Development tools                                       | 168 |

| 27 Gld  | ssary of terms                                          | 169 |

| Ap      | pendix A - (USB memory configurations)                  | 170 |

|         | Configuration 1                                         |     |

|         | Configuration 2                                         | 170 |

|         | Configuration 3                                         | 171 |

|         | Configuration 4                                         | 172 |

| Anı     | pendix B - Configuration for compatibility with nRF24XX | 173 |

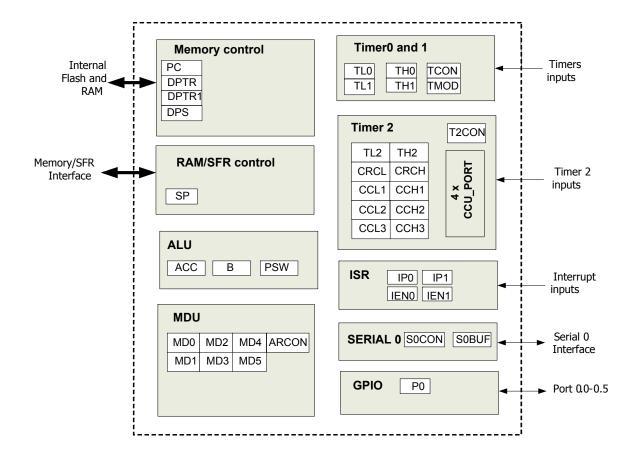

#### 1 Introduction

The nRF24LU1 is a unique single chip solution for compact USB dongles. By integrating a nRF24L01 compatible 2.4GHz RF transceiver it supports a wide range of applications including PC peripherals, sports accessories and game peripherals.

With an air data rate of 2 Mbps combined with full speed USB, supporting up to 12 Mbps, the nRF24LU1 meets the stringent performance requirements of applications such as wireless mouse, game controllers and media center remote controls with displays.

#### The nRF24LU1 integrates:

- A nRF24L01 compatible 2.4GHz RF transceiver

- A full speed USB 2.0 compliant device controller

- An 8-bit microcontroller

- 16 kbytes of flash memory

All this is packaged on a compact 5x5mm package, low cost external BOM.

With an internal voltage regulator that enables the chip to be powered directly from the USB bus, it does not require an external voltage regulator, saving cost and board space. With a fully integrated RF synthesizer and PLL for the USB no external loop filters, resonators or VCO varactor diodes are required. All that is needed is a low cost ±60ppm 16MHz crystal, matching circuitry and the antenna.

The main benefits of nRF24LU1 are:

- Very compact USB dongle

- Low cost external BOM

- No need for an external voltage regulator

- Single low cost ±60ppm 16MHz crystal

- Flash memory for firmware upgrades

#### 1.1 Features

#### Features of the nRF24LU1 include:

- Fast 8-bit MCU:

- ▶ Intel MCS 51 compliant instruction set

- ▶ Reduced instruction cycle time, up to 12x compared to legacy 8051

- ▶ 32 bit multiplication division unit

- Memory:

- ▶ 16 kbytes of on-chip flash memory with security features

- ▶ 2 kbytes of on-chip RAM memory

- ▶ Pre-programmed USB bootloader in the on-chip flash memory.

- 6 programmable digital input/output pins configurable as:

- ▶ GPIO

- ▶ SPI master

- ▶ SPI slave

- External interrupts

- ▶ Timer inputs

- ▶ Full duplex serial port

- Debug interface

- · High-performance 2.4GHz RF-transceiver

- ▶ True single chip GFSK transceiver

- ► Complete OSI Link Layer in hardware

- ▶ Enhanced ShockBurst™

- ▶ Auto ACK & retransmit

- ▶ Address and CRC computation

- ▶ On the air data rate 1 or 2Mbps

- ▶ Digital interface (SPI) speed 0-8 Mbps

- ▶ 125 RF channel operation

- ▶ Short switching time enable frequency hopping

- ► Fully compatible with nRF24LXX

- ▶ RF compatible with nRF2401A, nRF2402, nRF24E1, nRF24E2 in 1 Mbps mode

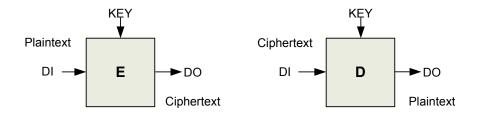

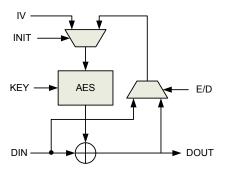

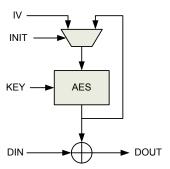

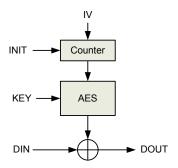

- AES encryption/decryption HW-block with 128 bits key length

- ▶ ECB Electronic Code Book mode

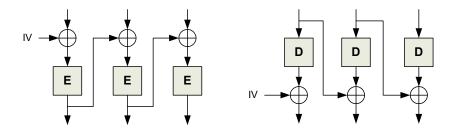

- ▶ CBC Cipher Block Chaining

- ▶ CFB Cipher FeedBack mode

- ▶ OFB Output FeedBack mode

- ▶ CTR Counter mode

- Full speed USB 2.0 compliant device controller supporting:

- ▶ Data transfer rates up to 12 Mbit/s

- ► Control, Interrupt, Bulk and ISO data transfer

- ► Endpoint 0 for control

- ▶ 5 input and 5 output Bulk/Interrupt endpoints

- ▶ 1 input and 1 output iso-synchronous endpoints

- ▶ Total 512 bytes of USB buffer endpoint memory sharable between endpoints

- On-chip USB transceiver PHY

- ▶ On-chip pull-up resistor on D+ line with software controlled disconnect

- · Power management function:

- ▶ Low power design supporting fully static stop/ standby/ suspend modes

- ▶ Programmable MCU clock frequency from 64 kHz to 16 MHz

- ▶ On-chip voltage regulators supporting low power mode (supplied from USB power)

- ▶ Watchdog and wakeup functionality running in low power mode

- On-chip oscillator and PLL to obtain full speed USB operation and to reduce the need for external components

- On-chip power on reset generator and brown-out detector

- On-chip support for HW debugger, supported by Keil development tools.

- Complete firmware platform available:

- ▶ Hardware abstraction layer (HAL) Functions

- ▶ USB library Functions

- ▶ Standard and HID specific USB Requests and Descriptors

- ▶ nRF24LU1 Library functions

- ► AES HAL

- ▶ Application examples

- ▶ Device Firmware Upgrade

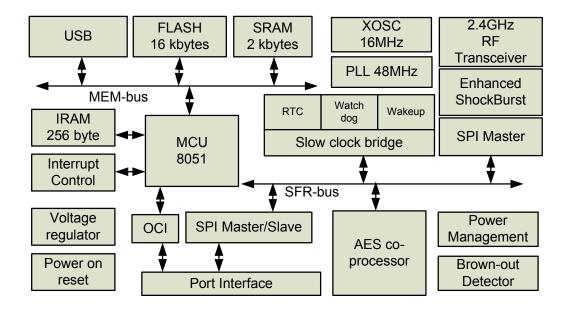

# 1.2 Block diagram

Figure 1. nRF24LU1 block diagram

To find more information on the block diagram, see <u>Table 1</u>. below:

| Name                     | Reference                  |  |

|--------------------------|----------------------------|--|

| USB                      | chapter 7 on page 62       |  |

| FLASH                    | chapter 17 on page 130     |  |

| SRAM                     | chapter 15 on page 122     |  |

| 2.4GHz RF transceiver    | chapter 6 on page 26       |  |

| XOSC                     | section 23.2 on page 163   |  |

| Enhanced ShockBurst      | section 6.4 on page 33     |  |

| IRAM                     | chapter 16 on page 129     |  |

| MCU                      | chapter 14 on page 114     |  |

| RTC, Watchdog and Wakeup | see chapter 19 on page 150 |  |

| SPI Master               | chapter 9 on page 96       |  |

| Interrupt control        | chapter 21 on page 158     |  |

| Name               | Reference                                      |

|--------------------|------------------------------------------------|

| SPI master/slave   | chapter 9 on page 96 and chapter 10 on page 98 |

| AES co-processor   | chapter 8 on page 91                           |

| Power management   | chapter 20 on page 154                         |

| Brown-out detector | section 17.2 on page 132                       |

Table 1. Block diagram cross references

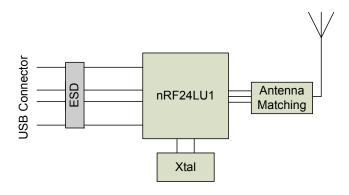

# 1.3 Typical system usage

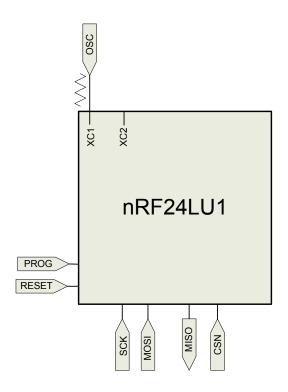

Figure 2. Typical system usage

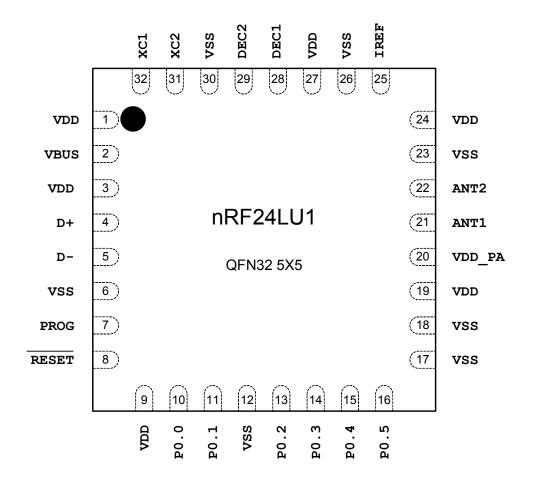

# 2 Pin Information

# 2.1 Pin Assignments

Figure 3. nRF24LU1 pin assignment (top view) for a QFN32 5x5 mm package.

#### 2.2 Pin Functions

| Pin             | Name       | Type          | Description                                         |  |

|-----------------|------------|---------------|-----------------------------------------------------|--|

| 21, 22          | ANT1, ANT2 | RF            | Antenna connection                                  |  |

| 5, 4            | D-, D+     | Digital I/O   | USB data                                            |  |

| 28, 29          | DEC1, DEC2 | Power         | Positive Digital Supply output for de-coupling pur- |  |

|                 |            |               | poses                                               |  |

| 25              | IREF       | Analog Input  | Reference current                                   |  |

| 10, 11, 13, 14, | P0.0-P0.5  | Digital I/O   | General purpose data Port 0, bit 0 - 5              |  |

| 15, 16          |            |               |                                                     |  |

| 7               | PROG       | Digital Input | Reserved for programming the flash                  |  |

| 8               | RESET      | Digital Input | Reset for MCU, active low                           |  |

| 2               | VBUS       | Power         | USB power connection                                |  |

| 1, 3, 9,        | VDD        | Power         | Alternative power supply pins. The VDD pins must    |  |

| 19, 24, 27      |            |               | always be connected and de-coupled externally.      |  |

| 20              | VDD_PA     | Power Output  | Power Supply (+1.8V) to Power Amplifier             |  |

| 6, 12, 17, 18,  | vss        | Power         | Ground (0V)                                         |  |

| 23, 26, 30      |            |               |                                                     |  |

| 32, 31          | XC1, XC2   | Analog Input  | Crystal connection                                  |  |

Table 2. nRF24LU1 pin functions.

#### 2.2.1 Antenna pins

ANT1 and ANT2 are connections for the external antenna (both receive and transmit).

#### 2.2.2 **USB** pins

D- and D+ are the connections to the USB data lines. External ESD protection is recommended.

## 2.2.3 Power supply pins

**VBUS** and **VSS** are the power supply and ground pins. The nRF24LU1 can operate from a single power supply.

The nRF24LU1 contains an on-chip regulator that produces +3.3V on the VDD pins, from the VBUS supply line (4.0 – 5.25 V). Alternatively, the VBUS pin can be left open and the VDD pins may be fed from an external 3.3V supply. In this case, the on-chip 3.3V regulator is switched off.

Additional on-chip regulators produce voltages for internal analog and digital functions blocks. External decoupling capacitors are required on DEC1 and DEC2.

VDD\_PA is a 1.8V output that is used to switch on an external RF Power Amplifier.

### 2.2.4 PROG pin

When set high this pin enables external flash programming and Port 0 is configured as a slave SPI port. The PROG pin needs an external pull-down resistor.

#### 2.2.5 Reference current pin

**IREF** pin must be connected to an external resistor.

# 2.2.6 Port pins

P0.0 - P0.5 are six general purpose I/O pins. Their functions are described in chapter 13 on page 111.

#### 2.2.7 External RESET Pin

A logic 0 on the RESET pin forces the nRF24LU1 to a known start-up state.

## 2.2.8 Crystal oscillator pins

xc1 and xc2 are connections to an external crystal.

# 3 Absolute Maximum Ratings

Maximum ratings are the extreme limits that you can expose the nRF24LU1 to without permanently damaging it. Exposure to absolute maximum ratings for prolonged periods of time may affect device reliability.

| Operating conditions    | Minimum | Maximum | Units |

|-------------------------|---------|---------|-------|

| Supply voltages         |         |         |       |

| VBUS                    | -0.3V   | +5.75   | V     |

| VSS                     |         | 0       | V     |

| VDD                     | +3.0    | +3.6    | V     |

| Input voltage           |         |         |       |

| VI                      | -0.3    | +3.6    | V     |

| Total Power Dissipation |         |         |       |

| PD (TA=85°C)            |         | 180     | mW    |

| Temperatures            |         |         |       |

| Operating Temperature   | -40     | +85     | °C    |

| Storage Temperature     | -40     | +125    | °C    |

Table 3. Absolute maximum ratings

# 4 Operating Conditions

| Symbol | Parameter (condition)      | Notes | Min. | Тур. | Max. | Units |

|--------|----------------------------|-------|------|------|------|-------|

| VBUS   | Supply voltage             |       | 4.0  | 5    | 5.25 | V     |

| VDD    | Alternative supply voltage |       | 3.05 | 3.27 | 3.5  | V     |

| TEMP   | Operating Temperature      |       | -40  | +27  | +85  | °C    |

Table 4. Operating conditions

# 5 Electrical Specifications

This section contains electrical and timing specifications.

# 5.1 Power consumption and timing characteristics

| Symbol       | Parameter (condition)                        | Notes    | Min. | Тур. | Max. | Units |

|--------------|----------------------------------------------|----------|------|------|------|-------|

| ISUP         | Average current in supply mode               | а        |      | 24   |      | mA    |

| ISTANDBY     | Supply current in standby mode               | b        |      | 480  |      | μA    |

|              | MCU                                          |          |      | I .  | I.   |       |

|              | Running @ 16MHz, generated from PLL          |          |      | 6    |      | mA    |

|              | Running @ 12MHz, generated from PLL          |          |      | 5    |      | mA    |

|              | Running @ 8MHz, generated from PLL           |          |      | 4    |      | mA    |

|              | Running @ 4MHz, generated from PLL           |          |      | 3    |      | mA    |

| IMCU1.6MPL   | Running @ 1.6MHz, generated from PLL         |          |      | 2.4  |      | mA    |

| IMCU4MXO     | Running @ 4MHz, generated from XO            |          |      | 2.4  |      | mA    |

| IMCU1.6MXO   | Running @ 1.6MHz, generated from XO          |          |      | 1.75 |      | mA    |

|              | Running @ 0.32MHz, generated from XO         |          |      | 1.4  |      | mA    |

| IMCU64KXO    | Running @ 0.064MHz, generated from XO        |          |      | 1.35 |      | mA    |

| Trst_act     | From RESET to MCU active                     |          |      |      | 2    | ms    |

| Tint_act     | From INTERRUPT to MCU active                 |          |      |      | 300  | μs    |

| Tact_stby    | MCU from active to standby                   | С        |      |      | 32   | μs    |

|              | RF Transceiver                               | <u> </u> |      | l.   | l-   |       |

| ITX          | RF Transceiver TX current @0dBm output power |          |      | 11   |      | mA    |

| IRX          | RF Transceiver RX current                    |          |      | 12   |      | mA    |

| Trfpwd act   | RF Transceiver from standby to active        | С        |      |      | 130  | μs    |

| Trst radio   | From RESET to RF Transceiver power           |          |      |      | 50   | ms    |

| _            | down                                         |          |      |      |      |       |

|              | USB                                          |          |      |      | •    | •     |

| IUSB         | USB active current                           |          |      | 4.5  |      | mA    |

| Tusb_wh      | USB wakeup from host                         |          |      |      | 500  | μs    |

| Tusb_wmcu    | USB wakeup from MCU                          |          |      |      | 300  | μs    |

| Tusbact_susp | USB from active to suspend                   | С        |      |      | 32   | μs    |

|              | PLL                                          |          |      |      |      |       |

| Tplloff_on   | PLL from off to on time                      | c d      |      |      | 250  | μs    |

| Tpllon_off   | PLL from on to off time                      | c d      |      |      | 32   | μs    |

a. For radio receive at 2Mbps and USB transmit

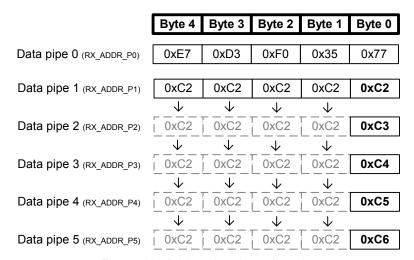

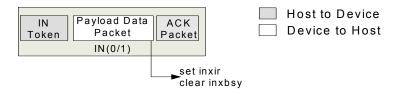

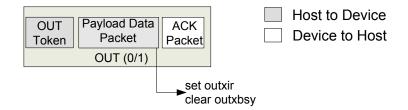

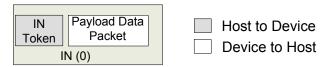

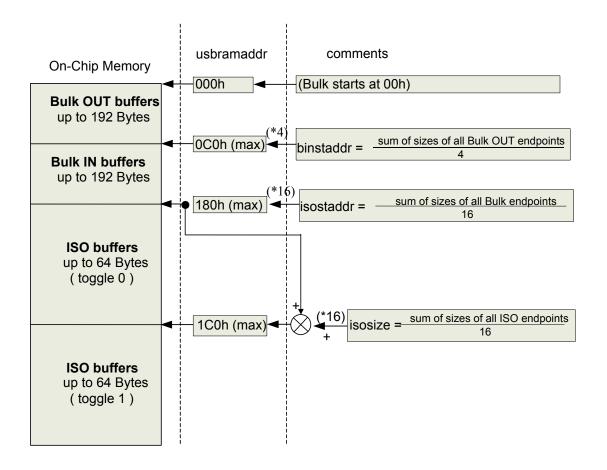

Table 5. Power consumption and timing characteristics