# TPS2010, TPS2011, TPS2012, TPS2013 POWER-DISTRIBUTION

SLVS097A - DECEMBER 1994 - REVISED AUGUST 1995

- 95-mΩ Max (5.5-V Input) High-Side MOSFET

Switch With Logic Compatible Enable Input

- Short-Circuit and Thermal Protection

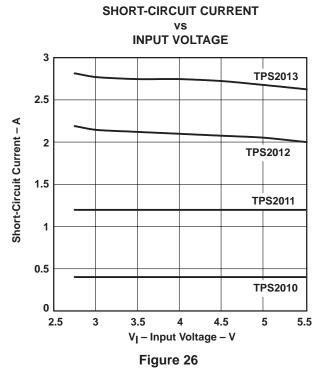

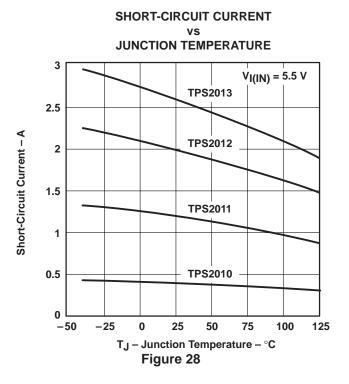

- Typical Short-Circuit Current Limits:

0.4 A, TPS2010; 1.2 A, TPS2011;

2 A, TPS2012; 2.6 A, TPS2013

- Electrostatic-Discharge Protection, 12-kV Output, 6-kV All Other Terminals

- Controlled Rise and Fall Times to Limit Current Surges and Minimize EMI

- SOIC-8 Package Pin Compatible With the Popular Littlefoot™ Series When GND Is Connected

- 2.7-V to 5.5-V Operating Range

- 10-μA Maximum Standby Current

- Surface-Mount SOIC-8 and TSSOP-14 Packages

- -40°C to 125°C Operating Junction Temperature Range

# description

The TPS201x family of power-distribution switches is intended for applications where heavy capacitive loads and short circuits are likely to be encountered. The high-side switch is a 95-m $\Omega$  N-channel MOSFET. Gate drive is provided by an internal driver and charge pump designed to control the power switch rise times and fall times to minimize current surges during switching. The charge pump operates at 100 kHz, requires no external components, and allows operation from supplies as low as 2.7 V. When the output load exceeds the current-limit threshold or a short circuit is present, the TPS201x limits the output current to a safe level by switching into a constant-current mode. Continuous heavy overloads and short circuits increase power dissipation in the switch and cause the junction temperature to rise. If the junction temperature reaches approximately 180°C, a thermal protection circuit shuts the switch off to prevent damage. Recovery from thermal shutdown is automatic once the device has cooled sufficiently.

The members of the TPS201x family differ only in short-circuit current threshold. The TPS2010 is designed to limit at 0.4-A load; the other members of the family limit at 1.2 A, 2 A, and 2.6 A (see the available options table). The TPS201x family is available in 8-pin small-outline integrated circuit (SOIC) and 14-pin thin shink small-outline (TSSOP) packages and operates over a junction temperature range of −40°C to 125°C. Versions in the 8-pin SOIC package are drop-in replacements for Siliconix's Littlefoot™ power PMOS switches, except that GND must be connected.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLVS097A - DECEMBER 1994 - REVISED AUGUST 1995

#### **AVAILABLE OPTIONS**

| ТЈ             | RECOMMENDED MAXIMUM         | TYPICAL SHORT-CIRCUIT               | PACKAG       | CHIP                       |             |

|----------------|-----------------------------|-------------------------------------|--------------|----------------------------|-------------|

|                | CONTINUOUS LOAD CURRENT (A) | OUTPUT CURRENT LIMIT AT 25°C<br>(A) | SOIC<br>(D)† | TSSOP<br>(PW) <sup>‡</sup> | FORM<br>(Y) |

|                | 0.2                         | 0.4                                 | TPS2010D     | TPS2010PWLE                | TPS2010Y    |

| 40°C to 135°C  | 0.6                         | 1.2                                 | TPS2011D     | TPS2011PWLE                | TPS2011Y    |

| -40°C to 125°C | 1                           | 2                                   | TPS2012D     | TPS2012PWLE                | TPS2012Y    |

|                | 1.5                         | 2.6                                 | TPS2013D     | TPS2013PWLE                | TPS2013Y    |

<sup>†</sup> The D package is available taped and reeled. Add an R suffix to device type (e.g., TPS2010DR).

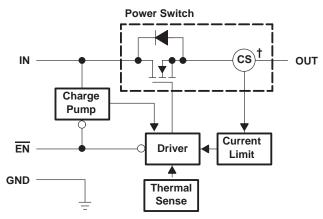

# functional block diagram

†Current sense

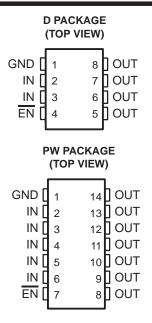

# **Terminal Functions**

| 1      | ERMINA | L    |     |                                                |

|--------|--------|------|-----|------------------------------------------------|

| NAME   | NO.    |      | 1/0 | DESCRIPTION                                    |

| NAIVIE | D      | PW   |     |                                                |

| EN     | 4      | 7    | I   | Enable input. Logic low turns power switch on. |

| GND    | 1      | 1    | I   | Ground                                         |

| IN     | 2, 3   | 2-6  | I   | Input voltage                                  |

| OUT    | 5-8    | 8-14 | 0   | Power-switch output                            |

# detailed description

# power switch

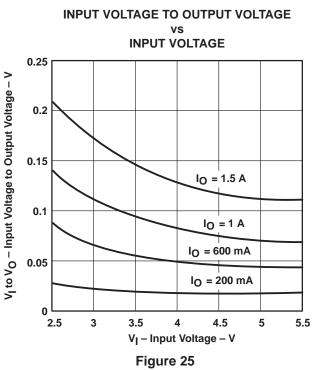

The power switch is an N-channel MOSFET with a maximum on-state resistance of 95 m $\Omega$  (V<sub>I(IN)</sub> = 5.5 V), configured as a high-side switch.

#### charge pump

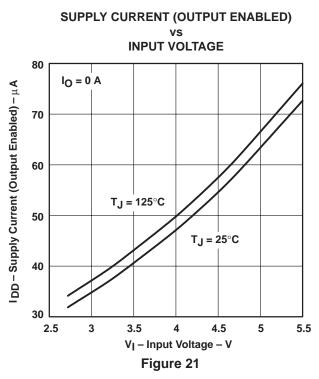

An internal 100-kHz charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V and requires very little supply current.

<sup>‡</sup>The PW package is only available left-end taped and reeled (indicated by the LE suffix on the device type; e.g., TPS2010PWLE).

SLVS097A - DECEMBER 1994 - REVISED AUGUST 1995

#### detailed description (continued)

#### driver

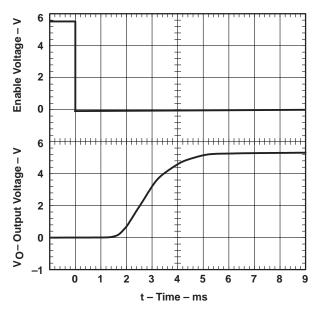

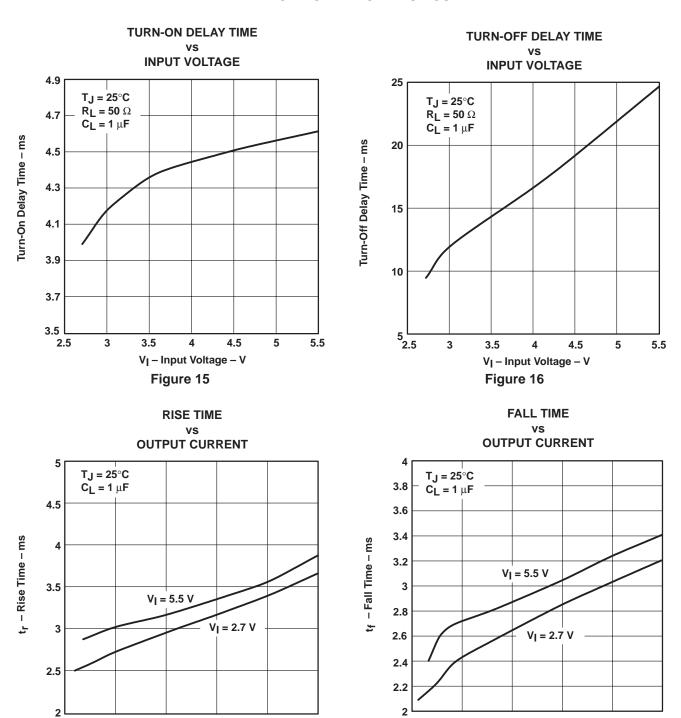

The driver controls the gate voltage of the power switch. To limit large current surges and reduce the associated electromagnetic interference (EMI) produced, the driver incorporates circuitry that controls the rise times and fall times of the output voltage. The rise and fall times are typically in the 2-ms to 4-ms range instead of the microsecond or nanosecond range for a standard FET.

#### enable (EN)

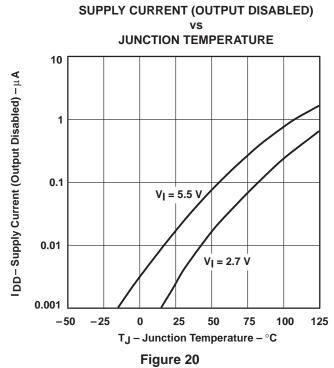

A logic high on the  $\overline{EN}$  input turns off the power switch and the bias for the charge pump, driver, and other circuitry to reduce the supply current to less than 10  $\mu$ A. A logic zero input restores bias to the drive and control circuits and turns the power on. The enable input is compatible with both TTL and CMOS logic levels.

#### current sense

A sense FET monitors the current supplied to the load. The sense FET is a much more efficient way to measure current than conventional resistance methods. When an overload or short circuit is encountered, the current-sense circuitry sends a control signal to the driver. The driver in turn reduces the gate voltage and drives the power FET into its linear region, which switches the output into a constant current mode and simply holds the current constant while varying the voltage on the load.

#### thermal sense

An internal thermal-sense circuit shuts the power switch off when the junction temperature rises to approximately 180°C. Hysteresis is built into the thermal sense, and after the device has cooled approximately 20 degrees, the switch turns back on. The switch continues to cycle off and on until the fault is removed.

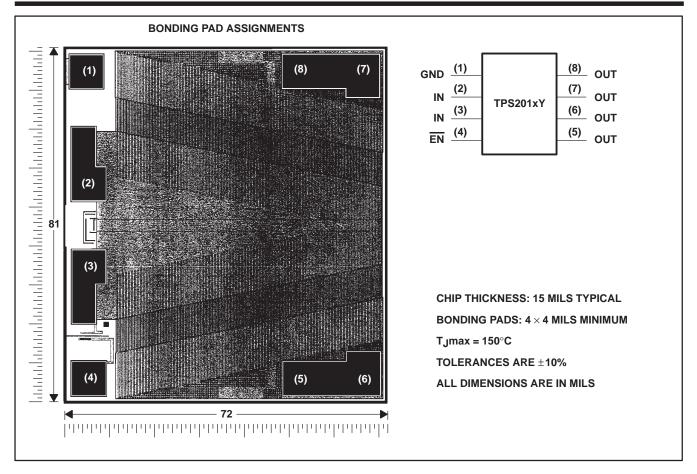

# **TPS201xY** chip information

This chip, when properly assembled, displays characteristics similar to the TPS201xC. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chip may be mounted with conductive epoxy or a gold-silicon preform.

SLVS097A - DECEMBER 1994 - REVISED AUGUST 1995

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Input voltage range, V <sub>I(IN)</sub> (see Note 1) |                                               |

|------------------------------------------------------|-----------------------------------------------|

| Output voltage range, $\dot{V}_{O}$ (see Note 1)     | $-0.3 \text{ V to V}_{I(IN)} + 0.3 \text{ V}$ |

| Input voltage range, V <sub>I</sub> at <del>EN</del> | –0.3 V to 7 V                                 |

| Continuous output current, IO                        | internally limited                            |

|                                                      |                                               |

| Continuous total power dissipation                   | See Dissipation Rating Table                  |

| Continuous total power dissipation                   |                                               |

| ·                                                    | -40°C to 125°C<br>-65°C to 150°C              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: All voltages are with respect to GND.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \leq 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|-----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| D       | 725 mW                                                                      | 5.8 mW/°C                                      | 464 mW                                | 145 mW                                 |

| PW      | 700 mW                                                                      | 5.6 mW/°C                                      | 448 mW                                | 140 mW                                 |

# recommended operating conditions

|                                     |           | MIN | MAX | UNIT |

|-------------------------------------|-----------|-----|-----|------|

| Input voltage, VI(IN)               |           | 2.7 | 5.5 | V    |

| Input voltage, V <sub>I</sub> at EN |           | 0   | 5.5 | V    |

| Continuous output current, IO       | TPS2010   | 0   | 0.2 |      |

|                                     | TPS2011   | 0   | 0.6 | ۸    |

|                                     | TPS2012   | 0   | 1   | Α    |

|                                     | TPS2013   | 0   | 1.5 |      |

| Operating virtual junction temper   | ature, TJ | -40 | 125 | °C   |

# electrical characteristics over recommended operating junction temperature range, $V_{I(IN)} = 5.5 \text{ V}$ , $I_O = \text{rated current}$ , $\overline{EN} = 0 \text{ V}$ (unless otherwise noted)

# power switch

| PARAMETER      |                        | TEST CONDITIONS <sup>†</sup> |                                           | TPS20 | UNIT  |     |            |

|----------------|------------------------|------------------------------|-------------------------------------------|-------|-------|-----|------------|

|                |                        | 1_0.                         |                                           | MIN   | TYP   | MAX |            |

|                |                        | $V_{I(IN)} = 5.5 V,$         | T <sub>J</sub> = 25°C                     |       | 75    | 95  |            |

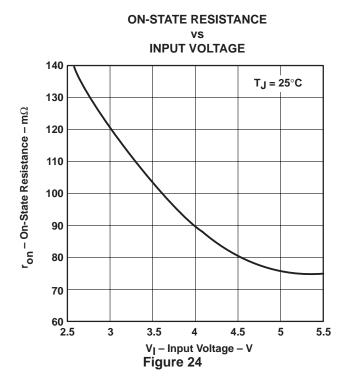

|                | On-state resistance    | $V_{I(IN)} = 4.5 \text{ V},$ | T <sub>J</sub> = 25°C                     |       | 80    | 110 | <b>m</b> O |

|                | On-state resistance    | $V_{I(IN)} = 3 V$            | T <sub>J</sub> = 25°C                     |       | 120   | 175 | mΩ         |

|                |                        | $V_{I(IN)} = 2.7 \text{ V},$ | $T_J = 25^{\circ}C$                       |       | 140   | 215 |            |

|                | Output leakage augreet | <del></del>                  | T <sub>J</sub> = 25°C                     |       | 0.001 | 1   | ^          |

|                | Output leakage current | $\overline{EN} = V_{I(IN)}$  | -40°C ≤ T <sub>J</sub> ≤ 125°C            |       |       | 10  | μΑ         |

|                | Output rise time       | $V_{I(IN)} = 5.5 V,$         | $T_J = 25^{\circ}C,  C_L = 1 \mu\text{F}$ |       | 4     |     |            |

| t <sub>r</sub> | r Output rise time     | $V_{I(IN)} = 2.7 \text{ V},$ | $T_J = 25^{\circ}C$ , $C_L = 1 \mu F$     |       | 3.8   |     | ms         |

|                | Output fall time       | $V_{I(IN)} = 5.5 V,$         | $T_J = 25^{\circ}C$ , $C_L = 1 \mu F$     |       | 3.9   |     |            |

| tf             | Output fall time       | V <sub>I(IN)</sub> = 2.7 V,  | $T_J = 25^{\circ}C,  C_L = 1 \mu\text{F}$ |       | 3.5   |     | ms         |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

# enable input (EN)

| PARAMETER |                                                    | TEST CONDITIONS                                               | TPS20<br>TPS20 | UNIT |     |    |

|-----------|----------------------------------------------------|---------------------------------------------------------------|----------------|------|-----|----|

|           |                                                    |                                                               | MIN            | TYP  | MAX |    |

|           | High-level input voltage                           | $2.7 \text{ V} \le \text{V}_{\text{I(IN)}} \le 5.5 \text{ V}$ | 2              |      |     | V  |

|           | Low level input veltage                            | $4.5 \text{ V} \le \text{V}_{\text{I(IN)}} \le 5.5 \text{ V}$ |                |      | 0.8 | V  |

|           | Low-level input voltage                            | $2.7 \text{ V} \le \text{V}_{\text{I(IN)}} < 4.5 \text{ V}$   |                |      | 0.4 | V  |

|           | Input current                                      | $\overline{EN} = 0 \ V \ or \ \overline{EN} = V_{I(IN)}$      | -0.5           |      | 0.5 | μΑ |

| tPLH      | Propagation (delay) time, low-to-high-level output | C <sub>L</sub> = 1 μF                                         |                |      | 20  | ma |

| tPHL      | Propagation (delay) time, high-to-low-level output | C <sub>L</sub> = 1 μF                                         |                |      | 40  | ms |

#### current limit

| PARAMETER             | TEST CONDITIONS <sup>†</sup>                 |         | TPS20<br>TPS20 | UNIT |     |     |

|-----------------------|----------------------------------------------|---------|----------------|------|-----|-----|

|                       |                                              |         | MIN            | TYP  | MAX | 1 1 |

| Short-circuit current | VI(IN) = 5.5 V, OUT connected to GND, device | TPS2010 | 0.22           | 0.4  | 0.6 |     |

|                       |                                              | TPS2011 | 0.66           | 1.2  | 1.8 | А   |

|                       |                                              | TPS2012 | 1.1            | 2    | 3   | A   |

|                       |                                              | TPS2013 | 1.65           | 2.6  | 4.5 |     |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

# TPS2010, TPS2011, TPS2012, TPS2013 POWER-DISTRIBUTION

SLVS097A - DECEMBER 1994 - REVISED AUGUST 1995

electrical characteristics over recommended operating junction temperature range,  $V_{I(IN)} = 5.5 \text{ V}$ ,  $I_O = \text{rated current}$ ,  $\overline{EN} = 0 \text{ V}$  (unless otherwise noted) (continued)

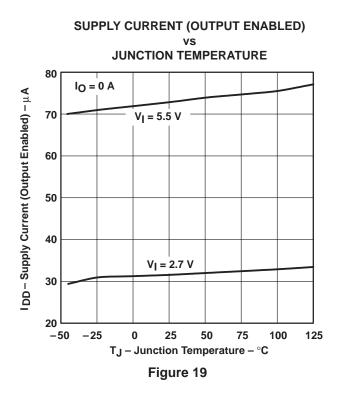

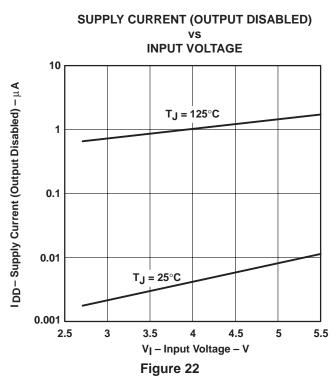

#### supply current

| PARAMETER                         | TEST CONDITIONS |                                                                       | TPS20 | UNIT  |     |    |

|-----------------------------------|-----------------|-----------------------------------------------------------------------|-------|-------|-----|----|

|                                   |                 |                                                                       | MIN   | TYP   | MAX |    |

| Supply ourrent low lovel output   | EN = VI(IN)     | T <sub>J</sub> = 25°C                                                 |       | 0.015 | 1   | μA |

| Supply current, low-level output  |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ |       |       | 10  | μΑ |

| Supply ourrent high level output  | EN = 0 V        | T <sub>J</sub> = 25°C                                                 |       | 73    | 100 |    |

| Supply current, high-level output |                 | -40°C ≤ T <sub>J</sub> ≤ 125°C                                        |       |       | 100 | μΑ |

electrical characteristics over recommended operating junction temperature range,  $V_{I(IN)}$  = 5.5 V,  $I_O$  = rated current,  $\overline{EN}$  = 0 V,  $T_J$  = 25°C (unless otherwise noted)

#### power switch

| PARAMETER              | TEST CONDITIONS†                                        | TPS2010Y, TPS2011Y<br>TPS2012Y, TPS2013Y | UNIT |

|------------------------|---------------------------------------------------------|------------------------------------------|------|

|                        |                                                         | MIN TYP MAX                              |      |

| On-state resistance    | $V_{I(IN)} = 5.5 V,$                                    | 75                                       |      |

|                        | $V_{I(IN)} = 4.5 V,$                                    | 80                                       | 0    |

|                        | $V_{I(IN)} = 3 V$                                       | 120                                      | mΩ   |

|                        | $V_{I(IN)} = 2.7 V,$                                    | 140                                      |      |

| Output leakage current | $\overline{EN} = V_{I(IN)}$                             | 0.001                                    | μΑ   |

| Output rice time       | $V_{I(IN)} = 5.5 \text{ V}, \qquad C_L = 1 \mu\text{F}$ | 4                                        | ma   |

| Output rise time       | $V_{I(IN)} = 2.7 \text{ V}, \qquad C_L = 1 \mu F$       | 3.8                                      | ms   |

| Output fall time       | $V_{I(IN)} = 5.5 \text{ V}, \qquad C_L = 1 \mu F$       | 3.9                                      |      |

| Output fall time       | $V_{I(IN)} = 2.7 \text{ V}, \qquad C_{L} = 1 \mu F$     | 3.5                                      | ms   |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

#### current limit

| PARAMETER             | TEST CONDITIONS†                                                                          | TPS201<br>TPS201 | UNIT |     |   |

|-----------------------|-------------------------------------------------------------------------------------------|------------------|------|-----|---|

|                       |                                                                                           | MIN              | TYP  | MAX |   |

| Short-circuit current | V <sub>I(IN)</sub> = 5.5 V,<br>OUT connected to GND,<br>Device enabled into short circuit |                  | 0.4  |     | А |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

#### supply current

| PARAMETER                         | TEST CONDITIONS             | TPS2010<br>TPS2012 | UNIT  |     |    |

|-----------------------------------|-----------------------------|--------------------|-------|-----|----|

|                                   |                             | MIN                | TYP   | MAX |    |

| Supply current, low-level output  | $\overline{EN} = V_{I(IN)}$ | (                  | 0.015 |     | μΑ |

| Supply current, high-level output | EN = 0 V                    | _                  | 73    |     | μΑ |

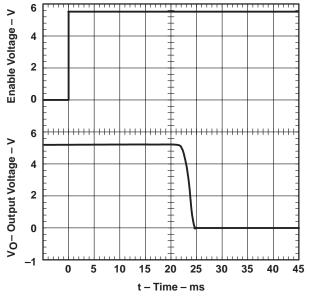

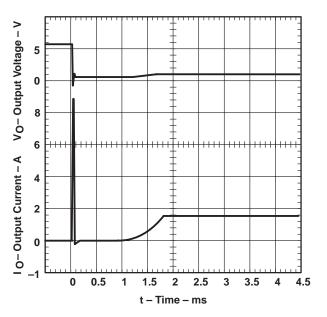

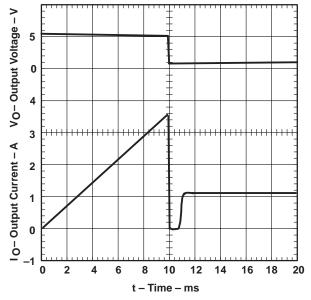

Figure 1. Propagation Delay and Rise Time With 1- $\mu$ F Load,  $V_{I(IN)}$  = 5.5 V

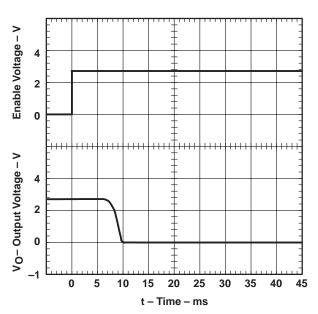

Figure 3. Propagation Delay and Rise Time With 1- $\mu$ F Load,  $V_{I(IN)}$  = 2.7 V

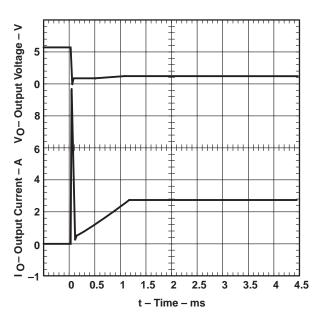

Figure 2. Propagation Delay and Fall Time With 1- $\mu$ F Load, V<sub>I(IN)</sub> = 5.5 V

Figure 4. Propagation Delay and Fall Time With 1- $\mu$ F Load,  $V_{I(IN)}$  = 2.7 V

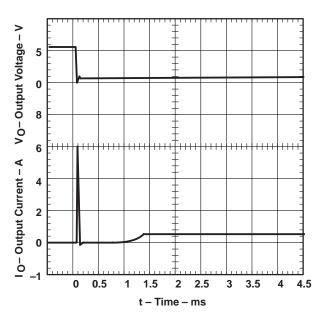

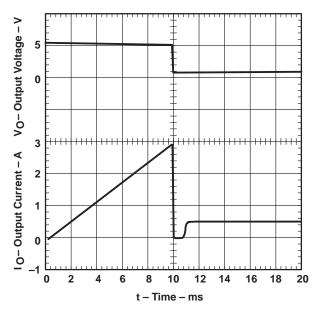

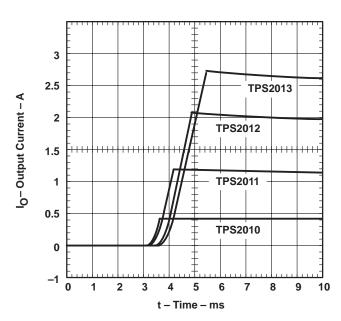

Figure 5. TPS2010, Short-Circuit Current. Short is Applied to Enabled Device,  $V_{I(IN)} = 5.5 \text{ V}$

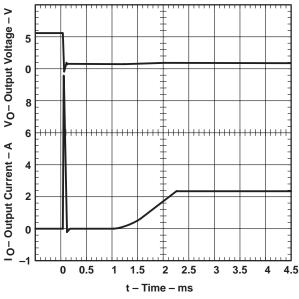

Figure 7. TPS2012, Short-Circuit Current. Short is Applied to Enabled Device,  $V_{I(IN)} = 5.5 \text{ V}$

Figure 6. TPS2011, Short-Circuit Current. Short is Applied to Enabled Device,  $V_{I(IN)} = 5.5 \text{ V}$

Figure 8. TPS2013 – Short-Circuit Current. Short is Applied to Enabled Device,  $V_{I(IN)} = 5.5 \text{ V}$

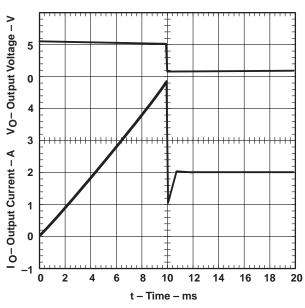

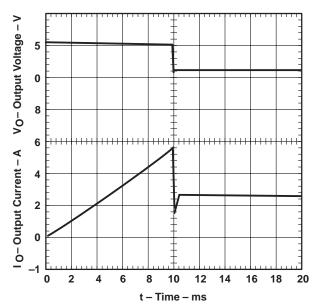

Figure 9. TPS2010 – Threshold Current,  $V_{I(IN)} = 5.5 \text{ V}$

Figure 11. TPS2012 – Threshold Current,  $V_{I(IN)} = 5.5 \text{ V}$

Figure 10. TPS2011 – Threshold Current,  $V_{I(IN)}$  = 5.5 V

Figure 12. TPS2013 – Threshold Current,  $V_{I(IN)}$  = 5.5 V

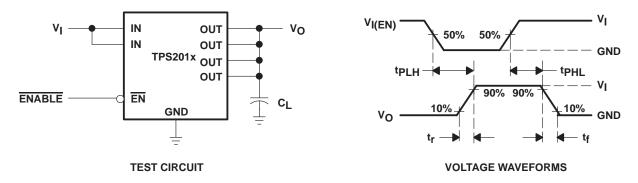

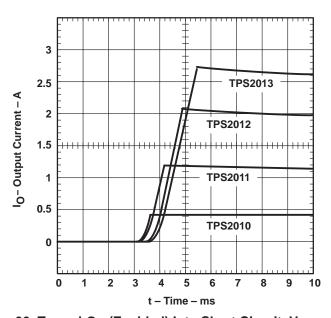

Figure 13. Turned-On (Enabled) Into Short Circuit,  $V_{I(IN)} = 5.5 \text{ V}$

Figure 14. Test Circuit and Voltage Waveforms

1.5

0

0.3

0.9

I<sub>O</sub> – Output Current – A Figure 17 0.3

0.9

IO - Output Current - A

Figure 18

1.2

1.5

0

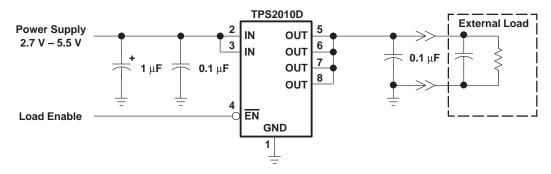

# **APPLICATION INFORMATION**

Figure 29. Typical Application

# power supply considerations

The TPS201x family has multiple inputs and outputs, which must be connected in parallel to minimize voltage drop and prevent unnecessary power dissipation.

A 0.047- $\mu F$  to 0.1- $\mu F$  ceramic bypass capacitor between IN and GND, close to the device, is recommended. A high-value electrolytic capacitor is also desirable when the output load is heavy or has large paralleled capacitors. Bypassing the output with a 0.1- $\mu F$  ceramic capacitor improves the immunity of the device to electrostatic discharge (ESD).

#### APPLICATION INFORMATION

#### overcurrent

A sense FET is employed to check for overcurrent conditions. Unlike sense resistors and polyfuses, sense FETs do not increase series resistance to the current path. When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Shutdown only occurs if the fault is present long enough to activate thermal limiting.

Three possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before  $V_{I(IN)}$  has been applied (see Figure 30). The TPS201x senses the short and immediately switches into a constant-current output.

Under the second condition, the short occurs while the device is enabled. At the instant the short occurs, very high currents flow for a short time before the current-limit circuit can react (see Figures 5, 6, 7, and 8). After the current-limit circuit has tripped, the device limits normally.

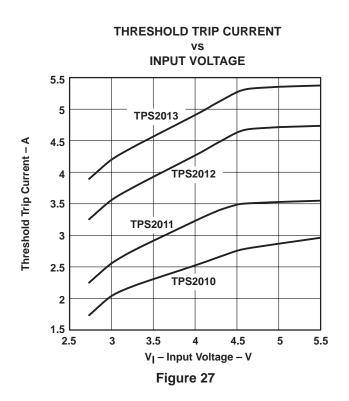

Under the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached (see Figures 9, 10, 11, and 12). The TPS201x family is capable of delivering currents up to the current-limit threshold without damage. Once the threshold has been reached, the device switches into its constant-current mode.

Figure 30. Turned-On (Enabled) Into Short Circuit,  $V_{I(IN)} = 5.5 \text{ V}$

#### APPLICATION INFORMATION

#### power dissipation and junction temperature

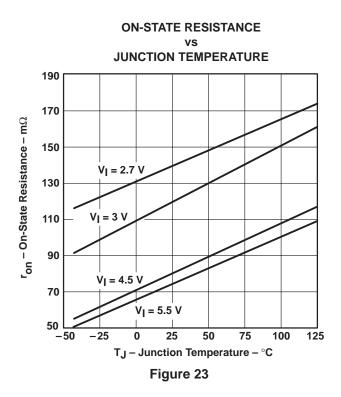

The low on resistance of the N-channel MOSFET allows small surface-mount packages, such as SOIC or TSSOP to pass large currents. The thermal resistances of these packages are high compared to that of power packages; it is good design practice to check power dissipation and junction temperature. The first step is to find  $r_{on}$  at the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{on}$  from Figure 23. Next calculate the power dissipation using:

$$P_D = r_{on} \times I^2$$

Finally, calculate the junction temperature:

$$T_J = P_D \times R_{\theta JA} + T_A$$

Where:

$T_A$  = Ambient temperature

$R_{\theta,IA}$  = Thermal resistance SOIC = 172°C/W, TSSOP = 179°C/W

Compare the calculated junction temperature with the initial estimate. If they do not agree within a few degrees, repeat the calculation using the calculated value as the new estimate. Two or three iterations are generally sufficient to get a reasonable answer.

#### thermal protection

Thermal protection is provided to prevent damage to the IC when heavy-overload or short-circuit faults are present for extended periods of time. The faults force the TPS201x into its constant current mode, which causes the voltage across the high-side switch to increase; under short-circuit conditions, the voltage across the switch is equal to the input voltage. The increased dissipation causes the junction temperature to rise to dangerously high levels. The protection circuit senses the junction temperature of the switch and shuts it off. The switch remains off until the junction has dropped approximately 20°C. The switch continues to cycle in this manner until the load fault or input power is removed.

#### **ESD** protection

All TPS201x terminals incorporate ESD-protection circuitry designed to withstand a 6-kV human-body-model discharge as defined in MIL-STD-883C. Additionally, the output is protected from discharges up to 12 kV.

28-Aug-2010

# **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPS2010D         | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2010DG4       | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2010DR        | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2010DRG4      | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2010PWLE      | OBSOLETE   | TSSOP        | PW                 | 14   |             | TBD                        | Call TI              | Call TI                      | Replaced by TPS2010PWR      |

| TPS2010PWR       | ACTIVE     | TSSOP        | PW                 | 14   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2010PWRG4     | ACTIVE     | TSSOP        | PW                 | 14   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2011D         | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2011DG4       | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2011DR        | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2011DRG4      | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2011PWLE      | OBSOLETE   | TSSOP        | PW                 | 14   |             | TBD                        | Call TI              | Call TI                      |                             |

| TPS2012D         | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2012DG4       | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2012DR        | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2012DRG4      | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2012PWLE      | OBSOLETE   | TSSOP        | PW                 | 14   |             | TBD                        | Call TI              | Call TI                      |                             |

| TPS2013D         | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

# PACKAGE OPTION ADDENDUM

28-Aug-2010

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPS2013DG4       | ACTIVE     | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2013DR        | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2013DRG4      | ACTIVE     | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Purchase Samples            |

| TPS2013PWLE      | OBSOLETE   | TSSOP        | PW                 | 14   |             | TBD                        | Call TI              | Call TI                      |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Jul-2012

# TAPE AND REEL INFORMATION

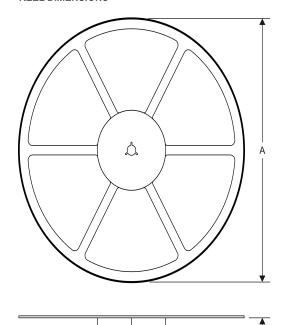

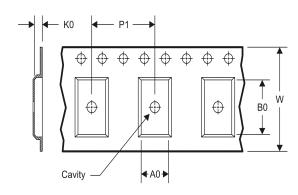

#### **REEL DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### TAPE AND REEL INFORMATION

#### \*All dimensions are nominal

| Device     |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2010DR  | SOIC  | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2010PWR | TSSOP | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS2011DR  | SOIC  | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2012DR  | SOIC  | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2013DR  | SOIC  | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 14-Jul-2012

\*All dimensions are nominal

| 7 til diffictiolofio are florifital |              |                 |      |      |             |            |             |

|-------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS2010DR                           | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2010PWR                          | TSSOP        | PW              | 14   | 2000 | 367.0       | 367.0      | 35.0        |

| TPS2011DR                           | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2012DR                           | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2013DR                           | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| roducts |                     | Applications  |

|---------|---------------------|---------------|

| udia    | ununu ti com/ou dio | Automotive on |

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio www.ti.com/communications **Amplifiers** amplifier.ti.com Communications and Telecom **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** Consumer Electronics www.ti.com/consumer-apps www.dlp.com DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

OMAP Mobile Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

www.ti-rfid.com

Pr

# **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

# http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

# Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9