# Fixed-Frequency Flyback Controller with Ultra-Low, No-Load Power Consumption

## DESCRIPTION

The HFC0511 is a fixed-frequency, currentcontroller with internal mode compensation specifically designed for medium-power, offline, flyback, switch-mode power supplies. The HFC0511 is a highly efficient green-mode controller. At light loads. the controller freezes the peak current and reduces its switching frequency down to 27kHz to achieve excellent light-load efficiency. At very light loads, the controller enters burst mode to achieve very low standby power consumption.

The HFC0511 offers frequency jittering to help dissipate energy generated by the conducted noise.

The HFC0511 employs an over-power compensation function to narrow the difference of the over-power protection point between the low line and high line.

The HFC0511 also has an X-cap discharge function to discharge the X-capacitor when the input is unplugged. This helps lower the power at no load.

Full protection features include thermal shutdown, VCC under-voltage lockout (UVLO), overload protection (OLP), over-voltage protection (OVP), and brown-out protection.

The HFC0511 is available in a SOIC8-7A package.

## **FEATURES**

- Fixed-Frequency, Current-Mode Control with Internal Slope Compensation

- Frequency Foldback down to 27kHz at Light Load

- Burst Mode for Low Standby Power Consumption, Meeting EuP Lot 6

- Frequency Jitter to Reduce EMI Signature

- X-Cap Discharge Function

- Adjustable Over-Power Compensation

- Internal High-Voltage Current Source

- VCC Under-Voltage Lockout (UVLO) with Hysteresis

- Brown-Out Protection on HV

- Overload Protection with Programmable Delay

- Thermal Shutdown (Auto-Restart with Hysteresis)

- Latch-Off for External Over-Voltage Protection (OVP) and Over-Temperature Protection (OTP) on TIMER

- Latch-Off for VCC Over-Voltage Protection (OVP)

- Short-Circuit Protection (SCP)

- Programmable Soft Start (SS)

- Available in a SOIC8-7A Package

### **APPLICATIONS**

- AC/DC Power for Small and Large Appliances

- AC/DC Adapters for Notebook Computers, Tablets, and Smart Phones

- Offline Battery Chargers

- LCD TVs and Monitors

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

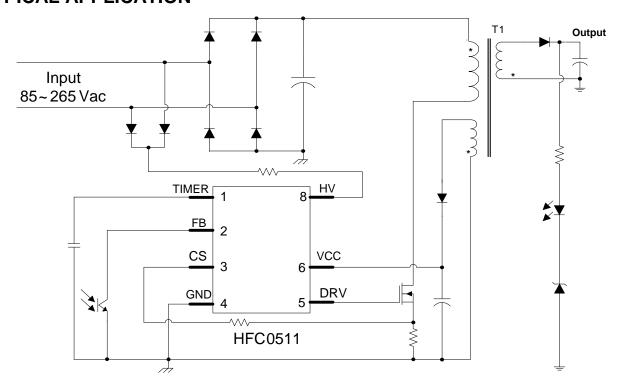

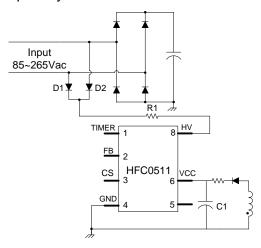

# **TYPICAL APPLICATION**

# **ORDERING INFORMATION**

| Part Number* | Package  | Top Marking |

|--------------|----------|-------------|

| HFC0511GS    | SOIC8-7A | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. HFC0511GS-Z)

# **TOP MARKING**

HFC0511 LLLLLLL MPSYWW

HFC0511: First seven digits of the part number

LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

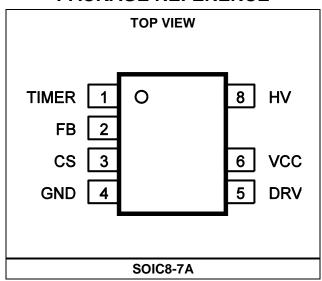

# PACKAGE REFERENCE

| <b>ABSOLUTE MAXIMUM RATINO</b>                      | 3S <sup>(1)</sup> |

|-----------------------------------------------------|-------------------|

| HV0.7V to                                           | 5 700V            |

| VCC, DRV to GND0.3V                                 | to 30V            |

| FB, TIMER, CS to GND0.3\                            | / to 7V           |

| Continuous power dissipation ( $T_A = +25^{\circ}C$ |                   |

|                                                     | 1.3W              |

| Junction temperature                                | 150°C             |

| Lead temperature                                    | 260°C             |

| Storage temperature60°C to +                        | -150°C            |

| ESD capability human body model (exce               |                   |

| and DRV)                                            | .4.0kV            |

| ESD capability human body model (DRV)               |                   |

|                                                     | .3.5kV            |

| ESD capability human body model (HV)                |                   |

| ESD capability for machine mode                     | 400V              |

| Recommended Operation Condition                     | 1s <sup>(3)</sup> |

| Operating junction temp. (T <sub>J</sub> )40°C to + | -125°C            |

| Operating VCC range                                 |                   |

| Thermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |       |

|-----------------------------------|-------------------------|--------------------------|-------|

| SOIC8-7A                          | 96                      | 45                       | .°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERICS**

VCC = 18V,  $T_J$  = -40°C ~ 125°C, min and max values are guaranteed by characterization, typical value is tested under 25°C, unless otherwise specified.

| Parameter                                                                        | Symbol                                    | Conditions                                                                | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------|------|------|------|------|

| Start-Up Current Source (HV)                                                     |                                           |                                                                           |      |      |      |      |

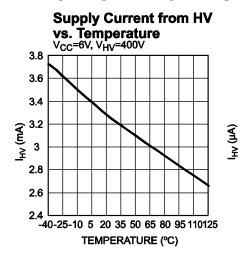

| Cupply ourrent from LIV                                                          | I <sub>HV_400</sub>                       | VCC = 12V, V <sub>HV</sub> = 400V                                         | 1.5  | 2.8  | 3.9  | A    |

| Supply current from HV                                                           | I <sub>HV_120</sub>                       | VCC = 12V, V <sub>HV</sub> = 120V                                         | 1.5  | 2.7  | 3.7  | mA   |

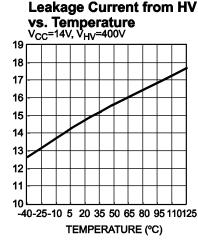

| Leakage current from HV                                                          | I <sub>LK_400</sub>                       | VCC increases to 18V,<br>then decreases to 14V,<br>V <sub>HV</sub> = 400V | 1    | 16   | 28   | μΑ   |

| Loakage current from 11v                                                         | I <sub>LK_200</sub>                       | VCC increases to 18V,<br>then decreases to 14V,<br>V <sub>HV</sub> = 200V | 1    | 13   | 25   | μΑ   |

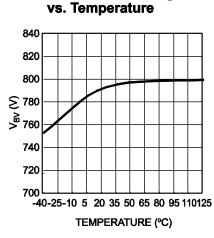

| Break-down voltage                                                               | $V_{BR}$                                  | T <sub>J</sub> = 25°C                                                     | 700  | 790  |      | V    |

| Supply Voltage Management (VCC                                                   | ;)                                        | 1                                                                         | -    |      | I.   |      |

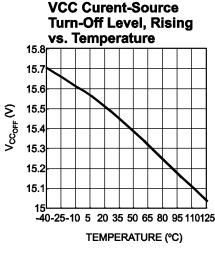

| VCC increasing level at which the current source turns off                       | VCC <sub>OFF</sub>                        |                                                                           | 12.5 | 15.5 | 18   | V    |

| VCC decreasing level above which soft start takes place if HV > HV <sub>ON</sub> | VCCss                                     |                                                                           | 10.5 | 12   | 13   | V    |

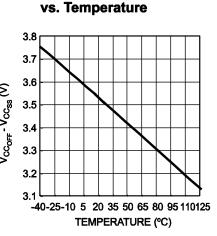

| VCC hysteresis for brown-in detection                                            | VCC <sub>OFF</sub> -<br>VCC <sub>SS</sub> |                                                                           | 1.35 | 3.5  |      | V    |

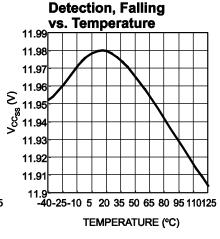

| VCC decreasing level at which the current source turns on                        | VCCon                                     |                                                                           | 7.3  | 8.5  | 9.6  | V    |

| VCC UVLO hysteresis                                                              | VCC <sub>OFF</sub> -<br>VCC <sub>ON</sub> |                                                                           | 5    | 7    |      | V    |

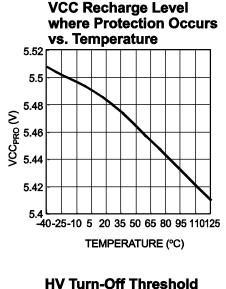

| VCC recharge level when protection takes place                                   | VCC <sub>PRO</sub>                        |                                                                           | 4.9  | 5.5  | 6.2  | V    |

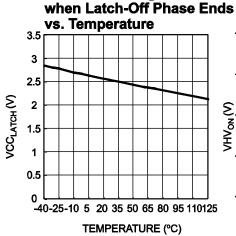

| VCC decreasing level at which the latch-off phase ends                           | VCCLATCH                                  |                                                                           |      | 2.5  |      | V    |

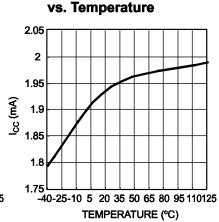

| Internal IC consumption                                                          | Icc                                       | $V_{FB} = 2V$ , $C_L = 1nF$ , $VCC = 12V$                                 | 0.9  | 1.8  | 2.7  | mA   |

| Internal IC consumption, latch-off phase                                         | Іссьатсн                                  | $VCC = VCC_{OFF} - 1V,$ $T_{J} = 25^{\circ}C$                             | 520  | 700  | 880  | μΑ   |

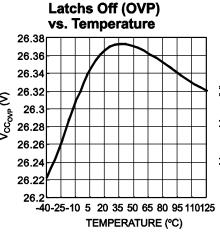

| Voltage on the VCC above which the controller latches off (OVP)                  | Vovp                                      |                                                                           | 24   | 26.5 | 28.5 | V    |

| Blanking duration on the OVP comparator                                          | $T_{\text{OVP}}$                          |                                                                           |      | 60   |      | μs   |

| Brown-Out                                                                        |                                           |                                                                           |      |      |      |      |

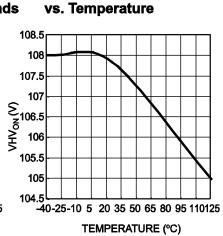

| HV turn-on threshold voltage                                                     | HVon                                      | V <sub>HV</sub> going up, T <sub>J</sub> = 25°C                           | 95   | 107  | 119  | V    |

| HV turn-off threshold voltage                                                    | HV <sub>OFF</sub>                         | V <sub>HV</sub> going down,<br>T <sub>J</sub> = 25°C                      | 86   | 97   | 110  | V    |

| Brown-out hysteresis                                                             | ΔHV                                       | T <sub>J</sub> = 25°C                                                     | 6.5  | 10   | 13.5 | V    |

| Timer duration for line cycle dropout                                            | T <sub>HV</sub>                           | C <sub>TIMER</sub> = 47nF                                                 | 40   |      |      | ms   |

| Oscillator                                                                       |                                           |                                                                           |      |      |      |      |

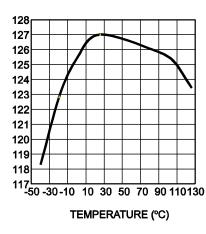

| Oscillator frequency                                                             | fosc                                      | V <sub>FB</sub> > 1.85V, T <sub>J</sub> = 25°C                            | 125  | 130  | 135  | kHz  |

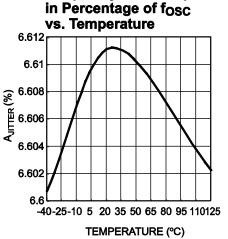

| Frequency jittering amplitude, in percentage of fosc                             | Ajitter                                   | V <sub>FB</sub> > 1.85V, T <sub>J</sub> = 25°C                            | ±5   | ±6.5 | ±8.3 | %    |

| Frequency jittering entry level                                                  | V <sub>FB_JITTER</sub>                    |                                                                           |      |      | 1.95 | V    |

| Frequency jittering modulation period                                            | T <sub>jitter</sub>                       | C <sub>TIMER</sub> = 47nF                                                 |      | 3.7  |      | ms   |

# **ELECTRICAL CHARACTERICS** (continued)

VCC = 18V,  $T_J$  = -40°C ~ 125°C, min and max values are guaranteed by characterization, typical value is tested under 25°C, unless otherwise specified.

| Parameter                                     | Symbol                  | Conditions                                               | Min  | Тур  | Max  | Unit         |

|-----------------------------------------------|-------------------------|----------------------------------------------------------|------|------|------|--------------|

| Current Sense                                 |                         |                                                          |      | •    | •    |              |

| Current-limit point                           | $V_{ILIM}$              |                                                          | 0.93 | 1    | 1.07 | V            |

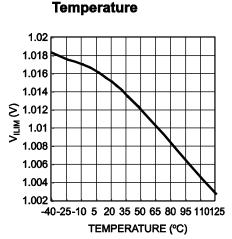

| Short-circuit protection point                | V <sub>SCP</sub>        |                                                          | 1.3  | 1.47 | 1.63 | V            |

| Current limitation when frequency             | V                       | V <sub>FB</sub> = 1.85V                                  | 0.63 | 0.60 | 0.72 | V            |

| folds back                                    | V <sub>FOLD</sub>       | VFB = 1.85 V                                             | 0.63 | 0.68 | 0.73 | V            |

| Current limitation when entering              | V <sub>IBURL</sub>      | V <sub>FB</sub> = 0.7V                                   |      | 0.11 |      | V            |

| burst                                         | V IBURL                 | VFB = 0.7 V                                              |      | 0.11 |      | V            |

| Current limitation when leaving               | Viburh                  | $V_{FB} = 0.8V$                                          |      | 0.15 |      | V            |

| burst                                         |                         | V1B = 0.0 V                                              |      |      |      | •            |

| Leading edge blanking for VILIM               | T <sub>LEB1</sub>       |                                                          |      | 350  |      | ns           |

| Leading edge blanking for V <sub>SCP</sub>    | T <sub>LEB2</sub>       |                                                          |      | 270  |      | ns           |

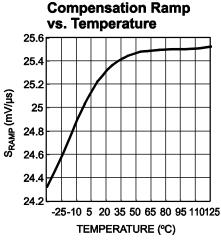

| Slope of the compensation ramp                | SRAMP                   |                                                          | 18   | 25   | 32   | mV/µs        |

| Feedback (FB)                                 |                         |                                                          |      |      |      |              |

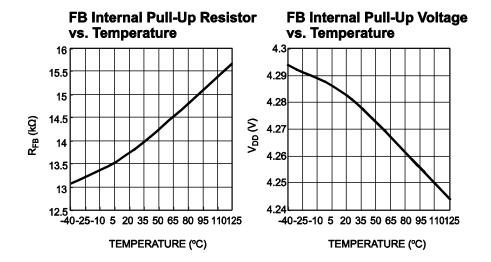

| Internal pull-up resistor                     | $R_FB$                  |                                                          | 11.5 | 14   | 17   | kΩ           |

| Internal pull-up voltage                      | $V_{DD}$                |                                                          |      | 4.3  |      | V            |

| V <sub>FB</sub> to internal current set point | $K_{FB1}$               | $V_{FB} = 2V$                                            | 2.55 | 2.8  | 3.05 |              |

| division ratio                                | IVERI                   | VFB - 2 V                                                | 2.00 | 2.0  | 0.00 |              |

| V <sub>FB</sub> to internal current set point | K <sub>FB2</sub>        | V <sub>FB</sub> = 3V                                     | 2.8  | 3.1  | 3.4  |              |

| division ratio                                | T G BZ                  | VIB 01                                                   |      | 0.1  | 0    |              |

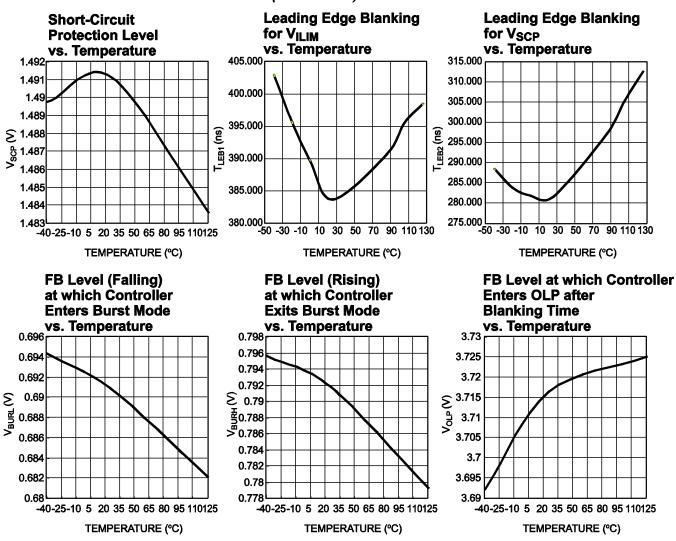

| FB decreasing level at which the              | V <sub>BURL</sub>       |                                                          | 0.63 | 0.7  | 0.77 | V            |

| controller enters burst mode                  | - 20.12                 |                                                          |      |      | -    |              |

| FB increasing level at which the              | $V_{BURH}$              |                                                          | 0.72 | 0.8  | 0.88 | V            |

| controller leaves burst mode                  |                         |                                                          |      |      |      |              |

| Overload Protection (OLP)                     |                         |                                                          | ı    | 1    | 1    |              |

| FB level at which the controller              | V <sub>OLP</sub>        |                                                          |      |      |      | .,           |

| enters the OLP after a dedicated              |                         |                                                          |      | 3.7  |      | V            |

| time                                          |                         |                                                          |      |      |      | <del> </del> |

| Time duration before OLP when                 | $T_OLP$                 | C <sub>TIMER</sub> = 47nF                                | 40   |      |      | ms           |

| FB reaches protection point                   |                         |                                                          |      |      |      |              |

| Over-Power Compensation                       | 17                      | T                                                        | ı    | 0.45 | 1    | A 0.7        |

| V <sub>HV</sub> to I <sub>OPC</sub> ratio     | Kopc                    | 1001/11/                                                 |      | 0.45 |      | μA/V         |

|                                               |                         | $V_{HV} = 120V, V_{FB} = 2.5V$                           |      | 0    |      | μA           |

| Current out of CS                             |                         | $V_{HV} = 155V, V_{FB} = 2.5V$                           |      | 13   |      |              |

| Current out of CS                             | lopc                    | $V_{HV} = 310V, V_{FB} = 2.5V$                           |      | 85   |      |              |

|                                               |                         | $V_{HV} = 380V, V_{FB} = 2.5V,$<br>$T_{J} = 25^{\circ}C$ | 80   | 109  | 138  |              |

| FB voltage below which                        |                         | 1J = 20 G                                                |      | -    | -    |              |

| compensation is removed                       | V <sub>OPC(OFF)</sub>   |                                                          | 0.55 |      | 1    | V            |

| FB voltage above which                        |                         |                                                          |      | 1    |      |              |

| compensation is applied fully                 | V <sub>OPC(ON)</sub>    |                                                          |      |      | 2.2  | V            |

| Frequency Foldback                            |                         |                                                          | 1    | 1    | 1    | I.           |

| FB voltage threshold below which              |                         |                                                          |      |      |      |              |

| frequency foldback starts                     | $V_{FB(FOLD)}$          |                                                          |      | 1.8  | 1    | V            |

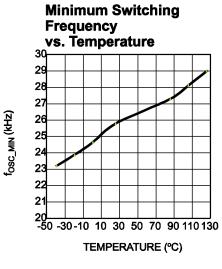

| Minimum switching frequency                   | Fosc(min)               | T <sub>J</sub> = 25°C                                    | 21   | 27   | 33   | kHz          |

| FB voltage threshold below which              | ì                       | 1.0 20 0                                                 |      |      | 55   |              |

| frequency foldback ends                       | V <sub>FB</sub> (FOLDE) |                                                          |      | 1.0  | 1    | V            |

| ,                                             |                         | 1                                                        |      | 1    | 1    | 1            |

# **ELECTRICAL CHARACTERICS** (continued)

VCC = 18V,  $T_J$  = -40°C ~ 125°C, min and max values are guaranteed by characterization, typical value is tested under 25°C, unless otherwise specified.

| Parameter                                   | Symbol                    | Conditions                      | Min | Тур  | Max | Unit |

|---------------------------------------------|---------------------------|---------------------------------|-----|------|-----|------|

| Latch-Off Input (Integration in TIMER)      |                           |                                 |     |      |     |      |

| Threshold below which controller is latched | V <sub>TIMER(LATCH)</sub> |                                 | 0.7 | 1    | 1.3 | V    |

| Blanking duration on latch detection        | TLATCH                    |                                 |     | 12   |     | μs   |

| DRV Voltage                                 |                           |                                 |     |      |     |      |

| Driver voltage high level                   | V <sub>High</sub>         | C <sub>L</sub> = 1nF, VCC = 12V |     | 10.3 |     | V    |

| Driver voltage clamp level                  | VClamp                    | C <sub>L</sub> = 1nF, VCC = 24V |     | 13.4 |     | V    |

| Driver voltage low level                    | $V_{Low}$                 | $C_L = 1nF, VCC = 24V$          |     | 16   |     | mV   |

| Driver voltage rise time                    | T <sub>R</sub>            | $C_L = 1nF$ , $VCC = 16V$       |     | 13   |     | ns   |

| Driver voltage fall time                    | $T_F$                     | $C_L = 1nF$ , $VCC = 16V$       |     | 23   |     | ns   |

| Driver pull-up resistance                   | R <sub>Pull-up</sub>      | $C_L = 1nF, VCC = 16V$          |     | 8    |     | Ω    |

| Driver pull-down resistance                 | R <sub>Pull-down</sub>    | $C_L = 1nF, VCC = 16V$          |     | 10   |     | Ω    |

| Thermal Shutdown                            |                           |                                 |     |      |     |      |

| Thermal shutdown threshold (5)              |                           |                                 |     | 150  |     | °C   |

| Thermal shutdown hysteresis (5)             |                           |                                 |     | 25   |     | °C   |

#### NOTE:

<sup>5)</sup> This parameter is guaranteed by design.

# **PIN FUNCTIONS**

| Pin# | Name  | Description                                                                                                                                                                                                        |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | TIMER | <b>Timer.</b> TIMER combines soft start, frequency jittering, and timer functions for overload protection (OLP), brown-out protection, and X-cap discharging. The HFC0511 can be latched off by pulling TIMER low. |

| 2    | FB    | Feedback. Use a pull-down optocoupler to control the output regulation.                                                                                                                                            |

| 3    | CS    | <b>Current sense.</b> CS senses the primary-side current for current-mode operation and provides a mean for over-power compensation adjustment.                                                                    |

| 4    | GND   | IC ground.                                                                                                                                                                                                         |

| 5    | DRV   | Drive signal output.                                                                                                                                                                                               |

| 6    | VCC   | Power supply.                                                                                                                                                                                                      |

| 8    | HV    | High-voltage current source. HV includes brown-out and X-cap discharge functions.                                                                                                                                  |

# TYPICAL CHARACTERISTICS

**Internal IC Consumption**

**VCC Current Source Turn-On**

**Break-Down Voltage**

Voltage above VCC

where the Controller

**VCC Hysteresis**

for HV Turn-On Detection

VCC Threshold for HV Turn-On

8.45 8.45 8.35 8.25 8.25 8.25 8.25 8.20 8.25 8.20 1.0125 TEMPERATURE (°C)

Level, Falling

vs. Temperature

# TYPICAL CHARACTERISTICS (continued)

VCC Decreasing Level

**HV Turn-On Threshold**

98 97.5 96.5 96.5 95.5 94.5 -40-25-10 5 20 35 50 65 80 95 110125 TEMPERATURE (°C)

vs. Temperature

**Oscillator Frequency**

vs. Temperature

**Frequency Jitter Amplitude**

Slope of the

**Current Limit vs.**

# TYPICAL CHARACTERISTICS (continued)

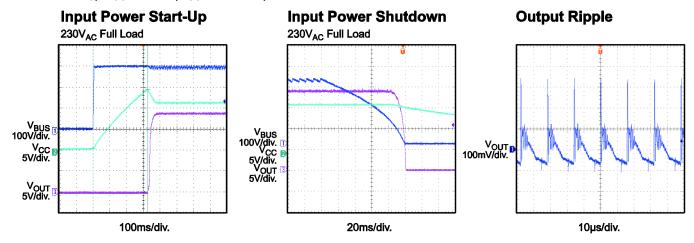

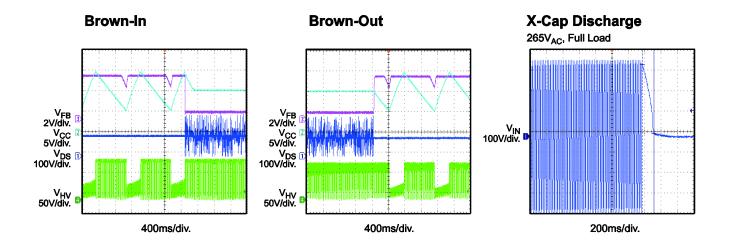

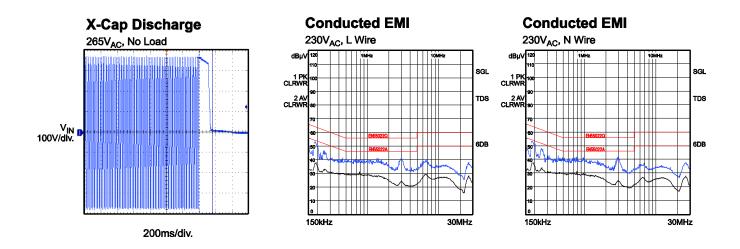

# TYPICAL PERFORMANCE CHARACTERISICS

$V_{IN} = 230V_{AC}$ ,  $V_{OUT} = 19V$ ,  $I_{OUT} = 2.35A$ , unless otherwise noted.

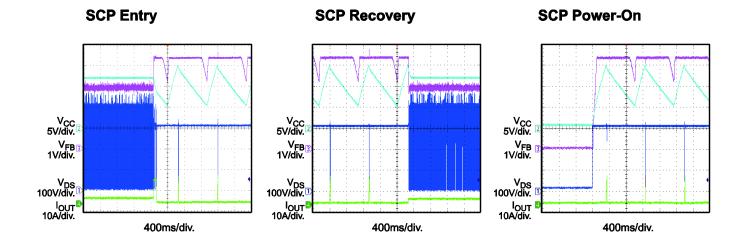

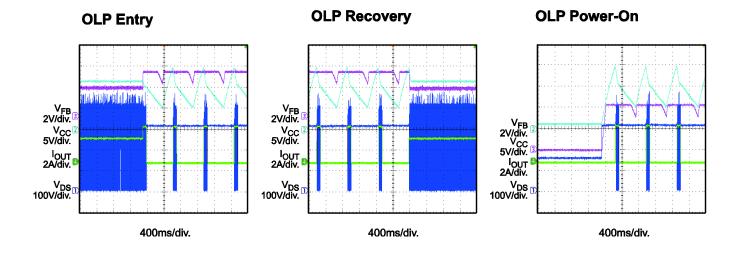

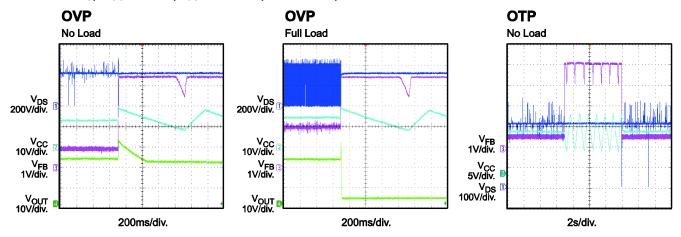

# **TYPICAL PERFORMANCE CHARACTERISICS** (continued)

$V_{IN} = 230V_{AC}$ ,  $V_{OUT} = 19V$ ,  $I_{OUT} = 2.35A$ ,  $T_A = 25$ °C, unless otherwise noted.

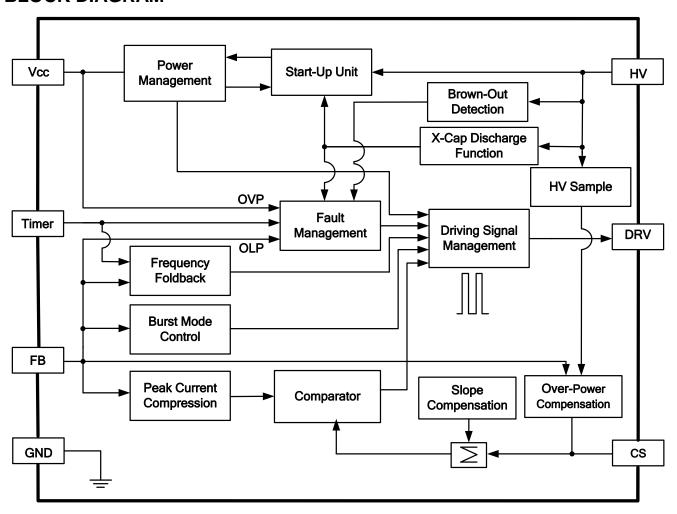

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

## **OPERATION**

The HFC0511 incorporates all necessary features for building a reliable switch-mode power supply. The HFC0511 is a fixedfrequency, current-mode controller with internal slope compensation. At light loads, controller freezes the peak current and reduces its switching frequency down to 27kHz to minimize switching losses. When the output power falls below a given level, the controller enters burst mode. The HFC0511 also has excellent EMI performance due to frequency jittering. The HFC0511's high level integration requires few external very components.

## **Fixed Frequency with Jitter**

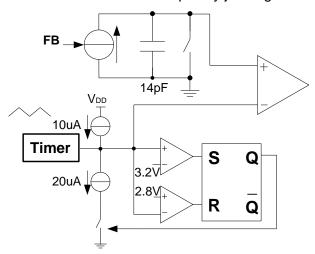

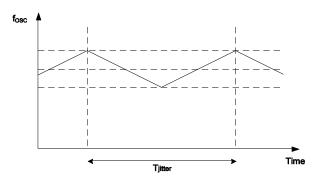

Frequency jitter reduces EMI by spreading the energy over the jitter frequency range. Figure 2 shows the circuit of the frequency jittering.

**Figure 2: Frequency Jitter Circuit**

A controlled current sourced (fixed at  $2.72\mu A$  when  $V_{FB}=2V$ ) charges the internal  $C_{OSC}$  capacitor. Comparing the capacitor voltage to the TIMER voltage determines the switching frequency. Frequency jitter is accomplished by varying  $V_{TIMER}$  between 3.2V and 2.8V (see Figure 3). Determine  $T_{jitter}$  with Equation (1):

$$T_{\text{jitter}} = 2 \cdot \frac{C_{\text{TIMER}} \cdot (3.2V - 2.8V)}{10\mu\text{A}} \tag{1}$$

Figure 3: Frequency Jitter

# Frequency Foldback

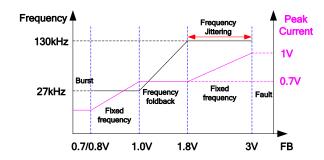

The HFC0511 implements frequency foldback at light load to improve overall efficiency.

When the load decreases to a given level (1.0V <  $V_{FB}$  < 1.8V), the controller freezes the peak current (as measured on CS, typically 0.7V) while reducing its switching frequency to 27kHz. This reduces switching loss. If the load continues to decrease, the peak current decreases with 27kHz of fixed frequency to avoid audible noise. Figure 4 shows the frequency vs.  $V_{FB}$  and peak current ( $V_{CS}$ ) vs.  $V_{FB}$ .

Figure 4: Frequency and Peak Current ( $V_{CS}$ ) vs.  $V_{FB}$

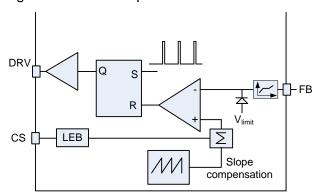

# **Current-Mode Operation with Slope Compensation**

The feedback voltage ( $V_{FB}$ ) controls the primary peak current. When the peak current reaches the level determined by  $V_{FB}$ , DRV turns off. The controller can also be used in continuous conduction mode (CCM) with a wide input voltage range because of its internal slope compensation (typically  $25 \text{mV/}\mu\text{s}$ ), avoiding sub-harmonic oscillations above a 50% duty cycle.

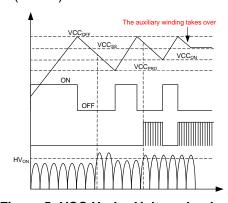

# High Voltage Start-Up Current Source with Brown-Out Detection

At start-up, the internal high-voltage current source from HV supplies the IC. The IC turns off the current source once VCC reaches VCC<sub>OFF</sub> (typically 15.5V) and detects the voltage on HV. Once the HV voltage exceeds HV<sub>ON</sub> before VCC drops down to VCC<sub>SS</sub> (typically 12V), the controller begins switching. If the HV voltage does not exceed VH<sub>ON</sub>, the system treats this as a brown-out and latches DRV low. When VCC drops to VCCPRO (typically 5.5V), the high-voltage current source turns on to recharge VCC. The auxiliary transformer winding supplies the IC after the controller starts switching. If VCC falls below VCC<sub>ON</sub> (typically 8.5V), the switching pulse stops, and the current source turns on again. Figure 5 shows the typical VCC under-voltage lockout (UVLO) waveform.

Figure 5: VCC Under-Voltage Lockout

The VCC lower threshold UVLO drops from  $VCC_{ON}$  to  $VCC_{PRO}$  under fault conditions such as overload protection (OLP), short-circuit protection (SCP), brown-out, and overtemperature protection (OTP).

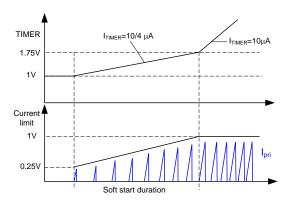

#### Soft Start (SS)

Soft start is externally programmable with a capacitor on TIMER. As this capacitor charges from 1V to 1.75V with 1/4 of the normal charge current, the peak-current limit threshold increases gradually from 0.25V to 1V while increasing the switching frequency gradually. Figure 6 shows the typical soft-start waveform. The TIMER capacitor determines the start-up duration as shown in Equation (2):

$$T_{Soft-start} = \frac{C_{TIMER} \cdot (1.75V - 1V)}{10/4\mu A}$$

(2)

Figure 6: Soft Start

#### **Burst Mode**

To minimize power dissipation in no load or light load, the HFC0511 employs burst-mode operation. As the load decreases,  $V_{FB}$  decreases. The IC enters burst mode when  $V_{FB}$  drops below the lower threshold ( $V_{BURL}$ , typically 0.7V), stopping output switching. Then the output voltage starts to drop, which causes  $V_{FB}$  to increase again. Once  $V_{FB}$  exceeds  $V_{BURH}$  (typically 0.8V), switching resumes. Burst mode enables and disables MOSFET switching alternately, thereby reducing no-load or lightload switching losses.

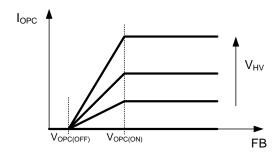

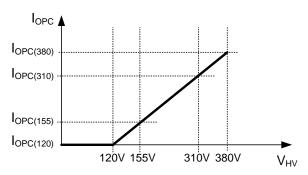

# **Adjustable Over-Power Compensation**

An offset current proportional to the input voltage is added to the current sense voltage. By choosing the value of the resistor to be in series with CS, the amount of compensation can be adjusted to the application for a more accurate output power limit at the total input range. Figure 7 and Figure 8 show the compensation current relation to FB and the peak voltage on HV respectively.

Figure 7: Compensation Current vs. FB and HV Voltage

Figure 8: Compensation Current vs. Peak of Rectified Input Line AC Voltage

## **Timer-Based Overload Protection (OLP)**

In a flyback converter, if the switching frequency is fixed, the maximum output power is limited by the peak current. The output voltage drops below the set value when the output power exceeds the power limit. This reduces the current through the optocoupler, pulling  $V_{\text{FB}}$  high.

When FB is higher than the OLP voltage ( $V_{\text{OLP}}$ ) (typically 3.7V), which is considered to be an error flag, the timer begins counting. If the error flag is removed during the count, the timer resets. If the timer count reaches 17, OLP is triggered. This timer duration avoids triggering OLP during power supply start-up or short load transients. Figure 9 shows the OLP function.

Figure 9: Overload Protection

#### **Timer-Based Brown-Out Protection**

The brown-out protection block is similar to the OLP block. When the HV voltage drops below  $HV_{OFF}$  (typically 97V), which is considered to be an error flag, the timer begins counting. Once the HV voltage is higher than  $HV_{OFF}$ , the timer resets. When the timer counts to 17, brown-out protection is triggered and switching stops.

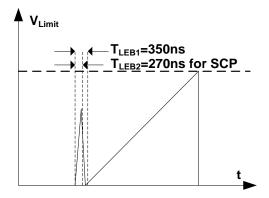

## **Short-Circuit Protection (SCP)**

The HFC0511 employs short-circuit protection (SCP) if  $V_{CS}$  reaches  $V_{SCP}$  (typically 1.47V) after a reduced leading-edge blanking time ( $T_{LEB2}$ ). Once the fault disappears, the power supply resumes operation.

#### **Thermal Shutdown**

To prevent thermal damage, the HFC0511 stops switching when the temperature exceeds 150°C. Once the temperature drops below 125°C, the power supply resumes operation. During thermal shutdown, the VCC UVLO lower threshold drops from 8.5V to 5.5V.

# **VCC Over-Voltage Protection (OVP)**

The HFC0511 enters a latched fault condition if VCC rises above  $V_{\text{OVP}}$  (typically 26.5V) for 60µs. The controller remains fully latched until VCC drops below VCC<sub>LATCH</sub> (typically 2.5V), such as when the power supply is unplugged from the main input and is plugged in again. This situation usually occurs when the optocoupler fails, which results in the loss of output voltage regulation.

## TIMER Latch-Off for OVP and OTP

Pulling TIMER below  $V_{\text{TIMER(LATCH)}}$  (typically 1V) for 12µs can latch off the IC. This function can be used for external over-voltage protection (OVP) and OTP.

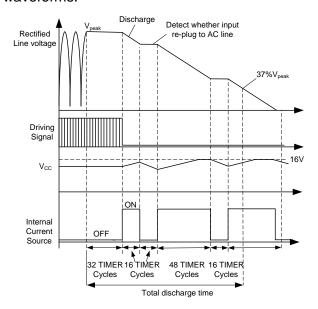

#### X-Cap Discharge Function

X-capacitors are typically positioned across a power supply's input terminals to filter differential mode EMI noise. These components pose a potential hazard since they can store unsafe levels of voltage energy after the AC line is disconnected. Generally, resistors in parallel with the X-caps provide a discharge path to meet safety standards, but these discharge resistors produce a constant loss while the AC is connected and contribute to no-load and standby input power consumption.

HV acts as a smart X-cap discharger. When AC voltage is applied, the internal high-voltage current source turns off to block HV current. and the IC monitors the HV voltage. When removing the AC voltage, the IC turns on the high-voltage current source after about 32 TIMER cycles to discharge the X-cap energy. The first discharge duration is 16 cycles. After the first discharge, the IC turns off the current source for 16 cycles to detect whether the input is plugged into the AC line again. If the AC input remains disconnected, the IC turns on the current source for 48 cycles to discharge again, and then turn off for 16 cycles to detect repeatedly until the voltage on the X-cap drops to VCC. Once the reconnected AC input is detected, the high-voltage current source remains off until VCC drops to VCC<sub>PRO</sub> (5.3V), and then restarts the system by recharging VCC. Figure 10 shows the discharge function waveforms.

Figure 10: X-Cap Discharger

This approach provides an intelligent discharge path for the X-cap, eliminating power loss from the external discharge resistors.

## **Clamped Driver**

DRV is clamped at  $V_{\text{Clamp}}$  (typically 13.4V) when VCC exceeds 16V, allowing for the use of any standard MOSFET.

## Leading-Edge Blanking

An internal leading-edge blanking (LEB) unit containing two LEB times is employed between the CS and the current comparator input to prevent premature switching pulse termination due to parasitic capacitances (see Figure 11). During the blanking time, the current comparator is disabled and cannot turn off the external MOSFET.

Figure 11: Leading-Edge Blanking

## **APPLICATION INFORMATION**

### **VCC Capacitor Selection**

Figure 12 shows the start-up circuit. The values of R1 and C1 determine the system start-up delay time. A larger R1 or C1 increases the start-up delay.

Figure 12: Start-Up Circuit

The VCC duration (from VCC<sub>OFF</sub> to VCC<sub>SS</sub>) for brown-out detection should exceed half of the input period. Estimate a value for the VCC capacitor with Equation (3):

$$C_{\text{VCC}} > \frac{I_{\text{CC(noswitch)}} \cdot 0.5 \cdot T_{\text{input}}}{\text{VCC}_{\text{OFF}} - \text{VCC}_{\text{SS}}}$$

(3)

Where  $I_{CC(noswitch)}$  is the internal consumption (close to  $I_{CClatch}$ ), and  $T_{input}$  is the period of the AC input. For most applications, choose a VCC capacitor value that exceeds  $10\mu F$ .

A higher R1 value decreases the current of the internal high-voltage current source, especially at a low-input condition. Ensure that the practical supply current from HV is not smaller than the corresponding internal IC consumption current, which is the same as  $I_{\text{CCLATCH}}$ . For the universal input range, R1 should be smaller than  $80k\Omega$ .  $20k\Omega$  is generally recommended.

#### Primary-Side Inductor Design (L<sub>m</sub>)

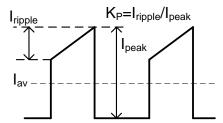

With internal slope compensation, the HFC0511 can support CCM when the duty cycle exceeds 50%. Set a ratio ( $K_P$ ) of the primary inductor's ripple current amplitude vs. the peak current value to 0 <  $K_P \le$  1, where  $K_P =$  1 for discontinuous conduction mode (DCM). Figure 13 shows the relevant waveforms.

A larger inductor leads to a smaller  $K_P$ , which can reduce RMS current, but increases transformer size. An optimal  $K_P$  value is between 0.6 and 0.8 for the universal input range and 0.8 to 1 for a 230V<sub>AC</sub> input range.

Figure 13: Typical Primary-Current Waveform

The input power (P<sub>in</sub>) at the minimum input can be estimated with Equation (4):

$$P_{in} = \frac{V_O \cdot I_O}{\eta} \tag{4}$$

Where  $V_0$  is the output voltage,  $I_0$  is the rated output current, and  $\eta$  is the estimated efficiency, which is generally between 0.75 and 0.85 depending on the input range and output application.

For CCM at minimum input, the converter duty cycle can be calculated with Equation (5):

$$D = \frac{(V_O + V_F) \cdot N}{(V_O + V_F) \cdot N + V_{\text{in(min)}}}$$

(5)

Where  $V_F$  is the secondary diode's forward voltage, N is the transformer turn ratio, and  $V_{\text{in}(\text{min})}$  is the minimum voltage on the bulk capacitor.

The MOSFET turn-on time can be calculated with Equation (6):

$$T_{on} = D \cdot T_{s} \tag{6}$$

Where  $T_s$  is the switching period.

The average value of the primary current is calculated with Equation (7):

$$I_{av} = \frac{P_{in}}{V_{in(min)}} \tag{7}$$

The peak value of the primary current is calculated with Equation (8):

$$I_{\text{peak}} = \frac{I_{\text{av}}}{\left(1 - \frac{K_{\text{p}}}{2}\right) \cdot D}$$

(8)

The ripple value of the primary current is calculated with Equation (9):

$$I_{ripple} = K_{P} \cdot I_{peak} \tag{9}$$

The valley value of the primary current is calculated with Equation (10):

$$I_{\text{valley}} = (1 - K_{\text{P}}) \cdot I_{\text{peak}} \tag{10}$$

L<sub>m</sub> can be estimated with Equation (11):

$$L_{m} = \frac{V_{\text{in(min)}} \cdot T_{\text{on}}}{I_{\text{ripples}}}$$

(11)

#### **Current-Sense Resistor**

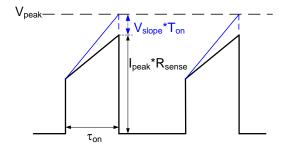

Figure 14 shows the peak-current comparator logic and the subsequent waveform.

**Peak-Current Comparator Circuit**

Typical Waveform Figure 14: Peak-Current Comparator

When the sum of the sensing resistor voltage and the slope compensator reaches  $V_{\text{peak}}$ , the comparator goes high to reset the RS flip-flop, and DRV is pulled down to turn off the MOSFET. The maximum current limit ( $V_{\text{limit}}$ , as measured by  $V_{\text{CS}}$ ) is 0.95V. The slope compensator ( $V_{\text{slope}}$ ) is ~25mV/µs. Given a certain margin, use 0.95x $V_{\text{limit}}$  as  $V_{\text{peak}}$  at full load. Then the voltage on the sensing resistor can be obtained with Equation (12):

$$V_{\text{sense}} = 95\% \cdot V_{\text{limit}} - V_{\text{slope}} \cdot T_{\text{on}}$$

(12)

Then calculate the value of the sense resistor with Equation (13):

$$R_{\text{sense}} = \frac{V_{\text{sense}}}{I_{\text{peak}}}$$

(13)

Select the current sense resistor with an appropriate power rating. Then calculate the sense resistor power loss with Equation (14):

$$P_{\text{sense}} = \left[ \left( \frac{I_{\text{peak}} + I_{\text{valley}}}{2} \right)^2 + \frac{1}{12} \left( I_{\text{peak}} - I_{\text{valley}} \right)^2 \right] \cdot D \cdot R_{\text{sense}} \quad \text{(14)}$$

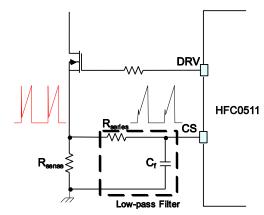

#### Low-Pass Filter on CS

A small capacitor connected to the CS with  $R_{\text{series}}$  forms a low-pass filter for noise filtering when the MOSFET turns on and off (see Figure 15).

Figure 15: Low-Pass Filter on CS

The low-pass filter's RxC constant should not exceed 1/3 of the leading-edge blanking period for SCP (T<sub>LEB2</sub>, typically 270ns), otherwise the filtered sensed voltage cannot reach the SCP point (1.45V) to trigger SCP if an output short circuit occurs.

## **Over-Power Compensation (OPC)**

The HFC0511 uses an over-power compensation function (OPC) by drawing current from CS. OPC minimizes the OLP difference caused by a different input voltage. The offset current is proportional to the input peak voltage sensed by HV.

Supposing that the resistor in the current sensing loop is  $R_{\text{series}}$ , and the input voltage is  $220V_{\text{AC}}$ , calculate the compensation voltage on CS with Equation (15):

$$V_{comp} = R_{series} \cdot I_{opc 310V}$$

(15)

The compensation criterion is making the FB voltage under full-load condition similar whether in high line or low line.

#### **Jitter Period**

Frequency jitter is an effective method to reduce EMI by dissipating energy. The n<sup>th</sup> order harmonic noise bandwidth is calculated with Equation (16):

$$B_{Tn} = n \cdot (2 \cdot \Delta f + f_{iitter})$$

(16)

Where  $\Delta f$  is the frequency jitter amplitude.

If B<sub>Tn</sub> exceeds the resolution bandwidth (RBW) of the spectrum analyzer (200Hz for noise frequency less than 150kHz, 9kHz for noise frequency between 150kHz to 30MHz), the spectrum analyzer receives less noise energy.

The capacitor on TIMER determines the period of the frequency jitter. A 10µA current source charges the capacitor. When the TIMER voltage reaches 3.2V, another 10µA current source discharges the capacitor to 2.8V. This charging and discharging cycle repeats.

Equation (2) describes the jitter period in theory. A smaller fitter is more effective for EMI reduction. However, the measurement bandwidth requires that fitter be large compared to the spectrum analyzer RBW for effective EMI reduction. fitter should also be less than the control-loop-gain crossover frequency to avoid disturbing the output voltage regulation. Simultaneously consider the practical application when selecting the TIMER capacitor. A capacitor that is too large may cause the start-up to fail at full load because of the long soft start-up duration shown in Equation (3).

However, a TIMER capacitor that is too small causes the TIMER period to become smaller, so the TIMER count capability is overloaded, and some logic problems may occur. For most applications, a f<sub>jitter</sub> value between 200Hz and 400Hz is recommended.

# X-Cap Discharge Time

Figure 10 shows the X-cap discharger waveforms. The maximum discharge time occurs at a high-line input with no-load condition. The maximum discharge delay time is calculated with Equation (17):

$$T_{delav} = 32 \cdot T_{iitter} \tag{17}$$

The X-cap is discharged from a high-voltage constant current source (I<sub>HV\_120V</sub>, typically 2.5mA) into HV. The current-source discharge time for the X-cap to drop to 37% of the peak voltage can be estimated with Equation (18):

$$T_{\text{discharge}} = \frac{C_{x} \cdot 63\% \cdot \sqrt{2} \cdot V_{\text{ac(max)}}}{I_{\text{HV}}}$$

(18)

Where  $C_X$  is the X-cap capacitance, and  $V_{AC(max)}$  is the maximum AC input RMS value.

The first discharging period is 16xT<sub>jitter</sub>, with a subsequent period equal to 48xT<sub>jitter</sub>. Then the discharge sections times can be calculated approximately with Equation (19):

$$n = \frac{T_{discharge} - 16 \cdot T_{jitter}}{48 \cdot T_{iitter}} + 1$$

(19)

For every discharge section, there is a certain period (16xT<sub>jitter</sub>) for detection as shown in Equation (20):

$$T_{\text{detect}} = 16 \cdot T_{\text{jitter}} \cdot (n-1)$$

(20)

As a result, the total discharge time is determined with Equation (21):

$$T_{\text{total}} = T_{\text{delay}} + T_{\text{discharge}} + T_{\text{detect}}$$

(21)

The total discharge time is relative to  $T_{jitter}$ , which is dependent on  $C_{TIMER}$ . For example, if  $C_{TIMER}$  is 47nF, and  $T_{jitter}$  is 3.7ms, the X-cap discharge margin is 1s due to the X-cap value tolerance ( $\pm 10\%$  typically). It is recommended to select an X-cap less than 3.3 $\mu$ F.

Though the X-cap has been discharged, it may still retain a high voltage on the bulk capacitor. For safety, make sure it is released before debugging the board.

## **Ramp Compensation**

When adopting peak current control, subharmonic oscillation occurs when D > 0.5 in CCM. The HFC0511 is equipped with internal ramp compensation to solve this problem.  $\alpha$  is calculated with Equation (22):

$$\alpha = \frac{\frac{D_{\text{max}} \cdot V_{\text{in(min)}}}{(1 - D_{\text{max}}) \cdot L_{\text{m}}} \cdot R_{\text{sense}} - m_{\text{a}}}{\frac{V_{\text{in(min)}}}{L_{\text{m}}} \cdot R_{\text{sense}} + m_{\text{a}}}$$

(22)

Where  $m_a=18 mV/\mu s$  is the minimum internal slope value of the compensation ramp,  $\frac{V_{in(min)}}{L_m} \cdot R_{sense} \ \, \text{is the slew rate of the primary-side} \\ \text{sensed} \ \, \text{by} \ \, \text{the CS} \ \, \text{resistor,} \quad \text{and} \\ \frac{D_{max} \cdot V_{in(min)}}{(1-D_{max}) \cdot L_m} \cdot R_{sense} \ \, \text{is the slew rate} \quad \text{of the} \\ \text{equivalent secondary-side voltage sensed by} \\ \text{the CS} \ \, \text{resistor respectively.} \quad \text{For stable}$

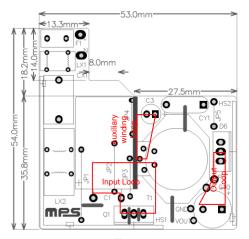

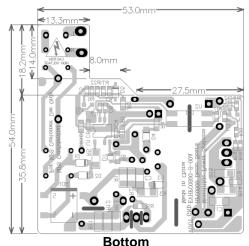

### **PCB Layout Guidelines**

operation, α must be less than 1.

Efficient PCB layout is critical for stable operation, good EMI performance, and good thermal performance. For best results, refer to Figure 16 and follow the guidelines below.

- 1) Minimize the power stage loop area including the input loop (C1 T1 Q1 R11/R12/R13 C1), the auxiliary winding loop (T1 D4 R4 C3 T1), and the output loop (T1 D6 C10 T1).

- Keep the input loop GND and control circuit separate.

Only connect them at C1.

- 3) Connect the Q1 heat sink to the primary GND plane to improve EMI.

- 4) Place the control circuit capacitors (such as those for FB, CS, and VCC) close to the IC to decouple noise.

Top

Figure 16: Recommended Layout

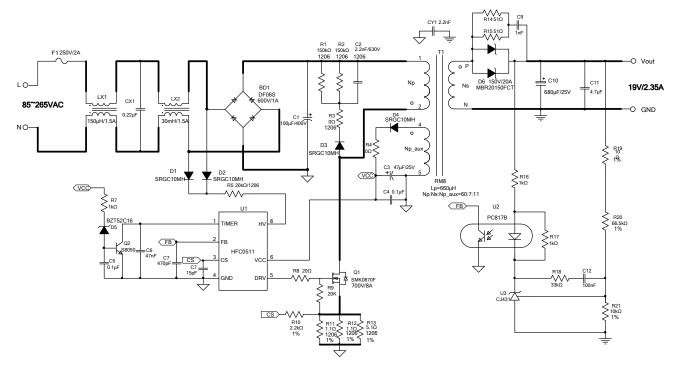

#### **Design Example**

Table 1 is a design example of the HFC0511 for power adapter applications.

**Table 1: Design Example**

| $V_{IN}$         | 85 to 265V <sub>AC</sub> |

|------------------|--------------------------|

| V <sub>OUT</sub> | 19V                      |

| Іонт             | 2 35A                    |

# **TYPICAL APPLICATION CIRCUIT**

Figure 17: Typical Application

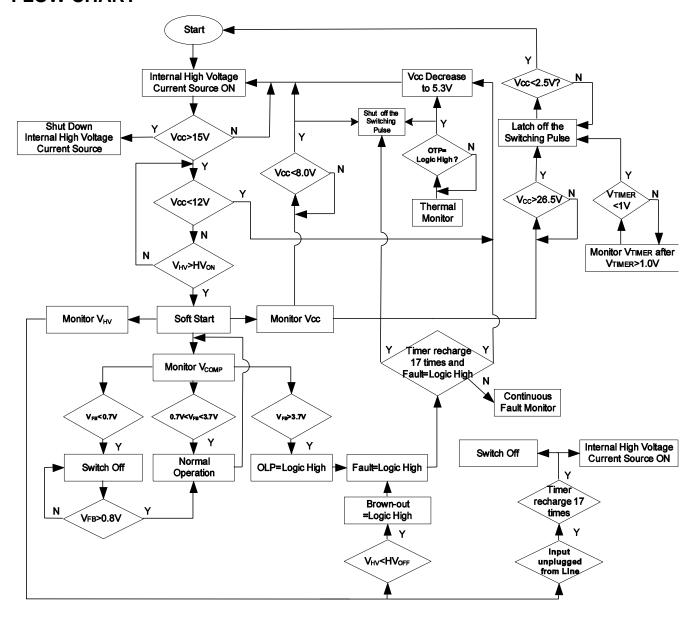

## **FLOW CHART**

UVLO, brown-out, OTP & OLP is auto restart, OVP on VCC and Latch-off on TIMER are latch mode

Release from the latch condition , need to unplug from the main input .

Figure 18: Control Flow Chart

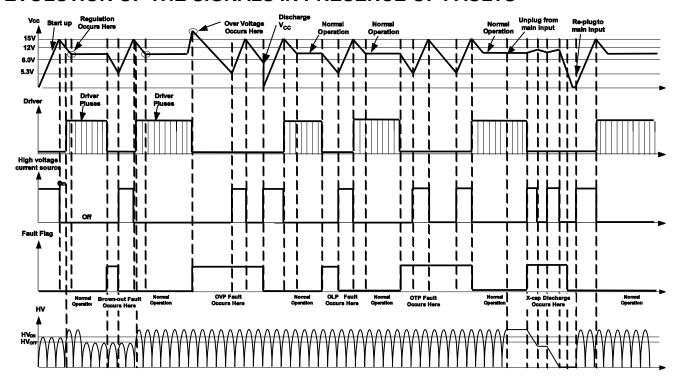

# **EVOLUTION OF THE SIGNALS IN PRESENCE OF FAULTS**

Figure 19: Signal Evolution in the Presence of Faults

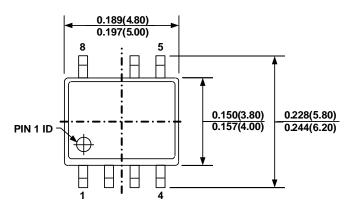

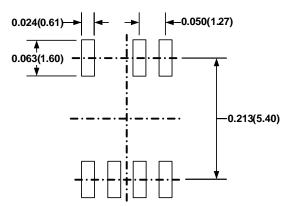

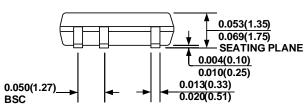

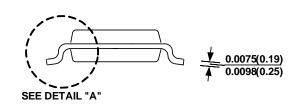

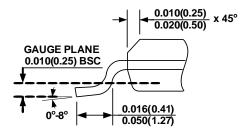

## PACKAGE INFORMATION

#### SOIC8-7A

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**SIDE VIEW**

**FRONT VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSIONS OR GATE BURRS

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING SHALL BE0.004" INCHES MAX

- 5) JEDEC REFERENCE IS MS-012.

- 6) DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

# http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

# Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru 4 moschip.ru 9