# 110 dB, 192-kHz 6-Ch CODEC with S/PDIF Receiver

#### **Features**

- ♦ Six 24-bit D/A, two 24-bit A/D Converters

- ♦ 110 dB DAC / 114 dB ADC Dynamic Range

- System Sampling Rates up to 192 kHz

- ♦ S/PDIF Receiver Compatible with EIAJ CP1201 and IEC-60958

- Recovered S/PDIF Clock or System Clock Selection

- ♦ 8:2 S/PDIF Input MUX

- ♦ ADC High-Pass Filter for DC Offset Calibration

- ♦ Expandable ADC Channels and One-Line Mode Support

- ♦ Digital Output Volume Control with Soft Ramp

- Digital ±15 dB Input Gain Adjust for ADC

- ♦ Differential Analog Architecture

- ♦ Supports Logic Levels between 1.8 V and 5 V

## **General Description**

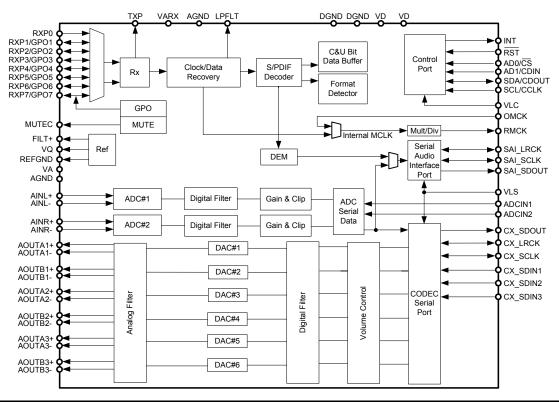

The CS42516 provides two analog-to-digital and six digital-to-analog delta-sigma converters, as well as an integrated S/PDIF receiver.

The CS42516 integrated S/PDIF receiver supports up to eight inputs, clock recovery circuitry and format autodetection. The internal stereo ADC is capable of independent channel gain control for single-ended or differential analog inputs. All six channels of DAC provide digital volume control and differential analog outputs. The general-purpose outputs may be driven high or low, or mapped to a variety of DAC mute controls or ADC overflow indicators.

The CS42516 is ideal for audio systems requiring wide dynamic range, negligible distortion and low noise, such as A/V receivers, DVD receivers, and digital speakers.

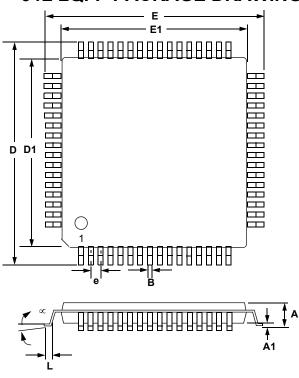

The CS42516 is available in a 64-pin LQFP package in Commercial (-10° to +70° C) grades. The CDB42518 Customer Demonstration board is also available for device evaluation. Refer to "Ordering Information" on page 90.

# TABLE OF CONTENTS

| 1. | . CHARACTERISTICS AND SPECIFICATIONS                               | 6  |

|----|--------------------------------------------------------------------|----|

|    | SPECIFIED OPERATING CONDITIONS                                     | 6  |

|    | ABSOLUTE MAXIMUM RATINGS                                           |    |

|    | ANALOG INPUT CHARACTERISTICS                                       |    |

|    | A/D DIGITAL FILTER CHARACTERISTICS                                 |    |

|    | ANALOG OUTPUT CHARACTERISTICS                                      |    |

|    | D/A DIGITAL FILTER CHARACTERISTICS                                 |    |

|    | SWITCHING CHARACTERISTICS                                          | 11 |

|    | SWITCHING CHARACTERISTICS - CONTROL PORT - I2CTM FORMAT            | 12 |

|    | SWITCHING CHARACTERISTICS - CONTROL PORT - SPI <sup>™</sup> FORMAT |    |

|    | DC ELECTRICAL CHARACTERISTICS                                      |    |

|    | DIGITAL INTERFACE CHARACTERISTICS                                  |    |

|    | PIN DESCRIPTIONS                                                   |    |

|    | . TYPICAL CONNECTION DIAGRAM                                       |    |

| 4. | APPLICATIONS                                                       |    |

|    | 4.1 Overview                                                       |    |

|    | 4.2 Analog Inputs                                                  |    |

|    | 4.2.1 Line-Level Inputs                                            |    |

|    | 4.2.2 High-Pass Filter and DC Offset Calibration                   |    |

|    | 4.3 Analog Outputs                                                 |    |

|    | 4.3.1 Line-Level Outputs and Filtering                             |    |

|    | 4.3.2 Interpolation Filter                                         |    |

|    | 4.3.3 Digital Volume and Mute Control                              |    |

|    | 4.3.4 ATAPI Specification                                          |    |

|    | 4.4 S/PDIF Receiver                                                |    |

|    | 4.4.1 8:2 S/PDIF Input Multiplexer                                 |    |

|    | 4.4.2 Error Reporting and Hold Function                            |    |

|    | 4.4.3 Channel Status Data Handling                                 |    |

|    | 4.4.4 User Data Handling                                           |    |

|    | 4.4.5 Non-Audio Auto-Detection                                     |    |

|    | 4.5.1 PLL and Jitter Attenuation                                   |    |

|    | 4.5.1 PLL and Jiller Alteridation 4.5.2 OMCK System Clock Mode     |    |

|    | 4.5.3 Master Mode                                                  |    |

|    | 4.5.4 Slave Mode                                                   |    |

|    | 4.6 Digital Interfaces                                             |    |

|    | 4.6.1 Serial Audio Interface Signals                               |    |

|    | 4.6.2 Serial Audio Interface Formats                               |    |

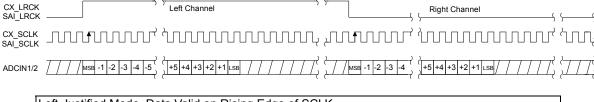

|    | 4.6.3 ADCIN1/ADCIN2 Serial Data Format                             |    |

|    | 4.6.4 One-Line Mode (OLM) Configurations                           |    |

|    | 4.6.4.1 OLM Config #1                                              |    |

|    | 4.6.4.2 OLM Config #2                                              |    |

|    | 4.6.4.3 OLM Config #3                                              |    |

|    | 4.6.4.4 OLM Config #4                                              |    |

|    | 4.6.4.5 OLM Config #5                                              |    |

|    | 4.7 Control Port Description and Timing                            |    |

|    | 4.7.1 SPI Mode                                                     |    |

|    | 4.7.2 I <sup>2</sup> C Mode                                        |    |

|    | 4.8 Interrupts                                                     |    |

|    | 4.9 Reset and Power-Up                                             |    |

|    | 4.10 Power Supply, Grounding, and PCB Layout                       |    |

| 5  | REGISTER QUICK REFERENCE                                           |    |

| 6. | REGISTER DESCRIPTION                                                   |    |

|----|------------------------------------------------------------------------|----|

|    | 6.1 Memory Address Pointer (MAP)                                       |    |

|    | 6.2 Chip I.D. and Revision Register (address 01h) (Read Only)          | 45 |

|    | 6.3 Power Control (address 02h)                                        | 46 |

|    | 6.4 Functional Mode (address 03h)                                      | 47 |

|    | 6.5 Interface Formats (address 04h)                                    | 49 |

|    | 6.6 Misc Control (address 05h)                                         | 50 |

|    | 6.7 Clock Control (address 06h)                                        | 52 |

|    | 6.8 OMCK/PLL_CLK Ratio (address 07h) (Read Only)                       | 53 |

|    | 6.9 RVCR Status (address 08h) (Read Only)                              |    |

|    | 6.10 Burst Preamble PC and PD Bytes (addresses 09h - 0Ch)(Read Only)   | 55 |

|    | 6.11 Volume Transition Control (address 0Dh)                           |    |

|    | 6.12 Channel Mute (address 0Eh)                                        | 58 |

|    | 6.13 Volume Control (addresses 0Fh, 10h, 11h, 12h, 13h, 14h)           | 58 |

|    | 6.14 Channel Invert (address 17h)                                      |    |

|    | 6.15 Mixing Control Pair 1 (Channels A1 & B1) (address 18h)            |    |

|    | Mixing Control Pair 2 (Channels A2 & B2) (address 19h)                 |    |

|    | Mixing Control Pair 3 (Channels A3 & B3) (address 1Ah)                 | 58 |

|    | 6.16 ADC Left Channel Gain (address 1Ch)                               | 61 |

|    | 6.17 ADC Right Channel Gain (address 1Dh)                              |    |

|    | 6.18 Receiver Mode Control (address 1Eh)                               |    |

|    | 6.19 Receiver Mode Control 2 (address 1Fh)                             |    |

|    | 6.20 Interrupt Status (address 20h) (Read Only)                        |    |

|    | 6.21 Interrupt Mask (address 21h)                                      |    |

|    | 6.22 Interrupt Mode MSB (address 22h)                                  |    |

|    | Interrupt Mode LSB (address 23h)                                       | 65 |

|    | 6.23 Channel Status Data Buffer Control (address 24h)                  | 65 |

|    | 6.24 Receiver Channel Status (address 25h) (Read Only)                 | 66 |

|    | 6.25 Receiver Errors (address 26h) (Read Only)                         | 67 |

|    | 6.26 Receiver Errors Mask (address 27h)                                | 68 |

|    | 6.27 Mutec Pin Control (address 28h)                                   | 69 |

|    | 6.28 RXP/General-Purpose Pin Control (addresses 29h to 2Fh)            | 69 |

|    | 6.29 Q-Channel Subcode Bytes 0 to 9 (addresses 30h to 39h) (Read Only) | 71 |

|    | 6.30 C-Bit or U-Bit Data Buffer (addresses 3Ah to 51h) (Read Only)     | 71 |

| 7. | PARAMETER DEFINITIONS                                                  | 72 |

| 8. | APPENDIX A: EXTERNAL FILTERS                                           | 73 |

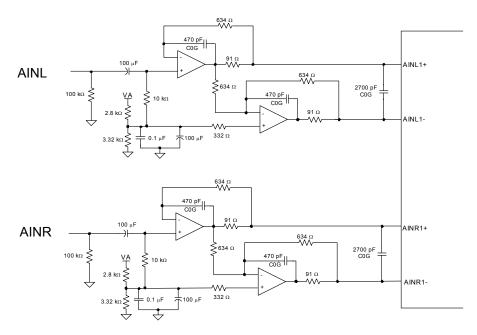

|    | 8.1 ADC Input Filter                                                   | 73 |

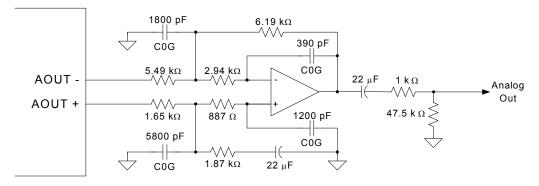

|    | 8.2 DAC Output Filter                                                  |    |

| 9. | APPENDIX B: S/PDIF RECEIVER                                            | 74 |

|    | 9.1 Error Reporting and Hold Function                                  | 74 |

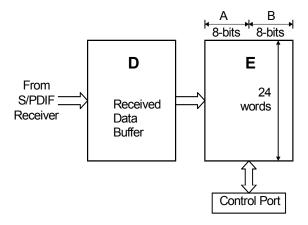

|    | 9.2 Channel Status Data Handling                                       | 74 |

|    | 9.2.1 Channel Status Data E Buffer Access                              | 75 |

|    | 9.2.1.1 One-Byte Mode                                                  | 75 |

|    | 9.2.1.2 Two-Byte Mode                                                  | 75 |

|    | 9.2.2 Serial Copy Management System (SCMS)                             | 76 |

|    | 9.3 User (U) Data E Buffer Access                                      | 76 |

|    | 9.3.1 Non-Audio Auto-Detection                                         | 76 |

|    | 9.3.1.1 Format Detection                                               | 76 |

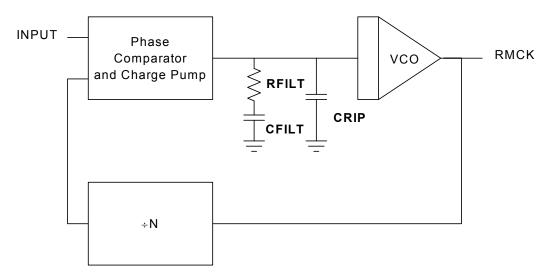

| 10 | D. APPENDIX C: PLL FILTER                                              | 77 |

|    | 10.1 External Filter Components                                        | 77 |

|    | 10.1.1 General                                                         |    |

|    | 10.1.2 Jitter Attenuation                                              |    |

|    | 10.1.3 Capacitor Selection                                             |    |

|    | 10.1.4 Circuit Board Layout                                            | 81 |

| 11. APPENDIX D: EXTERNAL AES3-S/PDIF-IEC60958 RECEIVER COMPONENTS           |    |

|-----------------------------------------------------------------------------|----|

| 11.1 AES3 Receiver External Components                                      |    |

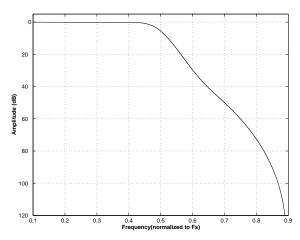

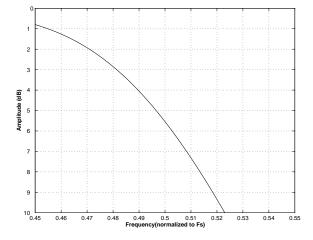

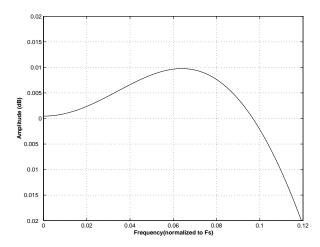

| 12. APPENDIX E: ADC FILTER PLOTS                                            |    |

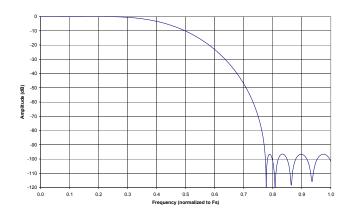

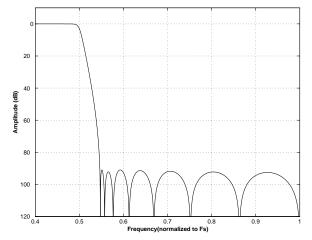

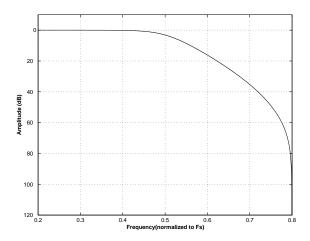

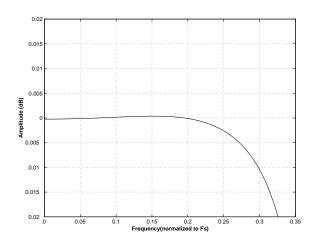

| 13. APPENDIX F: DAC FILTER PLOTS                                            |    |

| 14. PACKAGE DIMENSIONS                                                      |    |

| THERMAL CHARACTERISTICS                                                     | 89 |

| 15. ORDERING INFORMATION                                                    | 90 |

| 16. REFERENCES                                                              | 90 |

| 17. REVISION HISTORY                                                        | 91 |

| LIST OF FIGURES                                                             |    |

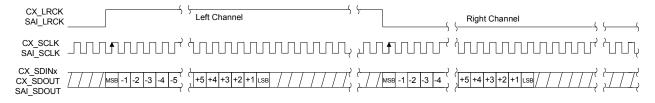

| Figure 1. Serial Audio Port Master Mode Timing                              |    |

| Figure 2. Serial Audio Port Slave Mode Timing                               | 11 |

| Figure 3. Control Port Timing - I <sup>2</sup> C Format                     | 12 |

| Figure 4. Control Port Timing - SPI Format                                  | 13 |

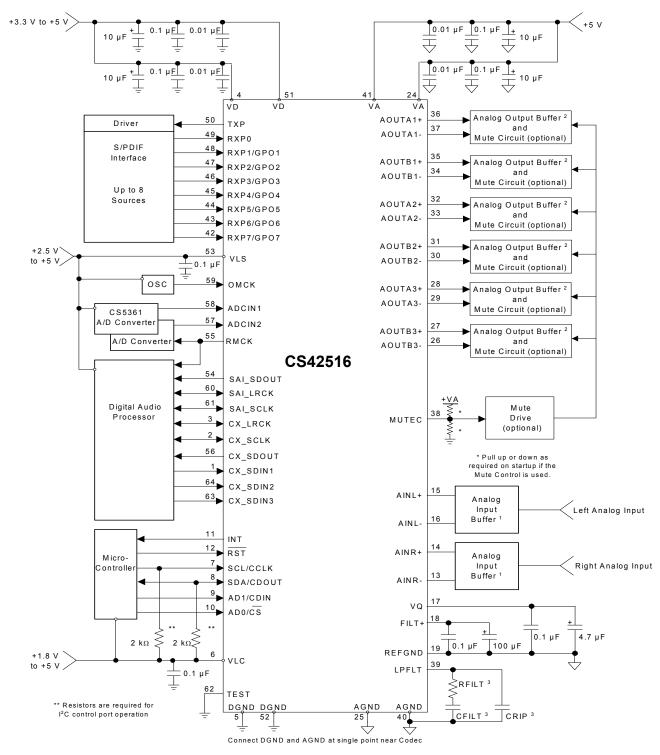

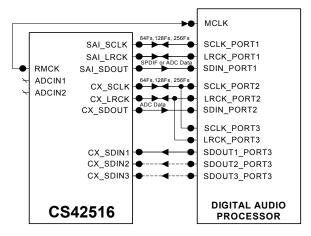

| Figure 5. Typical Connection Diagram                                        | 19 |

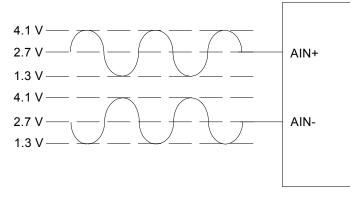

| Figure 6. Full-Scale Analog Input                                           |    |

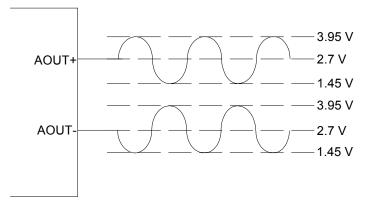

| Figure 7. Full-Scale Output                                                 | 21 |

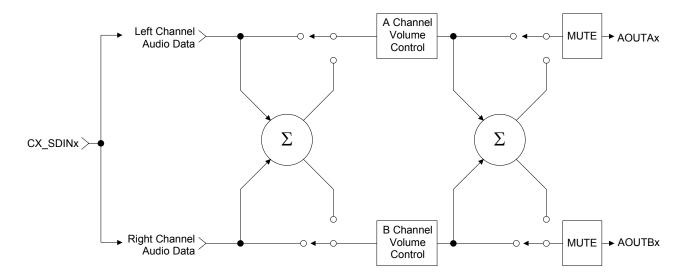

| Figure 8. ATAPI Block Diagram (x = channel pair 1, 2, or 3)                 | 22 |

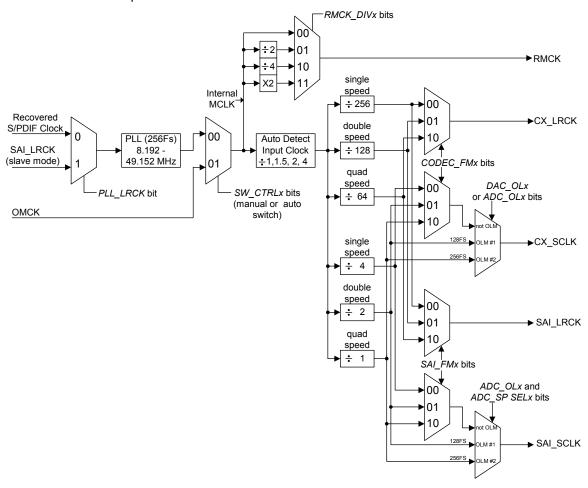

| Figure 9. CS42516 Clock Generation                                          |    |

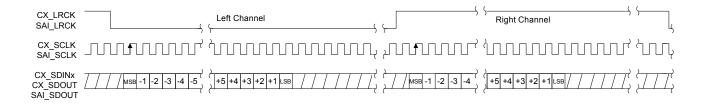

| Figure 10. I2S Serial Audio Formats                                         | 28 |

| Figure 11. Left-Justified Serial Audio Formats                              | 29 |

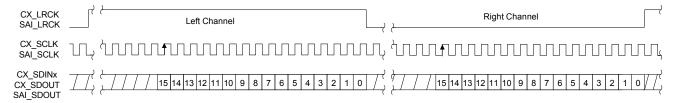

| Figure 12. Right-Justified Serial Audio Formats                             | 29 |

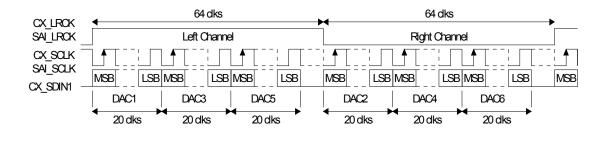

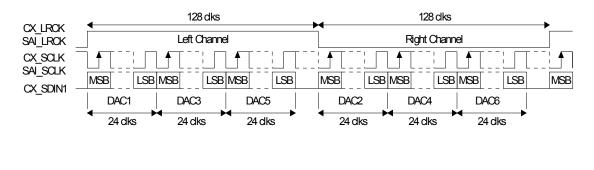

| Figure 13. One Line Mode #1 Serial Audio Format                             |    |

| Figure 14. One Line Mode #2 Serial Audio Format                             | 30 |

| Figure 15. ADCIN1/ADCIN2 Serial Audio Format                                | 31 |

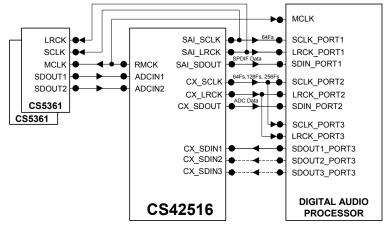

| Figure 16. OLM Configuration #1                                             |    |

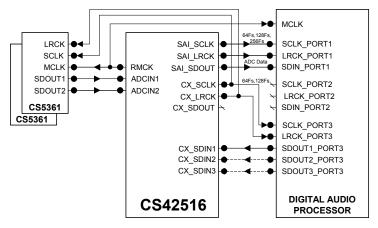

| Figure 17. OLM Configuration #2                                             | 33 |

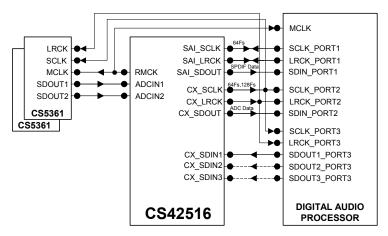

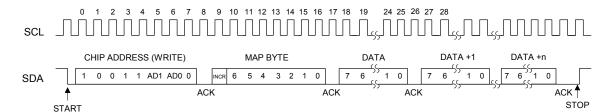

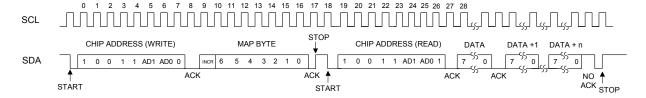

| Figure 18. OLM Configuration #3                                             | 34 |

| Figure 19. OLM Configuration #4                                             |    |

| Figure 20. OLM Configuration #5                                             | 36 |

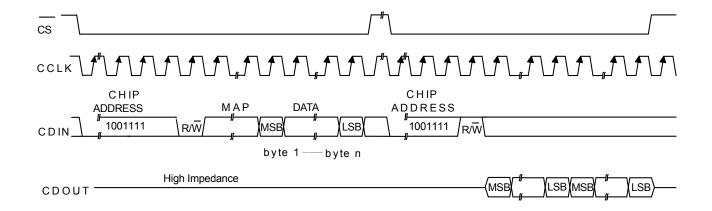

| Figure 21. Control Port Timing in SPI Mode                                  | 37 |

| Figure 22. Control Port Timing, I <sup>2</sup> C Write                      | 38 |

| Figure 23. Control Port Timing, I <sup>2</sup> C Read                       | 38 |

| Figure 24. Recommended Analog Input Buffer                                  | 73 |

| Figure 25. Recommended Analog Output Buffer                                 | 73 |

| Figure 26. Channel Status Data Buffer Structure                             |    |

| Figure 27. PLL Block Diagram                                                | 77 |

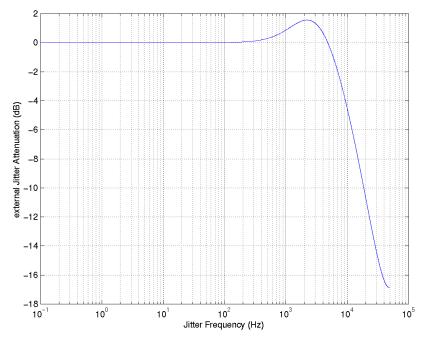

| Figure 28. Jitter-Attenuation Characteristics of PLL - Configurations 1 & 2 | 79 |

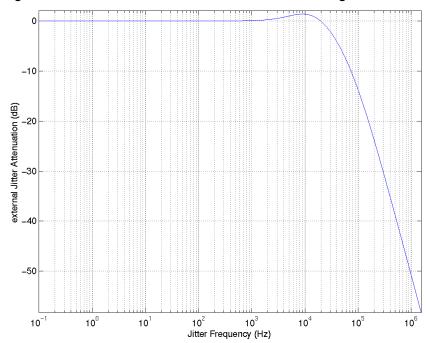

| Figure 29. Jitter-Attenuation Characteristics of PLL - Configuration 3      | 79 |

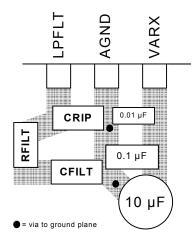

| Figure 30. Recommended Layout Example                                       | 81 |

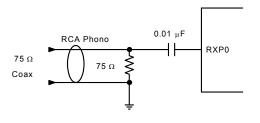

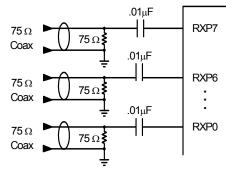

| Figure 31. Consumer Input Circuit                                           | 82 |

| Figure 32. S/PDIF MUX Input Circuit                                         | 82 |

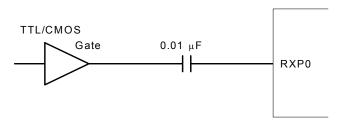

| Figure 33. TTL/CMOS Input Circuit                                           | 82 |

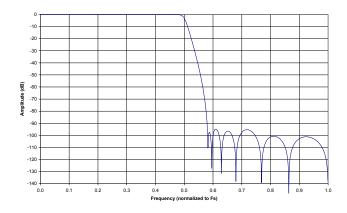

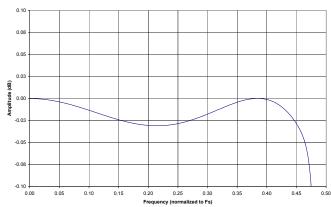

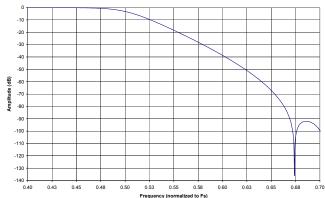

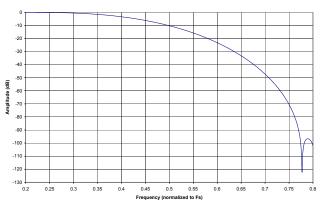

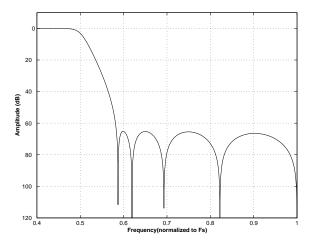

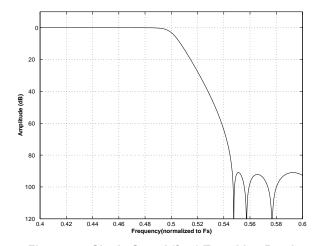

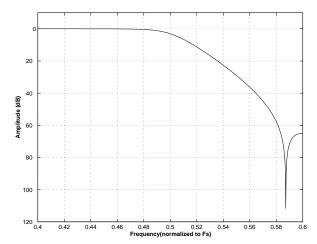

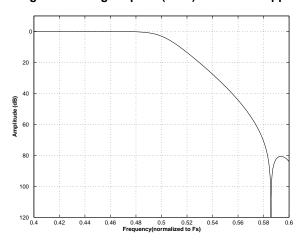

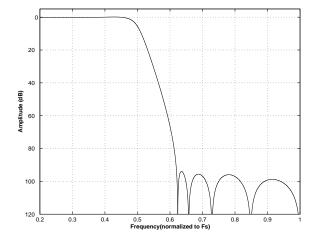

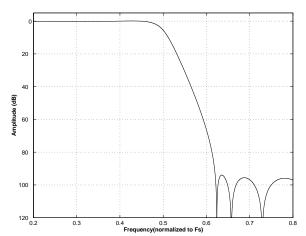

| Figure 34. Single-Speed Mode Stopband Rejection                             | 83 |

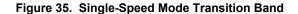

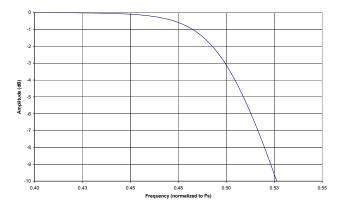

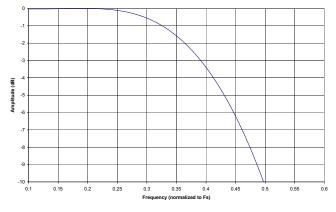

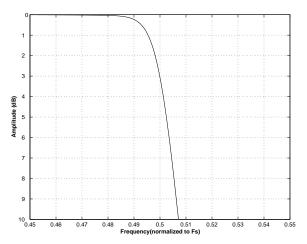

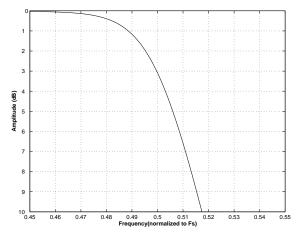

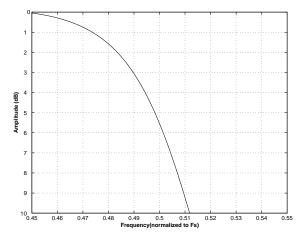

| Figure 35. Single-Speed Mode Transition Band                                | 83 |

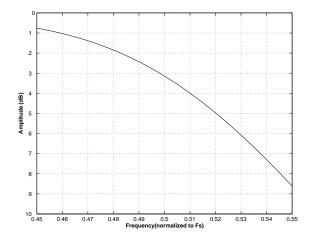

| Figure 36. Single-Speed Mode Transition Band (Detail)                       | 83 |

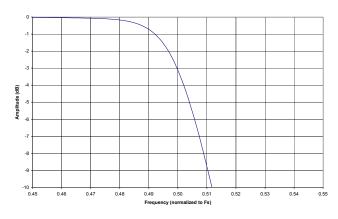

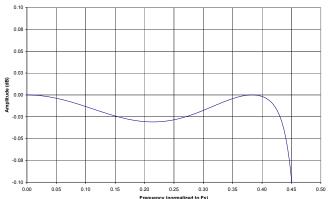

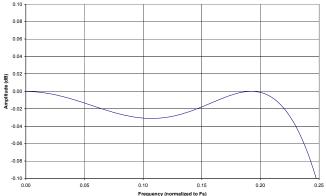

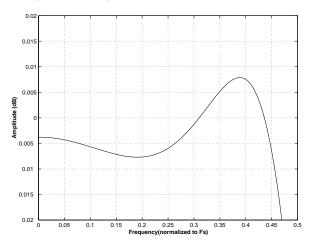

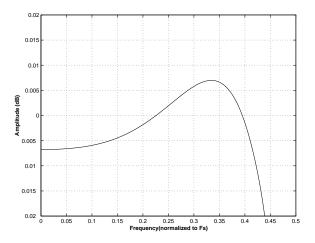

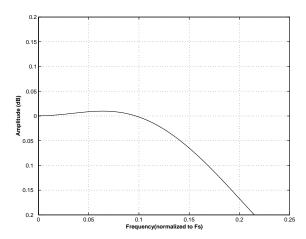

| Figure 37. Single-Speed Mode Passband Ripple                                | 83 |

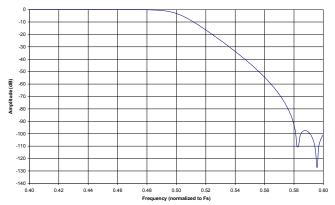

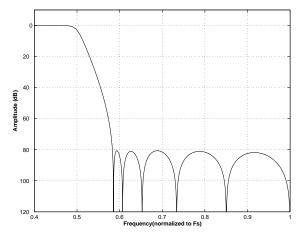

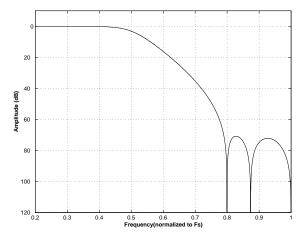

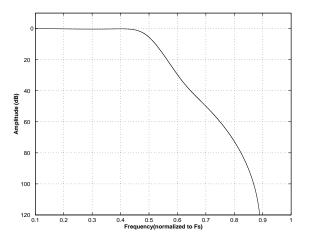

| Figure 38. Double-Speed Mode Stopband Rejection                             |    |

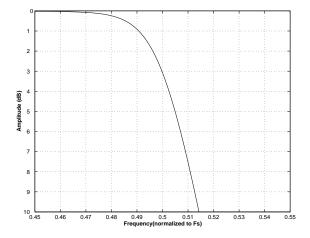

| Figure 39. Double-Speed Mode Transition Band                                | 83 |

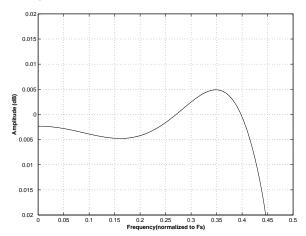

| Figure 40. Double-Speed Mode Transition Band (Detail)                       |    |

| Figure 41. Double-Speed Mode Passband Ripple                                |    |

| Figure 42. Quad-Speed Mode Stopband Rejection                               | 84 |

|                                                                             |    |

|      | E 40.0 10 1M 1 E 32 B 1                                 | ~ 4  |

|------|---------------------------------------------------------|------|

|      | Figure 43. Quad-Speed Mode Transition Band              |      |

|      | Figure 44. Quad-Speed Mode Transition Band (Detail)     |      |

|      | Figure 45. Quad-Speed Mode Passband Ripple              |      |

|      | Figure 46. Single-Speed (fast) Stopband Rejection       |      |

|      | Figure 47. Single-Speed (fast) Transition Band          |      |

|      | Figure 48. Single-Speed (fast) Transition Band (detail) | . 85 |

|      | Figure 49. Single-Speed (fast) Passband Ripple          | . 85 |

|      | Figure 50. Single-Speed (slow) Stopband Rejection       | . 85 |

|      | Figure 51. Single-Speed (slow) Transition Band          | . 85 |

|      | Figure 52. Single-Speed (slow) Transition Band (detail) | . 86 |

|      | Figure 53. Single-Speed (slow) Passband Ripple          | . 86 |

|      | Figure 54. Double-Speed (fast) Stopband Rejection       | . 86 |

|      | Figure 55. Double-Speed (fast) Transition Band          | . 86 |

|      | Figure 56. Double-Speed (fast) Transition Band (detail) |      |

|      | Figure 57. Double-Speed (fast) Passband Ripple          |      |

|      | Figure 58. Double-Speed (slow) Stopband Rejection       |      |

|      | Figure 59. Double-Speed (slow) Transition Band          |      |

|      | Figure 60. Double-Speed (slow) Transition Band (detail) |      |

|      | Figure 61. Double-Speed (slow) Passband Ripple          |      |

|      | Figure 62. Quad-Speed (fast) Stopband Rejection         |      |

|      | Figure 63. Quad-Speed (fast) Transition Band            |      |

|      | Figure 64. Quad-Speed (fast) Transition Band (detail)   |      |

|      | Figure 65. Quad-Speed (fast) Passband Ripple            |      |

|      | Figure 66. Quad-Speed (slow) Stopband Rejection         |      |

|      | Figure 67. Quad-Speed (slow) Transition Band            |      |

|      | Figure 68. Quad-Speed (slow) Transition Band (detail)   |      |

|      | Figure 69. Quad-Speed (slow) Passband Ripple            |      |

|      | riguio co. quad opoca (cion) i accedina rappio          |      |

| LIST | OF TABLES                                               |      |

|      | Table 1 Common OMCK Clock Fraguencies                   | 25   |

|      | Table 1. Common OMCK Clock Frequencies                  |      |

|      | Table 2. Common PLL Output Clock Frequencies            |      |

|      | Table 3. Slave Mode Clock Ratios                        |      |

|      | Table 4. Serial Audio Port Channel Allocations          |      |

|      | Table 5. DAC De-Emphasis                                |      |

|      | Table 6. Receiver De-Emphasis                           |      |

|      | Table 7. Digital Interface Formats                      |      |

|      | Table 8. ADC One-Line Mode                              |      |

|      | Table 9. DAC One-Line Mode                              |      |

|      | Table 10. RMCK Divider Settings                         |      |

|      | Table 11. OMCK Frequency Settings                       |      |

|      | Table 12. Master Clock Source Select                    |      |

|      | Table 13. AES Format Detection                          |      |

|      | Table 14. Receiver Clock Frequency Detection            |      |

|      | Table 15. Example Digital Volume Settings               |      |

|      | Table 16. ATAPI Decode                                  |      |

|      | Table 17. Example ADC Input Gain Settings               |      |

|      | Table 18. TXP Output Selection                          |      |

|      | Table 19. Receiver Input Selection                      |      |

|      | Table 20. Auxiliary Data Width Selection                |      |

|      | Table 21. External PLL Component Values & Locking Modes | . 77 |

# 1. CHARACTERISTICS AND SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and  $T_A = 25^{\circ}$  C.)

### SPECIFIED OPERATING CONDITIONS

(AGND=DGND=0, all voltages with respect to ground; OMCK=12.288 MHz; Master Mode)

| Parameter                                     |                        | Symbol         | Min  | Тур | Max  | Units |

|-----------------------------------------------|------------------------|----------------|------|-----|------|-------|

| DC Power Supply                               | Analog                 | VA / VARX      | 4.75 | 5.0 | 5.25 | V     |

|                                               | Digital                | VD             | 3.13 | 3.3 | 5.25 | V     |

|                                               | Serial Port Interface  | VLS            | 1.8  | 5.0 | 5.25 | V     |

| C                                             | Control Port Interface | VLC            | 1.8  | 5.0 | 5.25 | V     |

| Ambient Operating Temperature (power applied) |                        | T <sub>A</sub> | -10  | -   | +70  | °C    |

### ABSOLUTE MAXIMUM RATINGS

(AGND = DGND = 0 V; all voltages with respect to ground.)

| Paramete                          | ers                    | Symbol              | Min      | Max      | Units |

|-----------------------------------|------------------------|---------------------|----------|----------|-------|

| DC Power Supply                   | Analog                 | VA / VARX           | -0.3     | 6.0      | V     |

|                                   | Digital                | VD                  | -0.3     | 6.0      | V     |

|                                   | Serial Port Interface  | VLS                 | -0.3     | 6.0      | V     |

|                                   | Control Port Interface | VLC                 | -0.3     | 6.0      | V     |

| Input Current                     | (Note 1)               | l <sub>in</sub>     | -        | ±10      | mA    |

| Analog Input Voltage              | (Note 2)               | V <sub>IN</sub>     | AGND-0.7 | VA+0.7   | V     |

| Digital Input Voltage             | Serial Port Interface  | V <sub>IND-S</sub>  | -0.3     | VLS+ 0.4 | V     |

| (Note 2)                          | Control Port Interface | V <sub>IND-C</sub>  | -0.3     | VLC+ 0.4 | V     |

|                                   | S/PDIF interface       | $V_{\text{IND-SP}}$ | -0.3     | VARX+0.4 | V     |

| Ambient Operating Temperature(pow | er applied)            | T <sub>A</sub>      | -20      | +85      | °C    |

|                                   |                        | TA                  | -50      | +95      | °C    |

| Storage Temperature               |                        | T <sub>stg</sub>    | -65      | +150     | °C    |

**WARNING:** Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

#### Notes:

- 1. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

- 2. The maximum over/under voltage is limited by the input current.

# **ANALOG INPUT CHARACTERISTICS**

$(T_A = 25^{\circ} \text{ C}; \text{ VA} = \text{VARX} = 5 \text{ V}, \text{ VD} = 3.3 \text{ V}, \text{Logic "0"} = \text{DGND} = \text{AGND} = 0 \text{ V}; \text{Logic "1"} = \text{VLS} = \text{VLC} = 5 \text{ V}; \text{Measurement Bandwidth is 10 Hz to 20 kHz unless otherwise specified. Full-scale input sine wave, 997 Hz.; PDN_RCVR = 1; SW_CTRL[1:0] = '01'; OMCK = 12.288 MHz; Single-Speed Mode CX_SCLK = 3.072 MHz; Double-Speed Mode CX_SCLK = 6.144 MHz; Quad-Speed Mode CX_SCLK = 12.288 MHz.)$

| Paramet                                 | er                           | Symb         | ol Min   | Тур         | Max      | Unit     |

|-----------------------------------------|------------------------------|--------------|----------|-------------|----------|----------|

| Single-Speed Mode (Fs=48 kHz)           |                              | l            | •        |             |          |          |

| Dynamic Range                           | A-weigh                      |              | 108      | 114         | -        | dB       |

|                                         | unweigh                      | nted         | 105      | 111         | -        | dB       |

| Total Harmonic Distortion + Noise       |                              |              |          |             |          |          |

| (Note 3)                                |                              | dB THD+      | N -      | -100        | -94      | dB       |

|                                         |                              | ) aB         | -        | -91         | -        | dB       |

| D. I.I. O. I.M. I. (5. 00.111.)         | -60                          | ) dB         | -        | -51         | -        | dB       |

| Double-Speed Mode (Fs=96 kHz)           | A                            | -4           | 100      | 1444        |          | ID.      |

| Dynamic Range                           | A-weigh<br>unweigh           |              | 108      | 114<br>111  | -        | dB<br>dB |

|                                         | 40 kHz bandwidth unweigh     |              | 105      | 108         | -        | dB<br>dB |

| Total Harmonic Distortion + Noise       | 40 Ki iz bandwidtii diiweigi | iteu         |          | 100         | -        | uБ       |

| (Note 3)                                | _1                           | dB           |          | -100        | -94      | dB       |

| (Note 3)                                |                              | dB THD+      | N -      | -100<br>-91 | -94      | dВ       |

|                                         |                              | ) dB   IIID+ | _        | -51<br>-51  | _        | dB<br>dB |

|                                         |                              | dB           | _        | -97         | _        | dB       |

| Quad-Speed Mode (Fs=192 kHz)            |                              | *            |          |             | <u> </u> | u.b      |

| Dynamic Range                           | A-weigh                      | nted         | 108      | 114         | -        | dB       |

|                                         | unweigh                      |              | 105      | 111         | -        | dB       |

|                                         | 40 kHz bandwidth unweigh     | nted         | -        | 108         | -        | dB       |

| Total Harmonic Distortion+ Noise        |                              | İ            |          |             |          |          |

| (Note 3)                                | -1                           | dB           | -        | -100        | -94      | dB       |

|                                         |                              | dB THD+      | N -      | -91         | -        | dB       |

|                                         |                              | ) dB         | -        | -51         | -        | dB       |

|                                         |                              | dB           | -        | -97         | -        | dB       |

| Dynamic Performance for All Mod         | les                          |              |          |             |          |          |

| Interchannel Isolation                  |                              |              | -        | 110         | -        | dB       |

| Interchannel Phase Deviation            |                              |              | -        | 0.0001      | -        | Degree   |

| DC Accuracy                             |                              | •            | <u> </u> | II.         |          | I.       |

| Interchannel Gain Mismatch              |                              |              | -        | 0.1         | -        | dB       |

| Gain Drift                              |                              |              | -        | +/-100      | -        | ppm/°C   |

| Offset Error                            | HPF FREEZE disal             | oled         | -        | 0           | -        | LSB      |

|                                         | HPF_FREEZE enal              |              | -        | 100         | -        | LSB      |

| Analog Input                            |                              |              | II.      | I           |          | I.       |

| Full-scale Differential Input Voltage   |                              |              | 1.05 VA  | 1.10 VA     | 1.16 VA  | Vpp      |

| Input Impedance (Differential) (Note 4) |                              |              | 17       | -           | -        | kΩ       |

| Common Mode Rejection Ratio             |                              | CMRF         | ₹ -      | 82          | -        | dB       |

#### Notes:

- 3. Referred to the typical full-scale voltage.

- 4. Measured between AIN+ and AIN-

# A/D DIGITAL FILTER CHARACTERISTICS

| Parameter                                      |          | Symbol              | Min  | Тур                 | Max    | Unit     |

|------------------------------------------------|----------|---------------------|------|---------------------|--------|----------|

| Single-Speed Mode (2 to 50 kHz sample rates)   |          |                     |      |                     |        |          |

| Passband (-0.1 dB)                             | (Note 5) |                     | 0    | -                   | 0.47   | Fs       |

| Passband Ripple                                |          |                     | -    | -                   | ±0.035 | dB       |

| Stopband                                       | (Note 5) |                     | 0.58 | -                   | -      | Fs       |

| Stopband Attenuation                           |          |                     | -95  | -                   | -      | dB       |

| Total Group Delay (Fs = Output Sample Rate)    |          | t <sub>gd</sub>     | -    | 12/Fs               | -      | s        |

| Group Delay Variation vs. Frequency            |          | $\Delta t_{\sf gd}$ | -    | -                   | 0.0    | μS       |

| Double-Speed Mode (50 to 100 kHz sample rates) |          |                     |      |                     | "      |          |

| Passband (-0.1 dB)                             | (Note 5) |                     | 0    | -                   | 0.45   | Fs       |

| Passband Ripple                                |          |                     | -    | -                   | ±0.035 | dB       |

| Stopband                                       | (Note 5) |                     | 0.68 | -                   | -      | Fs       |

| Stopband Attenuation                           |          |                     | -92  | -                   | -      | dB       |

| Total Group Delay (Fs = Output Sample Rate)    |          | t <sub>gd</sub>     | -    | 9/Fs                | -      | s        |

| Group Delay Variation vs. Frequency            |          | $\Delta t_{\sf gd}$ | -    | -                   | 0.0    | μS       |

| Quad-Speed Mode (100 to 192 kHz sample rates)  |          |                     |      |                     | •      |          |

| Passband (-0.1 dB)                             | (Note 5) |                     | 0    | -                   | 0.24   | Fs       |

| Passband Ripple                                |          |                     | -    | -                   | ±0.035 | dB       |

| Stopband                                       | (Note 5) |                     | 0.78 | -                   | -      | Fs       |

| Stopband Attenuation                           |          |                     | -97  | -                   | -      | dB       |

| Total Group Delay (Fs = Output Sample Rate)    |          | t <sub>gd</sub>     | -    | 5/Fs                | -      | s        |

| Group Delay Variation vs. Frequency            |          | $\Delta t_{\sf gd}$ | -    | -                   | 0.0    | μS       |

| High-Pass Filter Characteristics               |          |                     |      |                     | •      |          |

| Frequency Response -3.0 dB<br>-0.13 dB         | (Note 6) |                     | -    | 1<br>20             | -      | Hz<br>Hz |

| Phase Deviation @ 20 Hz                        | (Note 6) |                     | _    | 10                  | -      | Deg      |

| Passband Ripple                                | ` '      |                     | _    | -                   | 0      | dB       |

| Filter Setting Time                            |          |                     | -    | 10 <sup>5</sup> /Fs | -      | S        |

### Notes:

- 5. The filter frequency response scales precisely with Fs.

- 6. Response shown is for Fs equal to 48 kHz. Filter characteristics scale with Fs.

# **ANALOG OUTPUT CHARACTERISTICS**

$(T_A$  = 25° C; VA =VARX= 5 V, VD = 3.3 V, Logic "0" = DGND =AGND = 0 V; Logic "1" = VLS = VLC = 5V; Measurement Bandwidth 10 Hz to 20 kHz unless otherwise specified.; Full-scale output 997 Hz sine wave, Test load R<sub>L</sub> = 3 k $\Omega$ , C<sub>L</sub> = 30 pF; PDN\_RCVR = 1; SW\_CTRL[1:0] = '01'; OMCK = 12.288 MHz; Single-Speed Mode, CX\_SCLK = 3.072 MHz; Double-Speed Mode, CX\_SCLK = 6.144 MHz; Quad-Speed Mode, CX\_SCLK = 12.288 MHz.)

| Parameter                                        |             |           | Symbol           | Min    | Тур    | Max    | Unit   |

|--------------------------------------------------|-------------|-----------|------------------|--------|--------|--------|--------|

| Dynamic performance for all modes                |             |           |                  |        |        |        | I.     |

| Dynamic Range (Note 7)                           |             |           |                  |        |        |        |        |

|                                                  |             | Weighted  |                  | 104    | 110    | -      | dB     |

|                                                  |             | nweighted |                  | 101    | 107    | -      | dB     |

|                                                  |             | Weighted  |                  | -      | 97     | -      | dB     |

|                                                  | (Note 8) ui | nweighted |                  | -      | 94     | -      | dB     |

| Total Harmonic Distortion + Noise                |             |           |                  |        |        |        |        |

|                                                  | 24-bit      | 0 dB      |                  | -      | -100   | -94    | dB     |

|                                                  |             | -20 dB    |                  | -      | -91    | -      | dB     |

|                                                  |             | -60 dB    | THD+N            | -      | -51    | -      | dB     |

|                                                  | 16-bit      | 0 dB      |                  | -      | -94    | -      | dB     |

|                                                  | (Note       | 8) -20 dB |                  | -      | -74    | -      | dB     |

|                                                  |             | -60 dB    |                  | -      | -34    |        | dB     |

| Idle Channel Noise/Signal-to-Noise Ratio (A-Weig | ghted)      |           |                  | -      | 110    | -      | dB     |

| Interchannel Isolation                           |             | (1 kHz)   |                  | -      | 90     | -      | dB     |

| Analog Output Characteristics for all mod        | des         |           |                  |        |        |        |        |

| Unloaded Full-Scale Differential Output Voltage  |             |           | V <sub>FS</sub>  | .89 VA | .94 VA | .99 VA | Vpp    |

| Interchannel Gain Mismatch                       |             |           |                  | -      | 0.1    | -      | dB     |

| Gain Drift                                       |             |           |                  | -      | 300    | -      | ppm/°C |

| Output Impedance                                 |             |           | Z <sub>OUT</sub> | -      | 150    | -      | Ω      |

| AC-Load Resistance                               |             |           | $R_L$            | 3      | -      | -      | kΩ     |

| Load Capacitance                                 |             |           | $C_L$            | -      | -      | 30     | pF     |

#### Notes:

- 7. One LSB of triangular PDF dither is added to data.

- 8. Performance limited by 16-bit quantization noise.

# D/A DIGITAL FILTER CHARACTERISTICS

|                                |                   | I      | Fast Roll- | Off         | Slow Roll-Off |        | -Off     |      |

|--------------------------------|-------------------|--------|------------|-------------|---------------|--------|----------|------|

| Parameter                      |                   | Min    | Тур        | Max         | Min           | Тур    | Max      | Unit |

| Combined Digital and On-chi    | p Analog Filter   | Respon | se - Singi | le-Speed Me | ode - 48 F    | кНz    |          | •    |

| Passband (Note 9) to           | o -0.01 dB corner | 0      | -          | 0.4535      | 0             | -      | 0.4166   | Fs   |

|                                | to -3 dB corner   | 0      | -          | 0.4998      | 0             | -      | 0.4998   | Fs   |

| Frequency Response 10 Hz to 20 | kHz               | -0.01  | -          | +0.01       | -0.01         | -      | +0.01    | dB   |

| StopBand                       |                   | 0.5465 | -          | -           | 0.5834        | -      | -        | Fs   |

| StopBand Attenuation           | (Note 10)         | 90     | -          | -           | 64            | -      | -        | dB   |

| Group Delay                    |                   | -      | 12/Fs      | -           | -             | 6.5/Fs | -        | S    |

| Passband Group Delay Deviation | 0 - 20 kHz        | -      | -          | ±0.41/Fs    |               | -      | ±0.14/Fs | S    |

| De-emphasis Error (Note 11)    | Fs = 32 kHz       | -      | -          | ±0.23       | -             | -      | ±0.23    | dB   |

| (Relative to 1 kHz)            | Fs = 44.1 kHz     | -      | -          | ±0.14       | -             | -      | ±0.14    | dB   |

|                                | Fs = 48 kHz       | -      | -          | ±0.09       | -             | -      | ±0.09    | dB   |

| Combined Digital and On-chi    | p Analog Filter   | Respon | se - Doub  | ole-Speed M | lode - 96     | kHz    |          |      |

| Passband (Note 9) to           | o -0.01 dB corner | 0      | -          | 0.4166      | 0             | -      | 0.2083   | Fs   |

|                                | to -3 dB corner   | 0      | -          | 0.4998      | 0             | -      | 0.4998   | Fs   |

| Frequency Response 10 Hz to 20 | kHz               | -0.01  | -          | 0.01        | -0.01         | -      | 0.01     | dB   |

| StopBand                       |                   | 0.5834 | -          | -           | 0.7917        | -      | -        | Fs   |

| StopBand Attenuation           | (Note 10)         | 80     | -          | -           | 70            | -      | -        | dB   |

| Group Delay                    |                   | -      | 4.6/Fs     | -           | -             | 3.9/Fs | -        | s    |

| Passband Group Delay Deviation | 0 - 20 kHz        | -      | -          | ±0.03/Fs    |               | -      | ±0.01/Fs | S    |

| Combined Digital and On-chi    | p Analog Filter   | Respon | se - Quad  | I-Speed Mo  | de - 192 l    | kHz    |          | •    |

| Passband (Note 9) to           | o -0.01 dB corner | 0      | -          | 0.1046      | 0             | -      | 0.1042   | Fs   |

|                                | to -3 dB corner   | 0      | -          | 0.4897      | 0             | -      | 0.4813   | Fs   |

| Frequency Response 10 Hz to 20 | kHz               | -0.01  | -          | 0.01        | -0.01         | -      | 0.01     | dB   |

| StopBand                       |                   | 0.6355 | -          | -           | 0.8683        | -      | -        | Fs   |

| StopBand Attenuation           | (Note 10)         | 90     | -          | -           | 75            | -      | -        | dB   |

| Group Delay                    |                   | -      | 4.7/Fs     | -           | -             | 4.2/Fs | -        | s    |

| Passband Group Delay Deviation | 0 - 20 kHz        | -      | -          | ±0.01/Fs    |               | -      | ±0.01/Fs | S    |

#### Notes:

- 9. Response is clock dependent and will scale with Fs. Note that the response plots (Figures 46 to 69) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

- 10. Single- and Double-Speed Mode Measurement Bandwidth is from stopband to 3 Fs. Quad-Speed Mode Measurement Bandwidth is from stopband to 1.34 Fs.

- 11. De-emphasis is available only in Single-Speed Mode.

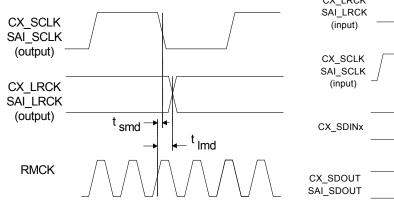

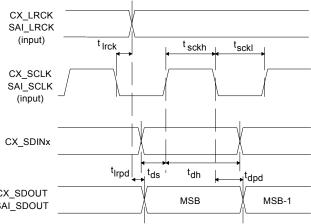

## **SWITCHING CHARACTERISTICS**

$(T_A = -10 \text{ to } +70^{\circ} \text{ C}; VA=VARX = 5 \text{ V}, VD=VLC= 3.3 \text{ V}, VLS= 1.8 \text{ V to } 5.25 \text{ V}; Inputs: Logic 0 = DGND, Logic 1 = VLS, C_1 = 30 pF)$

| Parameters                                                         | Symbol            | Min   | Тур | Max       | Units  |

|--------------------------------------------------------------------|-------------------|-------|-----|-----------|--------|

| RST Pin Low Pulse Width (Note 12)                                  |                   | 1     | -   | -         | ms     |

| PLL Clock Recovery Sample Rate Range                               |                   | 30    | -   | 200       | kHz    |

| RMCK Output Jitter (Note 14)                                       |                   | -     | 200 | -         | ps RMS |

| RMCK Output Duty Cycle (Note 15)                                   |                   | 45    | 50  | 55        | %      |

| OMCK Frequency (Note 13)                                           |                   | 1.024 | -   | 25.600    | MHz    |

| OMCK Duty Cycle (Note 13)                                          |                   | 40    | 50  | 60        | %      |

| CX_SCLK, SAI_SCLK Duty Cycle                                       |                   | 45    | 50  | 55        | %      |

| CX_LRCK, SAI_LRCK Duty Cycle                                       |                   | 45    | 50  | 55        | %      |

| Master Mode                                                        |                   |       |     |           |        |

| RMCK to CX_SCLK, SAI_SCLK active edge delay                        | t <sub>smd</sub>  | 0     | -   | 15        | ns     |

| RMCK to CX_LRCK, SAI_LRCK delay                                    | t <sub>lmd</sub>  | 0     | -   | 15        | ns     |

| Slave Mode                                                         |                   |       |     |           |        |

| CX_SCLK, SAI_SCLK Falling Edge to CX_SDOUT, SAI_SDOUT Output Valid | t <sub>dpd</sub>  |       | -   | (Note 16) | ns     |

| CX_LRCK, SAI_LRCK Edge to MSB Valid                                | t <sub>Irpd</sub> |       | -   | 26.5      | ns     |

| CX_SDIN Setup Time Before CX_SCLK Rising Edge                      | t <sub>ds</sub>   | 10    | -   | -         | ns     |

| CX_SDIN Hold Time After CX_SCLK Rising Edge                        | t <sub>dh</sub>   | 30    | -   | -         | ns     |

| CX_SCLK, SAI_SCLK High Time                                        | t <sub>sckh</sub> | 20    | -   | -         | ns     |

| CX_SCLK, SAI_SCLK Low Time                                         | t <sub>sckl</sub> | 20    | -   | -         | ns     |

| CX_SCLK, SAI_SCLK falling to CX_LRCK, SAI_LRCK Edge                | t <sub>lrck</sub> | -25   | -   | +25       | ns     |

#### Notes:

- 12. After powering-up the CS42516, RST should be held low after the power supplies and clocks are settled.

- 13. See Table 1 on page 25 for suggested OMCK frequencies

- 14. Limit the loading on RMCK to 1 CMOS load if operating above 24.576 MHz.

- 15. Not valid when RMCK\_DIV in "Clock Control (address 06h)" on page 52 is set to Multiply by 2.

- 16. 76.5 ns for Single-Speed and Double-Speed modes, 23 ns for Quad-Speed Mode.

Figure 2. Serial Audio Port Slave Mode Timing

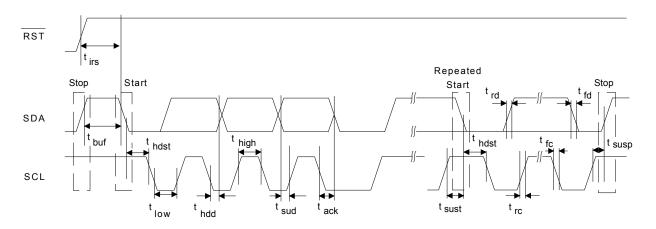

# SWITCHING CHARACTERISTICS - CONTROL PORT - I<sup>2</sup>C™ FORMAT

$(T_A$  = -10 to +70° C; VA=VARX = 5 V, VD =VLS= 3.3 V; VLC = 1.8 V to 5.25 V; Inputs: Logic 0 = DGND, Logic 1 = VLC,  $C_L$  = 30 pF)

| Parameter                                              | Symbol            | Min | Max       | Unit |

|--------------------------------------------------------|-------------------|-----|-----------|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | 100       | kHz  |

| RST Rising Edge to Start                               | t <sub>irs</sub>  | 500 | -         | ns   |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>  | 4.7 | -         | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 4.0 | -         | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 4.7 | -         | μs   |

| Clock High Time                                        | t <sub>high</sub> | 4.0 | -         | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 4.7 | -         | μs   |

| SDA Hold Time from SCL Falling (Note 17)               | t <sub>hdd</sub>  | 0   | -         | μs   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 250 | -         | ns   |

| Rise Time of SCL and SDA                               | t <sub>rc</sub>   | -   | 1         | μs   |

| Fall Time SCL and SDA                                  | t <sub>fc</sub>   | -   | 300       | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 4.7 | -         | μs   |

| Acknowledge Delay from SCL Falling (Note 18)           | t <sub>ack</sub>  | -   | (Note 19) | ns   |

#### Notes:

- 17. Data must be held for sufficient time to bridge the transition time,  $t_{fc}$ , of SCL.

- 18. The acknowledge delay is based on MCLK and can limit the maximum transaction speed.

- 19.  $\frac{15}{256 \times Fs}$  for Single-Speed Mode,  $\frac{15}{128 \times Fs}$  for Double-Speed Mode,  $\frac{15}{64 \times Fs}$  for Quad-Speed Mode

Figure 3. Control Port Timing - I<sup>2</sup>C Format

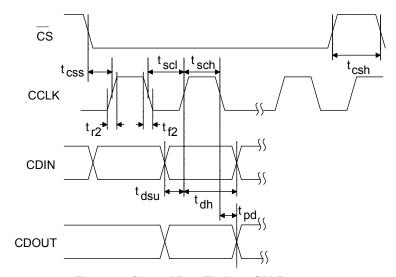

# SWITCHING CHARACTERISTICS - CONTROL PORT - SPI<sup>™</sup> FORMAT

$(T_A = -10 \text{ to } +70^{\circ} \text{ C}; VA=VARX = 5 \text{ V}, VD=VLS= 3.3 \text{ V}; VLC = 1.8 \text{ V to } 5.25 \text{ V}; Inputs: Logic 0 = DGND, Logic 1 = VLC, C_1 = 30 pF)$

| Parameter                               | Symbol           | Min | Тур | Max | Units |

|-----------------------------------------|------------------|-----|-----|-----|-------|

| CCLK Clock Frequency (Note 20)          | f <sub>sck</sub> | 0   | -   | 6.0 | MHz   |

| CS High Time Between Transmissions      | t <sub>csh</sub> | 1.0 | -   | -   | μS    |

| CS Falling to CCLK Edge                 | t <sub>css</sub> | 20  | -   | -   | ns    |

| CCLK Low Time                           | t <sub>scl</sub> | 66  | -   | -   | ns    |

| CCLK High Time                          | t <sub>sch</sub> | 66  | -   | -   | ns    |

| CDIN to CCLK Rising Setup Time          | t <sub>dsu</sub> | 40  | -   | -   | ns    |

| CCLK Rising to DATA Hold Time (Note 21) | t <sub>dh</sub>  | 15  | -   | -   | ns    |

| CCLK Falling to CDOUT Stable            | t <sub>pd</sub>  | -   | -   | 50  | ns    |

| Rise Time of CDOUT                      | t <sub>r1</sub>  | -   | -   | 25  | ns    |

| Fall Time of CDOUT                      | t <sub>f1</sub>  | -   | -   | 25  | ns    |

| Rise Time of CCLK and CDIN (Note 22)    | t <sub>r2</sub>  | -   | -   | 100 | ns    |

| Fall Time of CCLK and CDIN (Note 22)    | t <sub>f2</sub>  | -   | -   | 100 | ns    |

#### Notes:

- 20. If Fs is lower than 46.875 kHz, the maximum CCLK frequency should be less than 128 Fs. This is dictated by the timing requirements necessary to access the Channel Status and User Bit buffer memory. Access to the control register file can be carried out at the full 6 MHz rate. The minimum allowable input sample rate is 8 kHz, so choosing CCLK to be less than or equal to 1.024 MHz should be safe for all possible conditions.

- 21. Data must be held for sufficient time to bridge the transition time of CCLK.

- 22. For  $f_{sck}$  <1 MHz.

Figure 4. Control Port Timing - SPI Format

# DC ELECTRICAL CHARACTERISTICS

(T<sub>A</sub> = 25° C; AGND=DGND=0, all voltages with respect to ground; OMCK=12.288 MHz; Master Mode)

|                            | Parameter     |                              |                |   |      | Max | Units |

|----------------------------|---------------|------------------------------|----------------|---|------|-----|-------|

| Power Supply Current       | normal o      | peration, VA = VARX = 5 V    | I <sub>A</sub> | - | 75   | -   | mA    |

| (Note 23)                  |               | VD = 5 V                     | Ι <sub>D</sub> | - | 85   | -   | mA    |

|                            |               | VD = 3.3 V                   | I <sub>D</sub> | - | 51   | -   | mA    |

|                            | Interface of  | urrent, VLC=5 V (Note 24)    | ILC            | - | 250  | -   | μΑ    |

|                            |               | VLS=5 V                      | $I_{LS}$       | - | 13   | -   | mA    |

|                            | power-down st | ate (all supplies) (Note 25) | $I_{pd}$       | - | 250  | -   | μА    |

| Power Consumption          |               | (Note 23)                    |                |   |      |     |       |

| VA=VARX=5 V, VD=VLS=VI     | LC=3.3 V      | normal operation             |                | - | 587  | 650 | mW    |

|                            |               | power-down (Note 25)         |                | - | 1.25 | -   | mW    |

| VA=VARX=5 V, VD=VLS=VI     | LC=5 V        | normal operation             |                | - | 866  | 960 | mW    |

|                            |               | power-down (Note 25)         |                | - | 1.25 | -   | mW    |

| Power Supply Rejection Rat | tio (Note 26) | (1 kHz)                      | PSRR           | - | 60   | -   | dB    |

|                            |               | (60 Hz)                      | PSKK           | - | 40   | -   | dB    |

| VQ Nominal Voltage         |               |                              |                | - | 2.7  | -   | V     |

| VQ Output Impedance        |               |                              |                | - | 50   | -   | kΩ    |

| VQ Maximum allowable DC    | current       |                              |                | - | 0.01 | -   | mA    |

| FILT+ Nominal Voltage      |               |                              |                | - | 5.0  | -   | V     |

| FILT+ Output Impedance     |               |                              |                | - | 35   | -   | kΩ    |

| FILT+ Maximum allowable D  | OC current    |                              |                | - | 0.01 | -   | mA    |

#### Notes:

- 23. Current consumption increases with increasing FS and increasing OMCK. Max values are based on highest FS and highest OMCK. Variance between speed modes is negligible.

- 24. I<sub>LC</sub> measured with no external loading on the SDA pin.

- 25. Power-Down Mode is defined as  $\overline{RST}$  pin = Low with all clock and data lines held static.

- 26. Valid with the recommended capacitor values on FILT+ and VQ as shown in Figure 5.

# **DIGITAL INTERFACE CHARACTERISTICS**

$(T_A = +25^{\circ} C)$

| Parameters (Note 27)                                | Symbol               | Min             | Тур     | Max | Units   |      |

|-----------------------------------------------------|----------------------|-----------------|---------|-----|---------|------|

| High-Level Input Voltage                            | Serial Port          | $V_{IH}$        | 0.7xVLS | -   | -       | V    |

|                                                     | Control Port         |                 | 0.7xVLC | -   | -       | V    |

| Low-Level Input Voltage                             | Serial Port          | $V_{IL}$        | -       | -   | 0.2xVLS | V    |

|                                                     | Control Port         |                 | -       | -   | 0.2xVLC | V    |

| High-Level Output Voltage at I <sub>o</sub> =2 mA   | (Note 28)Serial Port | $V_{OH}$        | VLS-1.0 | -   | -       | V    |

|                                                     | Control Port         |                 | VLC-1.0 | -   | -       | V    |

|                                                     | MUTEC, GPOx          |                 | VA-1.0  | -   | -       | V    |

|                                                     | TXP                  |                 | VD-1.0  | -   | -       | V    |

| Low-Level Output Voltage at I <sub>o</sub> =2 mA    | (Note 28)            | $V_{OL}$        |         |     |         |      |

| Serial Port, Control Port, MUTEC, GPOx,TXP          |                      |                 | -       | -   | 0.4     | V    |

| High-Level Output Voltage at I <sub>o</sub> =100 μA | (Note 28)Serial Port | $V_{OH}$        | 0.8xVLS | -   | -       | V    |

|                                                     | Control Port         |                 | 0.8xVLC | -   | -       | V    |

|                                                     | MUTEC, GPOx          |                 | 0.8xVA  | -   | -       | V    |

|                                                     | TXP                  |                 | 0.8xVD  | -   | -       | V    |

| Low-Level Output Voltage at I <sub>o</sub> =100 μA  | (Note 28)Serial Port | $V_{OL}$        | -       | -   | 0.2xVLS | V    |

|                                                     | Control Port         |                 | -       | -   | 0.2xVLC | V    |

|                                                     | MUTEC, GPOx          |                 | -       | -   | 0.2xVA  | V    |

|                                                     | TXP                  |                 | -       | ı   | 0.2xVD  | V    |

| Input Sensitivity, RXP[7:0]                         |                      | $V_{TH}$        | -       | 150 | 200     | mVpp |

| Input Leakage Current                               |                      | l <sub>in</sub> | -       | -   | ±10     | μА   |

| Input Capacitance                                   |                      |                 | -       | 8   | -       | pF   |

| MUTEC Drive Current                                 |                      |                 | -       | 3   | -       | mA   |

#### Notes:

27. Serial Port signals include: RMCK, OMCK, SAI\_SCLK, SAI\_LRCK, SAI\_SDOUT, CX\_SCLK, CX\_L-RCK, CX\_SDOUT, CX\_SDIN1-3, AD-CIN1/2 Control Port signals include: SCL/CCLK, SDA/CDOUT, AD0/CS, AD1/CDIN, INT, RST S/PDIF-GPO Interface signals include: RXP0, RXP/GPO[1:7]

28. When operating RMCK above 24.576 MHz, limit the loading on the signal to 1 CMOS load.

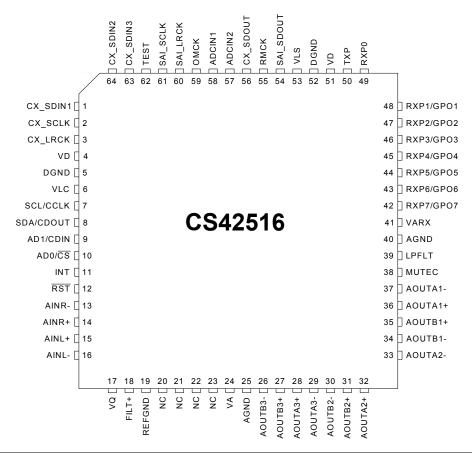

# 2. PIN DESCRIPTIONS

| Pin Name                         | #             | Pin Description                                                                                                                                                                                                                                                                                      |

|----------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CX_SDIN1<br>CX_SDIN2<br>CX_SDIN3 | 1<br>64<br>63 | Codec Serial Audio Data Input (Input) - Input for two's complement serial audio data.                                                                                                                                                                                                                |

| CX_SCLK                          | 2             | CODEC Serial Clock (Input/Output) - Serial clock for the CODEC serial audio interface.                                                                                                                                                                                                               |

| CX_LRCK                          | 3             | <b>CODEC Left Right Clock</b> ( <i>Input/Output</i> ) - Determines which channel, Left or Right, is currently active on the CODEC serial audio data line.                                                                                                                                            |

| VD                               | 4<br>51       | Digital Power (Input) - Positive power supply for the digital section.                                                                                                                                                                                                                               |

| DGND                             | 5<br>52       | Digital Ground (Input) - Ground reference. Should be connected to digital ground.                                                                                                                                                                                                                    |

| VLC                              | 6             | Control Port Power (Input) - Determines the required signal level for the control port.                                                                                                                                                                                                              |

| SCL/CCLK                         | 7             | <b>Serial Control Port Clock</b> ( <i>Input</i> ) - Serial clock for the serial control port. Requires an external pull-up resistor to the logic interface voltage in I <sup>2</sup> C mode as shown in the Typical Connection Diagram.                                                              |

| SDA/CDOUT                        | 8             | <b>Serial Control Data</b> ( <i>Input/Output</i> ) - SDA is a data I/O line in I <sup>2</sup> C mode and requires an external pull-up resistor to the logic interface voltage, as shown in the Typical Connection Diagram. CDOUT is the output data line for the control port interface in SPI mode. |

| AD1/CDIN                         | 9             | Address Bit 1 (I <sup>2</sup> C)/Serial Control Data (SPI) ( <i>Input</i> ) - AD1 is a chip address pin in I <sup>2</sup> C mode; CDIN is the input data line for the control port interface in SPI mode.                                                                                            |

| AD0/CS                           | 10            | Address Bit 0 (I <sup>2</sup> C)/Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I <sup>2</sup> C mode; $\overline{\text{CS}}$ is the chip select signal in SPI mode.                                                                                                          |

| INT                                                                              | 11                               | <b>Interrupt</b> ( <i>Output</i> ) - The CS42516 will generate an interrupt condition as per the Interrupt Mask register. See "Interrupts" on page 39 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST                                                                              | 12                               | Reset (Input) - The device enters a low power mode and all internal registers are reset to their default settings when low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AINR-<br>AINR+                                                                   | 13<br>14                         | <b>Differential Right Channel Analog Input</b> ( <i>Input</i> ) - Signals are presented differentially to the delta-sigma modulators via the AINR+/- pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AINL+                                                                            | 15                               | <b>Differential Left Channel Analog Input</b> ( <i>Input</i> ) - Signals are presented differentially to the delta-sigma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AINL-                                                                            | 16                               | modulators via the AINL+/- pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VQ                                                                               | 17                               | Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FILT+                                                                            | 18                               | <b>Positive Voltage Reference</b> ( <i>Output</i> ) - Positive reference voltage for the internal sampling circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REFGND                                                                           | 19                               | <b>Reference Ground</b> ( <i>Input</i> ) - Ground reference for the internal sampling circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC                                                                               | 20<br>21<br>22<br>23             | No Connect Pins - Do not make any connection to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AOUTA1 +,-<br>AOUTB1 +,-<br>AOUTA2 +,-<br>AOUTB2 +,-<br>AOUTA3 +,-<br>AOUTB3 +,- | 31,30<br>28,29<br>27,26          | <b>Differential Analog Output</b> ( <i>Output</i> ) - The full-scale differential analog output level is specified in the Analog Characteristics specification table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VA<br>VARX                                                                       | 24<br>41                         | Analog Power (Input) - Positive power supply for the analog section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AGND                                                                             | 25<br>40                         | Analog Ground (Input) - Ground reference. Should be connected to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MUTEC                                                                            | 38                               | <b>Mute Control</b> ( <i>Output</i> ) - The Mute Control pin outputs high impedance following an initial power-on condition or whenever the PDN bit is set to a '1', forcing the codec into power-down mode. The signal will remain in a high impedance state as long as the part is in power-down mode. The Mute Control pin goes to the selected "active" state during reset, muting, or if the master clock to left/right clock frequency ratio is incorrect. This pin is intended to be used as a control for external mute circuits to prevent the clicks and pops that can occur in any single supply system. The use of external mute circuits are not mandatory but may be desired for designs requiring the absolute minimum in extraneous clicks and pops. |

| LPFLT                                                                            | 39                               | PLL Loop Filter (Output) - An RC network should be connected between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RXP7/GPO7                                                                        | 42                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RXP6/GPO6<br>RXP5/GPO5<br>RXP4/GPO4<br>RXP3/GPO3<br>RXP2/GPO2<br>RXP1/GPO1       | 43<br>44<br>45<br>46<br>47<br>48 | <b>S/PDIF Receiver Input/ General Purpose Output</b> ( <i>Input/Output</i> ) - Receiver inputs for S/PDIF encoded data. The CS42516 has an internal 8:2 multiplexer to select the active receiver port, according to the Receiver Mode Control 2 register. These pins can also be configured as general purpose output pins, ADC Overflow indicators or Mute Control outputs according to the RXP/General Purpose Pin Control registers.                                                                                                                                                                                                                                                                                                                             |

| RXP0                                                                             | 49                               | S/PDIF Receiver Input (Input) - Dedicated receiver input for S/PDIF encoded data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TXP                                                                              | 50                               | <b>S/PDIF Transmitter Output</b> ( <i>Output</i> ) - S/PDIF encoded data output, mapped directly from one of the receiver inputs as indicated by the Receiver Mode Control 2 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VLS                                                                              | 53                               | Serial Port Interface Power (Input) - Determines the required signal level for the serial port interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |