Page 1

# **TCS3772**

# **Color Light-to-Digital Converter with Proximity Sensing**

## **General Description**

The TCS3772 device family provides red, green, blue, and clear (RGBC) light sensing and, when coupled with an external IR LED, proximity detection. These devices detect light intensity under a variety of lighting conditions and through a variety of attenuation materials, including dark glass. The proximity detection feature allows a large dynamic range of operation for accurate short distance detection, such as in a cell phone, for detecting when the user positions the phone close to their ear. An internal state machine provides the ability to put the device into a low power state in between proximity and RGBC measurements providing very low average power consumption.

The color sensing feature is useful in applications such as LED RGB backlight control, solid state lighting, reflected LED color sampler, or fluorescent light color temperature detection. With the addition of an IR blocking filter, the device is an excellent ambient light sensor, color temperature monitor, and general purpose color sensor.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of this device are listed below:

Figure 1: **Added Value of Using TCS3772**

| Benefits                                                                                 | Features                                                           |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Single Device Reduces Board Space                                                        | Integrated RGB and Clear Color Sensing and Proximity     Detection |

| Enables Flexible Operation for Wide<br>Range of Applications                             | Programmable Color Sensing and Proximity Detection                 |

| Enables Accurate Color and Ambient<br>Light Sensing Under Varying Lighting<br>Conditions | Integrated IR Blocking Filter                                      |

| Enables Operation within Wide Range of<br>Lighting Conditions                            | • 3.8M:1 Dynamic Range                                             |

- Color Light Sensing with IR-Blocking Filter

- Programmable Analog Gain and Integration Time

- 3 800 000:1 Dynamic Range

- Very High Sensitivity Ideally Suited for Operation Behind Dark Glass

- Proximity Detection

- Ambient Light Rejection

- Programmable Integration Time

- · Current Sink Driver for External IR LED

- Maskable Light and Proximity Interrupt

- Programmable Upper and Lower Thresholds with Persistence Filter

- Power Management

- Low Power 2.5-μA Sleep State

- 65-µA Wait State with Programmable Wait State Time from 2.4 ms to > 7 Seconds

- I<sup>2</sup>C Fast Mode Compatible Interface

- Data Rates up to 400 kbit/s

- Input Voltage Levels Compatible with V<sub>DD</sub> or 1.8 V Bus

- Register Set and Pin Compatible with the TCS3x71 Series

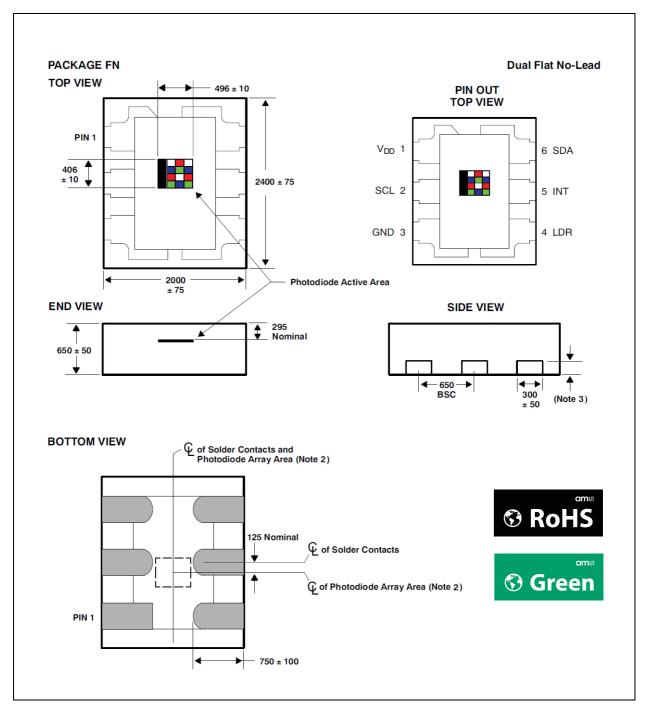

- Small 2 mm × 2.4 mm Dual Flat No-Lead (FN) Package

## **Applications**

The applications of TCS3772 include:

- RGB LED Backlight Control

- Ambient Light Color Temperature Sensing

- Cell Phone Touch Screen Disable

- Mechanical Switch Replacement

- Industrial Process Control

- Medical Diagnostics

## **End Products and Market Segments**

- HDTVs, Mobile Handsets, Tablets, and Portable Media Payers

- Medical and Commercial Instrumentation

- Toys

- Solid State and General Lighting

Page 2

Document Feedback

[v1-01] 2018-Mar-14

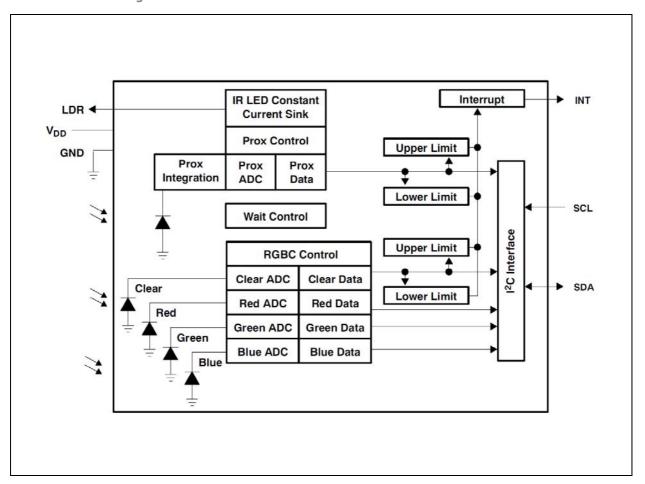

# **Block Diagram**

The functional blocks of this device are shown below:

Figure 2: Functional Block Diagram of TCS3772

ams Datasheet Page 3

[v1-01] 2018-Mar-14 Document Feedback

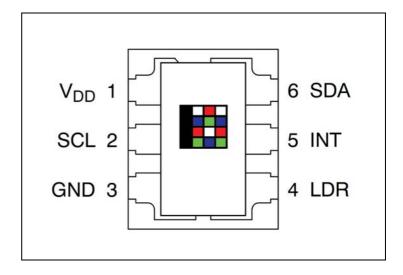

# **Pin Assignment**

The TCS3772 pin assignments are described below.

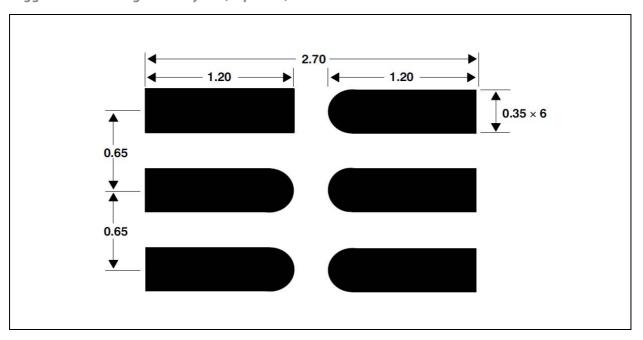

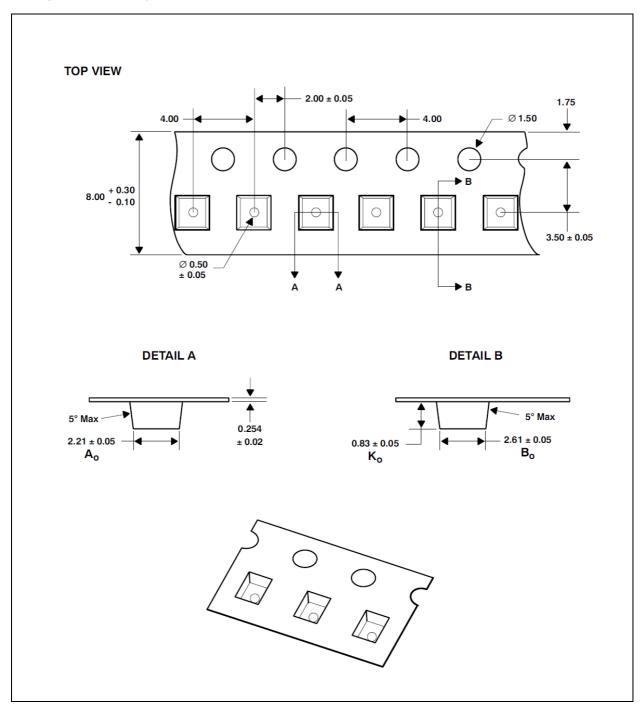

Figure 3: Pin Diagram

Package FN Dual Flat No-Lead (Top View):

Package drawing is not to scale.

Figure 4: Pin Description

| Pin Number | Pin Name        | Pin Type                                        | Description                                                                                   |

|------------|-----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 1          | V <sub>DD</sub> |                                                 | Supply voltage                                                                                |

| 2          | SCL             | Input                                           | I <sup>2</sup> C serial clock input terminal – clock signal for I <sup>2</sup> C serial data. |

| 3          | GND             |                                                 | Power supply ground. All voltages are referenced to GND.                                      |

| 4          | LDR             | Output                                          | LED driver for proximity emitter – open drain.                                                |

| 5          | INT             | INT Output Interrupt – open drain (active low). |                                                                                               |

| 6          | SDA             | Input/Output                                    | I <sup>2</sup> C serial data I/O terminal — serial data I/O for I <sup>2</sup> C.             |

Page 4ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings over Operating Free-Air Temperature Range (unless otherwise noted)

| Parameter                                    | Min  | Max  | Units | Comments                             |

|----------------------------------------------|------|------|-------|--------------------------------------|

| Supply voltage, V <sub>DD</sub>              |      | 3.8  | V     | All voltages are with respect to GND |

| Input terminal voltage                       | -0.5 | 3.8  | V     |                                      |

| Output terminal voltage (except LDR)         | -0.5 | 3.8  | V     |                                      |

| Output terminal voltage (LDR)                | -0.5 | 3.8  | V     |                                      |

| Output terminal current (except LDR)         | -1   | 20   | mA    |                                      |

| Storage temperature range, T <sub>STRG</sub> | -40  | 85   | °C    |                                      |

| ESD tolerance, human body model              | ±    | 2000 | V     |                                      |

ams Datasheet Page 5

[v1-01] 2018-Mar-14

Document Feedback

# **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Recommended Operating Conditions

| Symbol          | Parameter                      | Conditions                          | Min | Тур | Max | Units |

|-----------------|--------------------------------|-------------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> | Supply voltage                 | TCS37725 ( $I^2CV_{BUS} = V_{DD}$ ) | 2.7 | 3   | 3.6 | V     |

| - 00            | Supply voltage                 | TCS37727 ( $I^2CV_{BUS} = 1.8V$ )   | 2.7 | 3   | 3.3 | v     |

| T <sub>A</sub>  | Operating free-air temperature |                                     | -30 |     | 70  | ۰C    |

Figure 7: Operating Characteristics,  $V_{DD} = 3 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| Symbol            | Parameter                              | Conditions                                 | Min                 | Тур | Max                 | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------------------|----------------------------------------|--------------------------------------------|---------------------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                                        | Active – LDR pulses off                    |                     | 235 | 330                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| I <sub>DD</sub>   | Supply current                         | Wait state                                 |                     | 65  |                     | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                   |                                        | Sleep state - no I <sup>2</sup> C activity |                     | 2.5 | 10                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>OL</sub>   | INT SDA output low voltage             | 3 mA sink current                          | 0                   |     | 0.4                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| VOL               | in 3DA output low voltage              | 6 mA sink current                          | 0                   |     | 0.6                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| I <sub>LEAK</sub> | Leakage current, SDA, SCL,<br>INT pins |                                            | -5                  |     | 5                   | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                   | Leakage current, LDR pin               |                                            | -5                  |     | 5                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>IH</sub>   | SCL SDA input high voltage             | TCS37725                                   | 0.7 V <sub>DD</sub> |     |                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| - 10              | 3cL 3b/(iii)put iiigii voituge         | TCS37727                                   | 1.25                |     |                     | , and the second |  |

| V <sub>IL</sub>   | SCL SDA input low voltage              | TCS37725                                   |                     |     | 0.3 V <sub>DD</sub> | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| VIL               | SCL SDA Input low voltage              | TCS37727                                   |                     |     | 0.54                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

Page 6ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

Figure 8: Optical Characteristics, V<sub>DD</sub> = 3 V, T<sub>A</sub> = 25°C, AGAIN = 16×, ATIME = 0xF6 (unless otherwise noted)<sup>(1)</sup>

| Parameter Test Conditions  |                                      |     | ed<br>innel |     | een<br>innel |     | ue<br>nnel | Clea | ar Cha | nnel | Unit                    |

|----------------------------|--------------------------------------|-----|-------------|-----|--------------|-----|------------|------|--------|------|-------------------------|

|                            | Conditions                           | Min | Max         | Min | Max          | Min | Max        | Min  | Тур    | Max  |                         |

| R <sub>e</sub>             | $\lambda_{D} = 465 \text{ nm}^{(2)}$ | 0%  | 15%         | 10% | 42%          | 65% | 88%        | 11.0 | 13.8   | 16.6 | counts                  |

| lrradiance<br>responsivity | $\lambda_{D} = 525 \text{ nm}^{(3)}$ | 4%  | 25%         | 60% | 85%          | 10% | 45%        | 13.2 | 16.6   | 20.0 | /μW<br>/cm <sup>2</sup> |

| responsivity               | $\lambda_{D} = 615 \text{ nm}^{(4)}$ | 80% | 110%        | 0%  | 14%          | 5%  | 24%        | 15.6 | 19.5   | 23.4 | /СП                     |

- 1. The percentage shown represents the ratio of the respective red, green, or blue channel value to the clear channel value.

- 2. The 465 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$ =465nm, spectral halfwidth  $\Delta\lambda$ ½ = 22 nm.

- 3. The 525 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$ =525nm, spectral halfwidth  $\Delta\lambda \frac{1}{2}$  = 35 nm.

- 4. The 615 nm input irradiance is supplied by a AlInGaP light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$ =615nm, spectral halfwidth  $\Delta\lambda 1/2$  = 15 nm.

Figure 9: RGBC Characteristics,  $V_{DD} = 3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , AGAIN =  $16 \times$ , AEN = 1 (unless otherwise noted)

| Parameter                                 | Conditions                                                          | Min  | Тур | Max   | Units  |

|-------------------------------------------|---------------------------------------------------------------------|------|-----|-------|--------|

| Dark ADC count value                      | $E_e = 0$ , AGAIN = $60 \times$ ,<br>ATIME = $0 \times D6$ (100 ms) | 0    | 1   | 5     | counts |

| ADC integration time step size            | ATIME=0xFF                                                          | 2.27 | 2.4 | 2.56  | ms     |

| ADC number of integration steps (1)       |                                                                     | 1    |     | 256   | steps  |

| ADC counts per step (1)                   |                                                                     | 0    |     | 1024  | counts |

| ADC count value (1)                       | ATIME=0xC0 (153.6 ms)                                               | 0    |     | 65535 | counts |

|                                           | 4×                                                                  | 3.8  | 4   | 4.2   |        |

| Gain scaling, relative to 1× gain setting | 16×                                                                 | 15   | 16  | 16.8  | ×      |

|                                           | 60×                                                                 | 58   | 60  | 63    |        |

#### Note(s):

1. Parameter ensured by design and is not tested.

ams Datasheet Page 7

[v1-01] 2018-Mar-14 Document Feedback

Figure 10: Proximity Characteristics,  $V_{DD} = 3 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ , PEN = 1 (unless otherwise noted)

| Parameter                              | Conditio                                                                                                                                                        | ns         | Min   | Тур   | Max                               | Units  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-------|-----------------------------------|--------|

| I <sub>DD</sub><br>Supply current      | LDR pulse on                                                                                                                                                    |            |       | 3     |                                   | mA     |

| ADC conversion time step size          | PTIME = 0xFF                                                                                                                                                    |            | 2.27  | 2.4   | 2.56                              | ms     |

| ADC number of integration steps (1)    |                                                                                                                                                                 |            | 1     |       | 256                               | steps  |

| ADC counts per step (1)                | PTIME = 0xFF                                                                                                                                                    |            | 0     |       | 1023                              | counts |

| ADC count value                        | $\lambda_p = 850 \text{ nm}, E_e = 770.$<br>PTIME = 0xFB, PPULSE                                                                                                | 1350       |       | 1900  | counts                            |        |

| ADC output responsivity                | $\lambda_p = 850 \text{ nm, PTIME} = 0$ $PPULSE = 1^{(3)}$                                                                                                      | 0.175      | 0.211 | 0.247 | counts/<br>μW/<br>cm <sup>2</sup> |        |

| Noise (1) (2) (3)                      | $E_e = 0$ , PTIME = 0xFF, P                                                                                                                                     |            | 2     |       | % FS                              |        |

| LED pulse count (1)                    |                                                                                                                                                                 |            | 0     |       | 255                               | pulses |

| LED pulse period                       |                                                                                                                                                                 |            |       | 14.0  |                                   | μs     |

| LED pulse width – LED on time          |                                                                                                                                                                 |            |       | 6.3   |                                   | μs     |

|                                        |                                                                                                                                                                 | PDRIVE = 0 | 80    | 106   | 132                               | mA     |

| LED drive current                      | I <sub>SINK</sub> sink current @                                                                                                                                | PDRIVE = 1 |       | 50    |                                   |        |

| LED drive current                      | 1.6 V, LDR pin                                                                                                                                                  | PDRIVE = 2 |       | 25    |                                   |        |

|                                        |                                                                                                                                                                 | PDRIVE = 3 |       | 12.5  |                                   |        |

| Maximum operating distance (1) (4) (5) | PDRIVE = 0 (100 mA), P Emitter: λ <sub>p</sub> = 850 nm, and 60 mW/sr Object: 16 × 20-inch, 9 Kodak Gray Card (white Optics: Open view (no optical attenuation) |            | 30    |       | inches                            |        |

- 1. Parameter is ensured by design or characterization and is not tested.

- 2. Proximity noise is defined as one standard deviation of 600 samples.

- 3. Proximity noise typically increases as  $\sqrt{\text{PPULSE}}$

- 4. Greater operating distances are achievable with appropriate optical system design considerations. See available **ams** application notes for additional information.

- 5. Maximum operating distance is dependent upon emitter and the reflective properties of the object's surface.

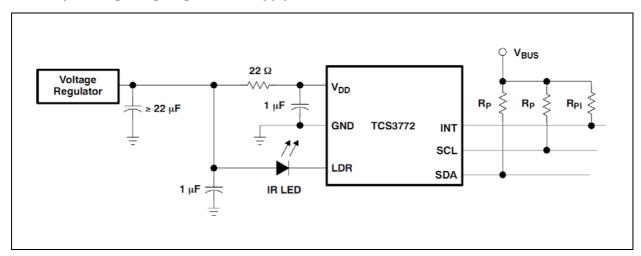

- 6. Proximity noise test was done using the Figure 11, "Proximity Noise Test Circuit," on page 9.

Page 8ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

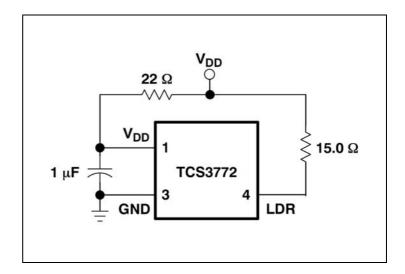

Figure 11: Proximity Noise Test Circuit

Figure 12: Wait Characteristics,  $V_{DD}$  = 3 V,  $T_A$  = 25°C, WEN = 1 (unless otherwise noted)

| Parameter                | Conditions   | Channel | Min  | Тур | Max  | Units |

|--------------------------|--------------|---------|------|-----|------|-------|

| Wait step size           | WTIME = 0xFF |         | 2.27 | 2.4 | 2.56 | ms    |

| Wait number of steps (1) |              |         | 1    |     | 256  | steps |

1. Parameter ensured by design and is not tested.

ams Datasheet Page 9

[v1-01] 2018-Mar-14 Document Feedback

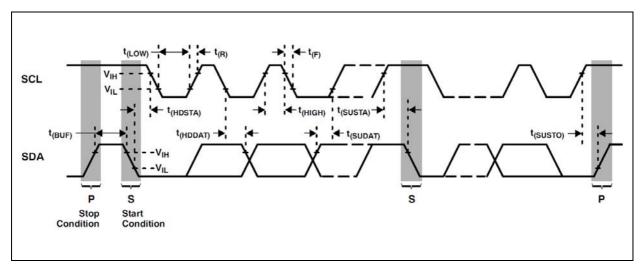

# **Timing Characteristics**

The timing characteristics of TCS3772 are given below.

Figure 13: AC Electrical Characteristics,  $V_{DD} = 3 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| Parameter <sup>(1)</sup> | Description                                                                                  | Min | Max | Units |

|--------------------------|----------------------------------------------------------------------------------------------|-----|-----|-------|

| f <sub>(SCL)</sub>       | Clock frequency (I <sup>2</sup> C only)                                                      | 0   | 400 | kHz   |

| t <sub>(BUF)</sub>       | Bus free time between start and stop condition                                               | 1.3 |     | μs    |

| t <sub>(HDSTA)</sub>     | Hold time after (repeated) start condition. After this period, the first clock is generated. | 0.6 |     | μs    |

| t <sub>(SUSTA)</sub>     | Repeated start condition setup time                                                          | 0.6 |     | μs    |

| t <sub>(SUSTO)</sub>     | Stop condition setup time                                                                    |     |     | μs    |

| t <sub>(HDDAT)</sub>     | Data hold time                                                                               | 0   |     | μs    |

| t <sub>(SUDAT)</sub>     | Data setup time                                                                              | 100 |     | ns    |

| t <sub>(LOW)</sub>       | SCL clock low period                                                                         | 1.3 |     | μs    |

| t <sub>(HIGH)</sub>      | SCL clock high period                                                                        | 0.6 |     | μs    |

| t <sub>F</sub>           | Clock/data fall time                                                                         |     | 300 | ns    |

| t <sub>R</sub>           | Clock/data rise time                                                                         |     | 300 | ns    |

| C <sub>i</sub>           | Input pin capacitance                                                                        |     | 10  | pF    |

### Note(s):

1. Specified by design and characterization; not production tested.

# **Timing Diagrams**

Figure 14:

Parameter Measurement Information

Page 10ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# Typical Operating Characteristics

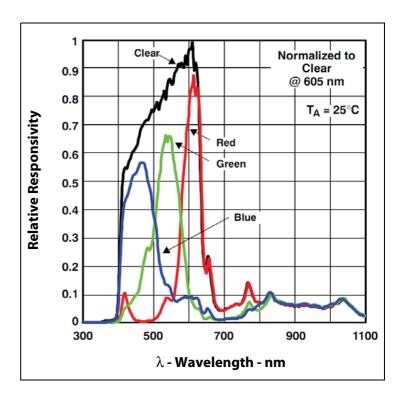

Figure 15:

Photodiode Spectral Responsivity RGBC

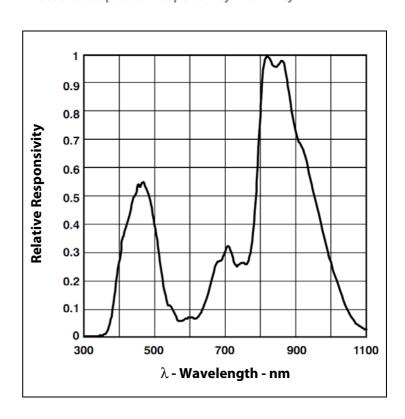

Figure 16:

Photodiode Spectral Responsivity Proximity

ams Datasheet Page 11

[v1-01] 2018-Mar-14 Document Feedback

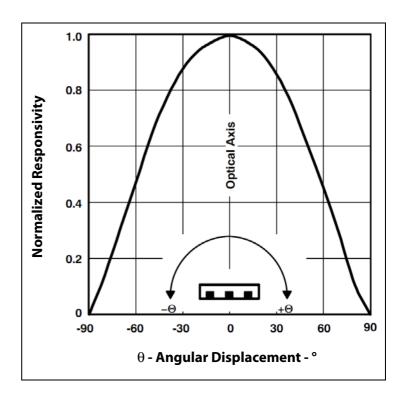

Figure 17: Normalized Responsivity vs. Angular Displacement

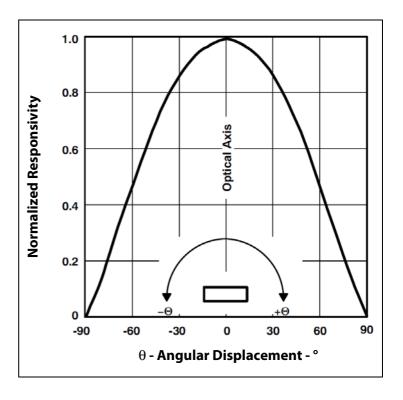

Figure 18: Normalized Responsivity vs. Angular Displacement

Page 12ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

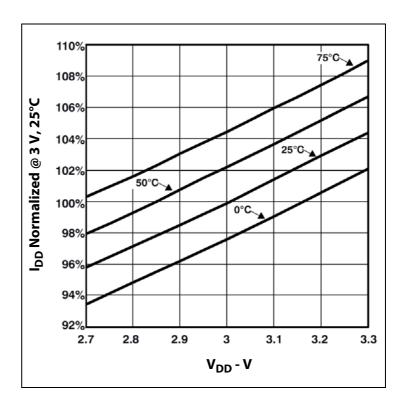

Figure 19: Normalized  $I_{DD}$  vs.  $V_{DD}$  and Temperature

Figure 20: Typical LDR Current vs. Voltage

ams Datasheet Page 13

[v1-01] 2018-Mar-14 Document Feedback

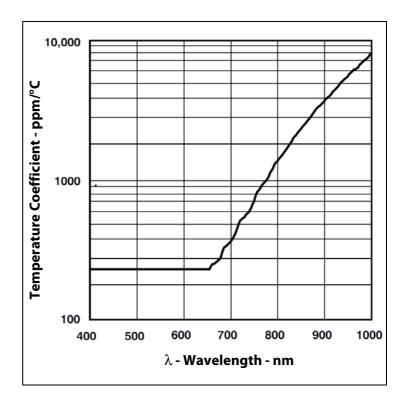

Figure 21: Responsivity Temperature Coefficient

Page 14ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

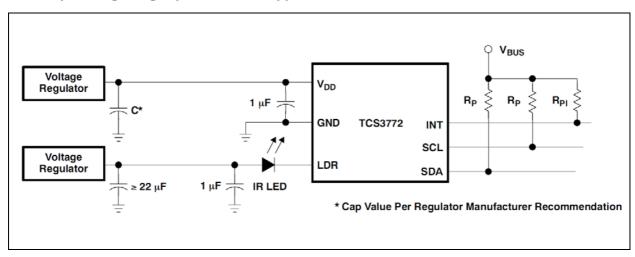

## **Detailed Description**

The TCS3772 is a next-generation digital color light sensor device containing four integrating analog-to-digital converters (ADCs) that integrate currents from photodiodes. The device contains a 3 × 4 photodiode array used for color measurements and a 1 × 4 photodiode array used for proximity measurements. Integration of all color sensing channels occurs simultaneously. Upon completion of the conversion cycle, the conversion result is transferred to the corresponding data registers. The transfers are double-buffered to ensure that the integrity of the data is maintained. Communication with the device is accomplished through a fast (up to 400 kHz), two-wire I<sup>2</sup>C serial bus for easy connection to a microcontroller or embedded controller.

The device provides a separate pin for level-style interrupts. The interrupt feature simplifies and improves system efficiency by eliminating the need to poll a sensor for a light intensity value. When interrupts are enabled, an interrupt is generated when the value of a clear channel or proximity conversion is greater than an upper threshold or less than a lower threshold. Once the interrupt is asserted, it remains asserted until cleared by the controlling firmware. In addition, a programmable interrupt persistence filter allows the user to set the number of consecutive clear channel or proximity conversions outside of the threshold region that are necessary to trigger an interrupt. Interrupt thresholds and persistence filter settings are configured independently for both clear and proximity.

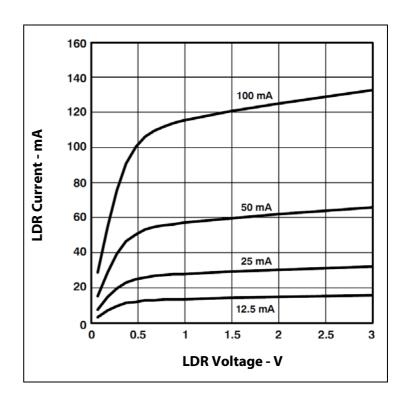

Proximity detection requires only a single external IR LED. An internal LED driver can be configured to provide a constant current sink of 12.5 mA, 25 mA, 50 mA, or 100 mA of current. No external current limiting resistor is required. The number of proximity LED pulses can be programmed from 1 to 255 pulses. Each pulse has a 14- $\mu$ s period.

ams Datasheet Page 15

[v1-01] 2018-Mar-14 Document Feedback

# **Principles of Operation**

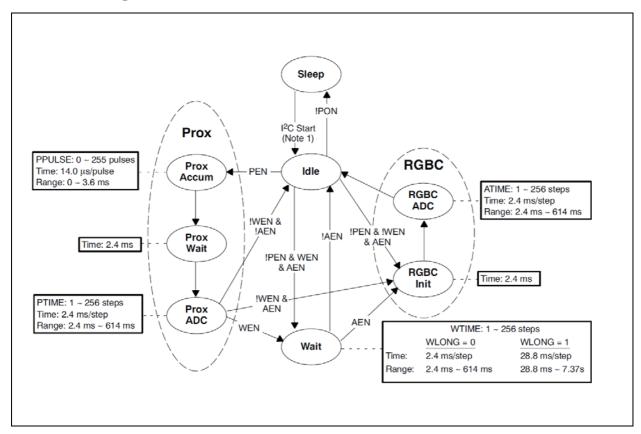

## **System State Machine**

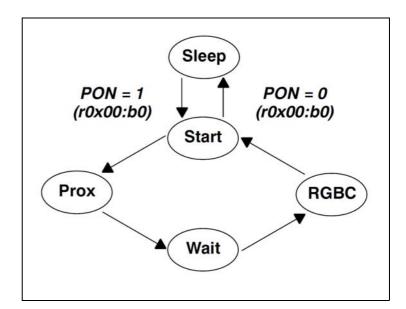

The TCS3772 provides control of RGBC, proximity detection, and power management functionality through an internal state machine (Figure 22). After a power-on-reset, the device is in the sleep mode. As soon as the PON bit is set, the device will move to the start state. It will then continue through the Prox, Wait, and RGBC states. If these states are enabled, the device will execute each function. If the PON bit is set to 0, the state machine will continue until all conversions are completed and then go into a low power sleep mode.

Figure 22: Simplified State Diagram

**Note(s):** In this document, the nomenclature uses the bit field name in italics followed by the register number and bit number to allow the user to easily identify the register and bit that controls the function. For example, the power on (PON) is in register 0, bit 0. This is represented as PON (r0x00:b0).

Page 16

Document Feedback

[v1-01] 2018-Mar-14

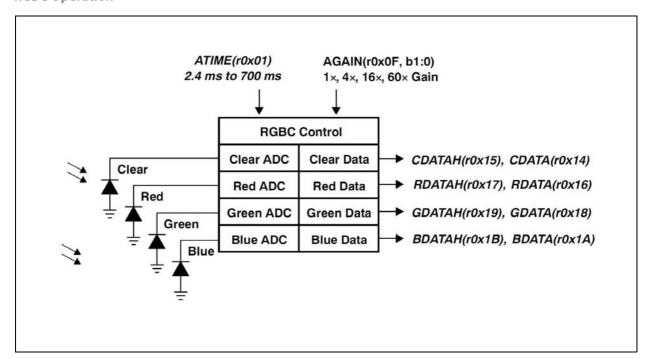

## **RGBC Operation**

The RGBC engine contains RGBC gain control (AGAIN) and four integrating analog-to-digital converters (ADC) for the RGBC photodiodes. The RGBC integration time (ATIME) impacts both the resolution and the sensitivity of the RGBC reading. Integration of all four channels occurs simultaneously and upon completion of the conversion cycle, the results are transferred to the color data registers. This data is also referred to as channel count. The transfers are double-buffered to ensure that invalid data is not read during the transfer. After the transfer, the device automatically moves to the next state in accordance with the configured state machine.

Figure 23: RGBC Operation

The registers for programming the integration and wait times are a 2's compliment values. The actual time can be calculated as follows:

ATIME = 256 - Integration Time / 2.4 ms

Inversely, the time can be calculated from the register value as follows:

Integration Time =  $2.4 \text{ ms} \times (256 - \text{ATIME})$

For example, if a 100-ms integration time is needed, the device needs to be programmed to:

$$256 - (100 / 2.4) = 256 - 42 = 214 = 0 \times D6$$

Conversely, the programmed value of 0xC0 would correspond to:

$$(256 - 0xC0) \times 2.4 = 64 \times 2.4 = 154 \text{ ms}$$

ams Datasheet Page 17

[v1-01] 2018-Mar-14 Document Feedback

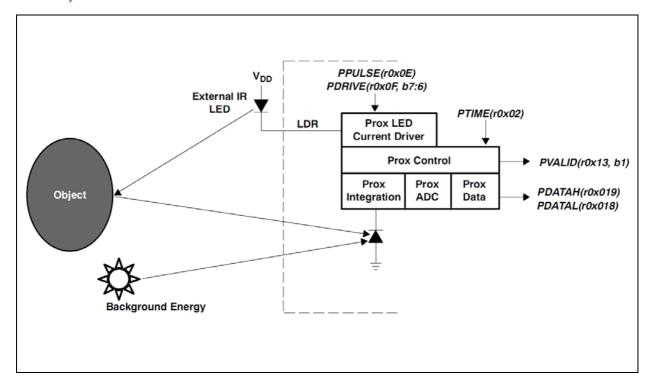

## **Proximity Detection**

Proximity detection is accomplished by measuring the amount of light energy, generally from an IR LED, reflected off an object to determine its distance. The proximity light source, which is external to the TCS3772 device, is driven by the integrated proximity LED current driver.

Figure 24: Proximity Detection

The LED current driver, output on the LDR terminal, provides a regulated current sink that eliminates the need for an external current limiting resistor. PDRIVE sets the drive current to 100 mA, 50 mA, 25 mA. To drive an external light source with more than 100 mA or to minimize on-chip ground bounce, LDR can be used to drive an external p-type transistor, which, in turn, drives the light source.

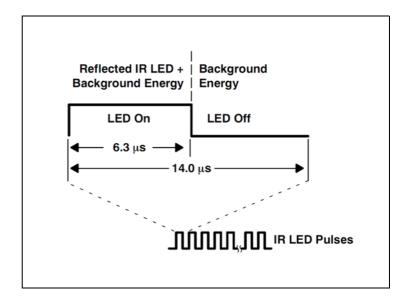

Referring to the Detailed State Machine figure, the LED current driver pulses the external IR LED as shown in Figure 25 during the Prox Accum state. Figure 25 also illustrates that the LED On pulse has a fixed width of 6.3  $\mu s$  and period of 14.0  $\mu s$ . So, in addition to setting the proximity drive current, 1 to 255 proximity pulses (PPULSE) can be programmed. When deciding on the number of proximity pulses, keep in mind that the signal increases proportionally to PPULSE, while noise increases by the square root of PPULSE.

Page 18

Document Feedback

[v1-01] 2018-Mar-14

Figure 25:

Proximity LED Current Driver Waveform

Figure 24 illustrates light rays emitting from an external IR LED, reflecting off an object, and being absorbed by the proximity photodiode.

Referring again to Figure 25, the reflected IR LED and the background energy is integrated during the LED On time, then during the LED Off time, the integrated background energy is subtracted from the LED On time energy, leaving the external IR LED energy to accumulate from pulse to pulse.

After the programmed number of proximity pulses have been generated, the proximity ADC converts and scales the proximity measurement to a 16-bit value, then stores the result in two 8-bit proximity data (PDATAx) registers. ADC scaling is controlled by the proximity ADC conversion time (PTIME) which is programmable from 1 to 256 2.4-ms time units. However, depending on the application, scaling the proximity data will equally scale any accumulated noise. Therefore, in general, it is recommended to leave PTIME at the default value of one 2.4-ms ADC conversion time (0xFF).

Once the first proximity cycle has completed, the proximity valid (PVALID) bit in the Status register will be set and remain set until the proximity detection function is disabled (PEN).

For additional information on using the proximity detection function behind glass and for optical system design guidance, please see available **ams** application notes.

ams Datasheet Page 19

[v1-01] 2018-Mar-14 Document Feedback

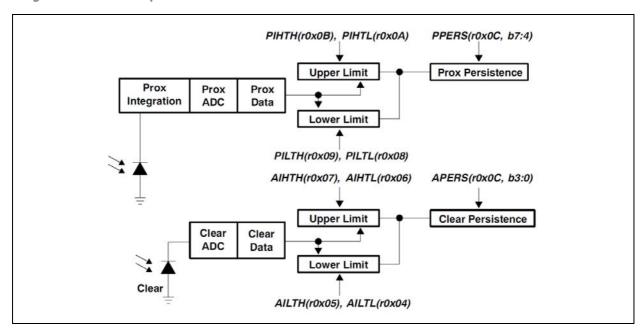

## Interrupts

The interrupt feature simplifies and improves system efficiency by eliminating the need to poll the sensor for light intensity or proximity values outside of a user-defined range. While the interrupt function is always enabled and it's status is available in the status register (0x13), the output of the interrupt state can be enabled using the proximity interrupt enable (PIEN) or Clear interrupt enable (AIEN) fields in the enable register (0x00).

Four 16-bit interrupt threshold registers allow the user to set limits below and above a desired light level and proximity range. An interrupt can be generated when the Clear data (CDATA) is less than the Clear interrupt low threshold registers (AILTx) or greater than the Clear interrupt high threshold registers (AIHTx). Likewise, an out-of-range proximity interrupt can be generated when the proximity data (PDATA) falls below the proximity interrupt low threshold (PILTx) or exceeds the proximity interrupt high threshold (PIHTx).

It is important to note that the thresholds are evaluated in sequence, first the low threshold, then the high threshold. As a result, if the low threshold is set above the high threshold, the high threshold is ignored and only the low threshold is evaluated.

To further control when an interrupt occurs, the device provides a persistence filter. The persistence filter allows the user to specify the number of consecutive out-of-range Clear or proximity occurrences before an interrupt is generated. The persistence register (0x0C) allows the user to set the Clear persistence (APERS) and the proximity persistence (PPERS) values. See the persistence register for details on the persistence filter values. Once the persistence filter generates an interrupt, it will continue until a special function interrupt clear command is received (see command register).

Figure 26: Programmable Interrupt

Page 20ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

## **System Timing**

The system state machine shown in Figure 22 provides an overview of the states and state transitions that provide system control of the device. This section highlights the programmable features, which affect the state machine cycle time, and provides details to determine system level timing.

When the proximity detection feature is enabled (PEN), the state machine transitions through the Prox Accum, Prox Wait, and Prox ADC states. The Prox Wait time is a fixed 2.4ms, whereas the Prox Accum time is determined by the number of proximity LED pulses (PPULSE) and the Prox ADC time is determined by the integration time (PTIME). The formulas to determine the Prox Accum and Prox ADC times are given in the associated boxes in Figure 27. If an interrupt is generated as a result of the proximity cycle, it will be asserted at the end of the Prox ADC state.

When the power management feature is enabled (WEN), the state machine will transition in turn to the Wait state. The wait time is determined by WLONG, which extends normal operation by 12× when asserted, and WTIME. The formula to determine the wait time is given in the box associated with the Wait state in Figure 27.

When the RGBC feature is enabled (AEN), the state machine will transition through the RGBC Init and RGBC ADC states. The RGBC Init state takes 2.4 ms, while the RGBC ADC time is dependent on the integration time (ATIME). The formula to determine RGBC ADC time is given in the associated box in Figure 27. If an interrupt is generated as a result of the RGBC cycle, it will be asserted at the end of the RGBC ADC.

ams Datasheet Page 21 **Document Feedback**

Figure 27: Detailed State Diagram

- 1. There is a 2.4 ms warm-up delay if PON is enabled. If PON is not enabled, the device will return to the Sleep state as shown.

- 2. PON, PEN, WEN, and AEN are fields in the Enable register (0x00).

Page 22ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# **Power Management**

Power consumption can be managed with the Wait state, because the Wait state typically consumes only 65  $\mu A$  of  $I_{DD}$ current. An example of the power management feature is given below. With the assumptions provided in the example, average  $I_{DD}$  is estimated to be 186  $\mu A$ .

Figure 28: **Power Management**

| System State<br>Machine State | Programmable<br>Parameter | Programmed<br>Value | Duration                | Typical<br>Current |

|-------------------------------|---------------------------|---------------------|-------------------------|--------------------|

| Prox Accum                    | PPULSE                    | 0x04                | 0.056 ms                |                    |

| Prox Accum - LED ON           |                           |                     | 0.025 ms <sup>(1)</sup> | 109 mA             |

| Prox Accum - LED OFF          |                           |                     | 0.031 ms <sup>(2)</sup> | 0.235 mA           |

| Prox Wait                     |                           |                     | 2.40 ms                 | 0.235 mA           |

| Prox ADC                      | PTIME                     | 0xFF                | 2.40 ms                 | 0.235 mA           |

| Wait                          | WTIME                     | 0xEE                | 43.1 ms                 | 0.065 mA           |

| vvait                         | WLONG                     | 0                   | 73.11113                | 0.005111A          |

| ALS Init                      |                           |                     | 2.40 ms                 | 0.235 mA           |

| ALS ADC                       | ATIME                     | 0xEE                | 43.1 ms                 | 0.235 mA           |

- 1. Prox Accum LED ON time = 6.3  $\mu$ s per pulse  $\times$  4 pulses = 25.2  $\mu$ s = 0.025 ms

- 2. Prox Accum LED OFF time = 7.7  $\mu$ s per pulse  $\times$  4 pulses = 30.9  $\mu$ s = 0.031 ms  $Average\ I_{DD}\ Current = ((0.025\times109) + (0.031\times0.235) + (2.40\times0.235) + (43.1\times0.065) + (43.1\times0.263) + (2.40\times0.235\times2)) /\ 93\approx186\ \mu A$

Keeping with the same programmed values as the example, Figure 29 shows how the average I<sub>DD</sub> current is affected by the Wait state time, which is determined by WEN, WTIME, and WLONG. Note that the worst-case current occurs when the Wait state is not enabled.

Figure 29: Average I<sub>DD</sub> Current

| WEN | WTIME | WLONG | WAIT State | Average I <sub>DD</sub> Current |

|-----|-------|-------|------------|---------------------------------|

| 0   | n/a   | n/a   | 0 ms       | 289 μΑ                          |

| 1   | 0xFF  | 0     | 2.40 ms    | 279 μΑ                          |

| 1   | 0xEE  | 0     | 43.1 ms    | 186 μΑ                          |

| 1   | 0x00  | 0     | 613 ms     | 82 μΑ                           |

| 1   | 0x00  | 1     | 7.36 s     | 67 μΑ                           |

ams Datasheet Page 23 **Document Feedback**

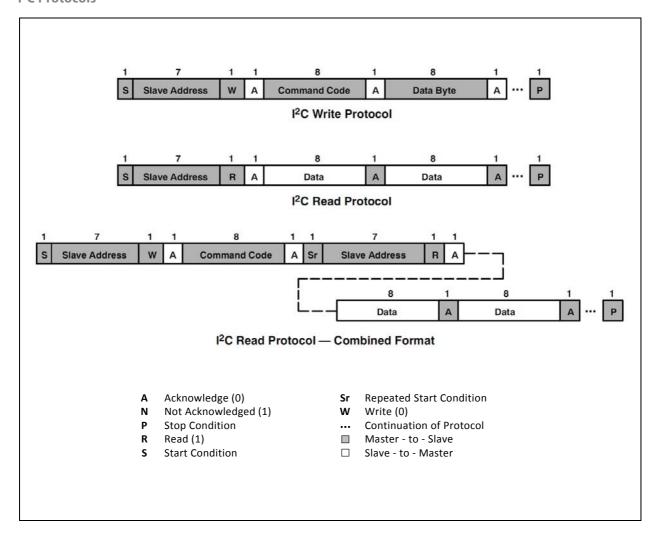

## I<sup>2</sup>C Protocol

Interface and control are accomplished through an I<sup>2</sup>C serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The devices support the 7-bit I<sup>2</sup>C addressing protocol.

The I<sup>2</sup>C standard provides for three types of bus transaction: read, write, and a combined protocol (Figure 30). During a write operation, the first byte written is a command byte followed by data. In a combined protocol, the first byte written is the command byte followed by reading a series of bytes. If a read command is issued, the register address from the previous command will be used for data access. Likewise, if the MSB of the command is not set, the device will write a series of bytes at the address stored in the last valid command with a register address. The command byte contains either control information or a 5-bit register address. The control commands can also be used to clear interrupts.

The I<sup>2</sup>C bus protocol was developed by Philips (now NXP). For a complete description of the I<sup>2</sup>C protocol, please review the NXP I<sup>2</sup>C design specification at:

http://www.i2c-bus.org/references/.

Figure 30: I<sup>2</sup>C Protocols

Page 24ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# **Register Description**

The TCS3772 is controlled and monitored by data registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions. The register set is summarized in Figure 31.

Figure 31: Register Set

| Address | Register Name | R/W | Register Function                            | Reset Value |

|---------|---------------|-----|----------------------------------------------|-------------|

|         | COMMAND       | W   | Specifies register address                   | 0x00        |

| 0x00    | ENABLE        | R/W | Enables states and interrupts                | 0x00        |

| 0x01    | ATIME         | R/W | RGBC time                                    | 0xFF        |

| 0x02    | PTIME         | R/W | Proximity time                               | 0xFF        |

| 0x03    | WTIME         | R/W | Wait time                                    | 0xFF        |

| 0x04    | AILTL         | R/W | Clear interrupt low threshold low byte       | 0x00        |

| 0x05    | AILTH         | R/W | Clear interrupt low threshold high byte      | 0x00        |

| 0x06    | AIHTL         | R/W | Clear interrupt high threshold low byte      | 0x00        |

| 0x07    | AIHTH         | R/W | Clear interrupt high threshold high byte     | 0x00        |

| 0x08    | PILTL         | R/W | Proximity interrupt low threshold low byte   | 0x00        |

| 0x09    | PILTH         | R/W | Proximity interrupt low threshold high byte  | 0x00        |

| 0x0A    | PIHTL         | R/W | Proximity interrupt high threshold low byte  | 0x00        |

| 0x0B    | PIHTH         | R/W | Proximity interrupt high threshold high byte | 0x00        |

| 0x0C    | PERS          | R/W | Interrupt persistence filters                | 0x00        |

| 0x0D    | CONFIG        | R/W | Configuration                                | 0x00        |

| 0x0E    | PPULSE        | R/W | Proximity pulse count                        | 0x00        |

| 0x0F    | CONTROL       | R/W | Gain control register                        | 0x00        |

| 0x12    | ID            | R   | Device ID                                    | ID          |

| 0x13    | STATUS        | R   | Device status                                | 0x00        |

| 0x14    | CDATA         | R   | Clear ADC data low byte                      | 0x00        |

| 0x15    | CDATAH        | R   | Clear ADC data high byte                     | 0x00        |

| 0x16    | RDATA         | R   | Red ADC data low byte                        | 0x00        |

| 0x17    | RDATAH        | R   | Red ADC data high byte                       | 0x00        |

| 0x18    | GDATA         | R   | Green ADC data low byte                      | 0x00        |

| 0x19    | GDATAH        | R   | Green ADC data high byte                     | 0x00        |

| Address | Register Name | R/W | R/W Register Function        |      |

|---------|---------------|-----|------------------------------|------|

| 0x1A    | BDATA         | R   | Blue ADC data low byte       | 0x00 |

| 0x1B    | BDATAH        | R   | Blue ADC data high byte      | 0x00 |

| 0x1C    | PDATA         | R   | Proximity ADC data low byte  | 0x00 |

| 0x1D    | PDATAH        | R   | Proximity ADC data high byte | 0x00 |

The mechanics of accessing a specific register depends on the specific protocol used. See the section on I<sup>2</sup>C protocols on the previous pages. In general, the COMMAND register is written first to specify the specific control/status register for following read/write operations.

Page 26ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# **Command Register**

The COMMAND registers specifies the address of the target register for future write and read operations.

Figure 32: **Command Register**

| 7   | 6   | 5    | 4 | 3 | 2       | 1 | 0 |

|-----|-----|------|---|---|---------|---|---|

| CMD | TYI | ТҮРЕ |   |   | ADDR/SF |   |   |

| Field   | Bits | Description                           |                                                                                                                                                                                                                                                        |  |  |  |

|---------|------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CMD     | 7    | Select Commar                         | nd Register. Must write as 1 when addressing COMMAND register.                                                                                                                                                                                         |  |  |  |

|         |      | Selects type of                       | transaction to follow in subsequent data transfers:                                                                                                                                                                                                    |  |  |  |

|         |      | FIELD VALUE                           | INTEGRATION TIME                                                                                                                                                                                                                                       |  |  |  |

|         |      | 00                                    | Repeated byte protocol transaction                                                                                                                                                                                                                     |  |  |  |

| TYPE    | 6:5  | 01                                    | Auto-increment protocol transaction                                                                                                                                                                                                                    |  |  |  |

|         |      | 10                                    | Reserved – Do not use                                                                                                                                                                                                                                  |  |  |  |

|         |      | 11                                    | Special function – See description below                                                                                                                                                                                                               |  |  |  |

|         |      |                                       | vill repeatedly read the same register with each data access. Block ovide auto-increment function to read successive bytes.                                                                                                                            |  |  |  |

|         |      | above, this field<br>specific control | pecial function field. Depending on the transaction type, see<br>I either specifies a special function command or selects the<br>-status-register for following write and read transactions. The field<br>low apply only to special function commands: |  |  |  |

|         |      | FIELD VALUE                           | READ VALUE                                                                                                                                                                                                                                             |  |  |  |

| ADDR/SF | 4:0  | 00101                                 | Proximity interrupt clear                                                                                                                                                                                                                              |  |  |  |

| ADDIVSI | 4.0  | 00110                                 | Clear channel interrupt clear                                                                                                                                                                                                                          |  |  |  |

|         |      | 00111                                 | Proximity and Clear interrupt clear                                                                                                                                                                                                                    |  |  |  |

|         |      | Other                                 | Reserved – Do not write                                                                                                                                                                                                                                |  |  |  |

|         |      |                                       | oximity interrupt clear special functions clear any pending lare self clearing.                                                                                                                                                                        |  |  |  |

ams Datasheet Page 27 Document Feedback

# **Enable Register (0x00)**

The ENABLE register is used primarily to power the TCS3772 device on and off, and enable functions and interrupts as shown below.

Figure 33: Enable Register

| 7     | 6   | 5    | 4    | 3   | 2   | 1   | 0   |

|-------|-----|------|------|-----|-----|-----|-----|

| Reser | ved | PIEN | AIEN | WEN | PEN | AEN | PON |

| Fields   | Bits | Description                                                                                                                                                                                                                                                                                                                                       |  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reserved | 7:6  | Reserved. Write as 0.                                                                                                                                                                                                                                                                                                                             |  |

| PIEN     | 5    | Proximity interrupt enable. When asserted, permits proximity interrupts to be generated.                                                                                                                                                                                                                                                          |  |

| AIEN     | 4    | Clear channel interrupt enable. When asserted, permits Clear interrupts to be generated.                                                                                                                                                                                                                                                          |  |

| WEN      | 3    | Wait enable. This bit activates the wait feature. Writing a 1 activates the wait timer. Writing a 0 disables the wait timer.                                                                                                                                                                                                                      |  |

| PEN      | 2    | Proximity enable. This bit activates the proximity function. Writing a 1 enables proximity. Writing a 0 disables proximity.                                                                                                                                                                                                                       |  |

| AEN      | 1    | RGBC enable. This bit actives the two-channel ADC. Writing a 1 activates RGBC. Writing a 0 disables RGBC.                                                                                                                                                                                                                                         |  |

| PON 0    |      | Power ON. This bit activates the internal oscillator to permit the timers and ADC channels to operate. Writing a 1 activates the oscillator. Writing a 0 disables the oscillator. During reads and writes over the I <sup>2</sup> C interface, this bit is temporarily overridden and the oscillator is enabled, independent of the state of PON. |  |

Page 28ams DatasheetDocument Feedback[v1-01] 2018-Mar-14

# RGBC Time Register (0x01)

The RGBC timing register controls the internal integration time of the RGBC clear and IR channel ADCs in 2.4-ms increments. Upon power up, the RGBC time register is set to 0xFF.

Figure 34: **RGBC Time Register**

| Fields  | Bits | Description |              |        |           |  |  |  |  |

|---------|------|-------------|--------------|--------|-----------|--|--|--|--|

|         |      | VALUE       | INTEG_CYCLES | TIME   | MAX COUNT |  |  |  |  |

|         |      | 0xFF        | 1            | 2.4 ms | 1024      |  |  |  |  |

| ATIME   | 7:0  | 0xF6        | 10           | 24 ms  | 10240     |  |  |  |  |

| ATTIVIE |      | 0xD6        | 42           | 101 ms | 43008     |  |  |  |  |

|         |      | 0xAD        | 64           | 154 ms | 65535     |  |  |  |  |

|         |      | 0x00        | 256          | 614 ms | 65535     |  |  |  |  |

# Proximity Time Register (0x02)

The proximity timing register controls the integration time of the proximity ADC in 2.4 ms increments. Upon power up, the proximity time register is set to 0xFF. It is recommended that this register be programmed to a value of 0xFF (1 integration cycle).

Max Prox Count =  $((256 - PTIME) \times 1024)) - 1$  up to a maximum of 65535.

Figure 35: **Proximity Time Register**

| Fields      | Bits     | Description  |        |           |  |  |  |  |

|-------------|----------|--------------|--------|-----------|--|--|--|--|

| PTIME 7:0 - | VALUE    | INTEG_CYCLES | TIME   | MAX COUNT |  |  |  |  |

|             | 7:0 0xFF | 1            | 2.4 ms | 1023      |  |  |  |  |

ams Datasheet Page 29 **Document Feedback**

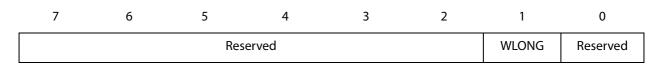

# Wait Time Register (0x03)