# ANALOG 10-Bit Monitor and Control System with ADC, DEVICES DACS Temperature Sensor and GPIOS **DACs, Temperature Sensor, and GPIOs**

**AD7292 Data Sheet**

### **FEATURES**

#### 10-bit SAR ADC

8 multiplexed analog input channels Single-ended mode of operation Differential mode of operation 5 V analog input range  $V_{REF}$ ,  $2 \times V_{REF}$ , or  $4 \times V_{REF}$  input ranges

Input measured with respect to A<sub>GND</sub> or V<sub>DD</sub>

4 monotonic, 10-bit, 5 V DACs

2 µs settling time

Power-on reset to 0 V

10 mA sink and source capability

Internal temperature sensor

±1°C accuracy

12 general-purpose digital I/O pins

Internal 1.25 V reference

**Built-in monitoring features**

Minimum and maximum value register for each channel

Programmable alert thresholds

**Programmable hysteresis**

**SPI** interface

Temperature range: -40°C to +125°C

Package type: 36-lead LFCSP

### **APPLICATIONS**

Base station power amplifier (PA) monitoring and control RF control loops

**Optical communication system control**

General-purpose system monitoring and control

### **GENERAL DESCRIPTION**

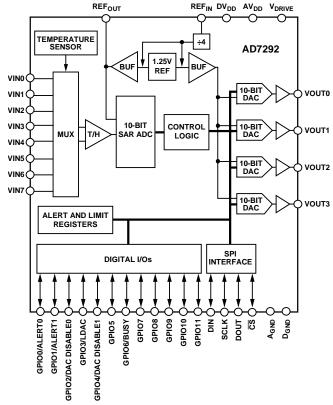

The AD7292 contains all the functionality required for generalpurpose monitoring of analog signals and control of external devices, integrated into a single-chip solution. The AD7292 features an 8-channel, 10-bit SAR ADC, four 10-bit DACs, a ±1°C accurate internal temperature sensor, and 12 GPIOs to aid system monitoring and control.

The 10-bit, high speed, low power successive approximation register (SAR) ADC is designed to monitor a variety of singleended input signals. Differential operation is also available by configuring VIN0 and VIN1 to operate as a differential pair.

The AD7292 offers a register programmable ADC sequencer, which enables the selection of a programmable sequence of channels for conversion.

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

Four 10-bit digital-to-analog converters (DACs) provide outputs from 0 V to 5 V. An internal, high accuracy, 1.25 V reference provides a separately buffered reference source for both the ADC and the DACs.

A high accuracy band gap temperature sensor is monitored and digitized by the 10-bit ADC to give a resolution of 0.03125°C. The AD7292 also features built-in limit and alarm functions.

The AD7292 is a highly integrated solution offered in a 36-lead LFCSP package with an operating temperature range of -40°C to +125°C.

### **TABLE OF CONTENTS**

| Features                                    | . 1 |

|---------------------------------------------|-----|

| Applications                                | . 1 |

| Functional Block Diagram                    | . 1 |

| General Description                         | . 1 |

| Revision History                            | . 2 |

| Specifications                              | . 3 |

| ADC Specifications                          | . 3 |

| DAC Specifications                          | . 4 |

| General Specifications                      | . 5 |

| Temperature Sensor Specifications           | . 5 |

| Timing Specifications                       | . 6 |

| Absolute Maximum Ratings                    | . 7 |

| Thermal Resistance                          | . 7 |

| ESD Caution                                 | . 7 |

| Pin Configuration and Function Descriptions | . 8 |

| Typical Performance Characteristics         | 10  |

| Theory of Operation                         | 15  |

| Analog Inputs                               | 15  |

| ADC Transfer Functions                      | 16  |

| Temperature Sensor                          | 17  |

| DAC Operation                               | 17  |

| Digital I/O Pins                            | 17  |

| Serial Port Interface (SPI)                 | 18  |

| Interface Protocol                          | 18  |

| Register Structure                          | 20  |

| Register Descriptions                       | 21  |

| Vendor ID Register (Address 0x00)           | 21  |

| ADC Data Register (Address 0x01)            | 21  |

| ADC sequence Register (Address 0x03)                                         | 41 |

|------------------------------------------------------------------------------|----|

| Configuration Register Bank (Address 0x05)                                   | 21 |

| Alert Limits Register Bank (Address 0x06)                                    | 30 |

| Alert Flags Register Bank (Address 0x07)                                     | 31 |

| Minimum and Maximum Register Bank (Address 0x08)                             | 32 |

| Offset Register Bank (Address 0x09)                                          | 32 |

| DAC Buffer Enable Register (Address 0x0A)                                    | 33 |

| GPIO Register (Address 0x0B)                                                 | 33 |

| Conversion Command Register (Address 0x0E)                                   | 34 |

| ADC Conversion Result Registers, VIN0 to VIN7 (Address 0x10 to Address 0x17) | 34 |

| T <sub>SENSE</sub> Conversion Result Register (Address 0x20)                 | 34 |

| DAC Channel Registers (Address 0x30 to Address 0x33)                         | 34 |

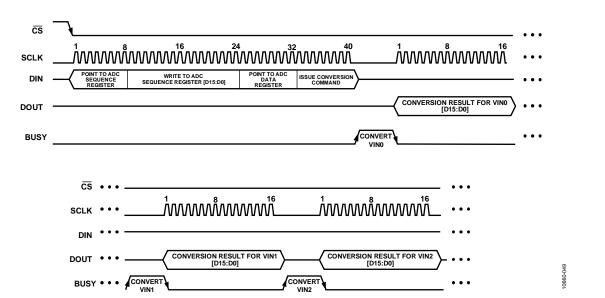

| ADC Conversion Control                                                       | 35 |

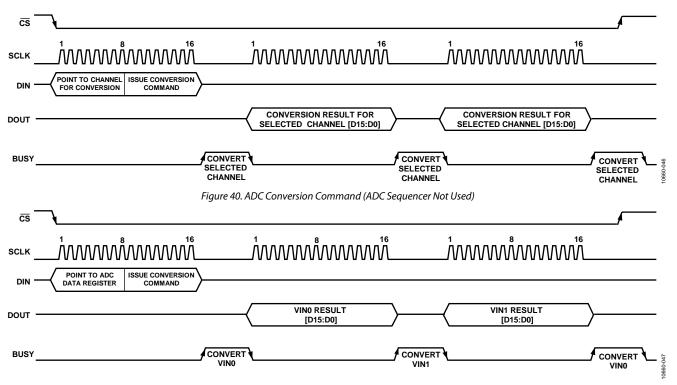

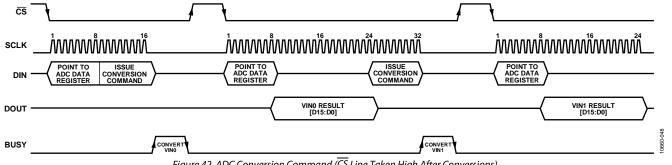

| ADC Conversion Command                                                       | 35 |

| ADC Sequencer                                                                | 36 |

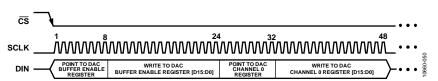

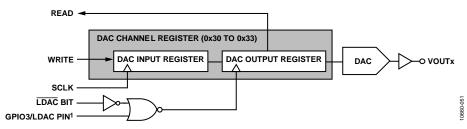

| DAC Output Control                                                           | 37 |

| LDAC Operation                                                               | 37 |

| Simultaneous Update of All DAC Outputs                                       | 37 |

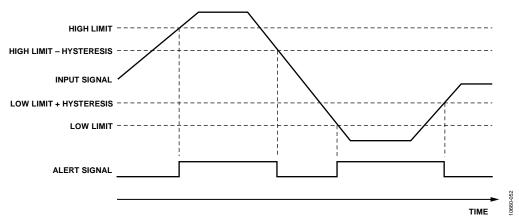

| Alerts and Limits                                                            | 38 |

| Alert Limit Monitoring Features                                              | 38 |

| Hardware Alert Pins                                                          | 38 |

| Alert Flag Bits in the Conversion Result Registers                           | 38 |

| Alert Flags Register Bank                                                    | 39 |

| Minimum and Maximum Conversion Results                                       | 39 |

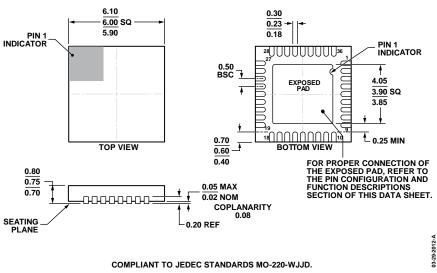

| Outline Dimensions                                                           | 40 |

| Onderine Colle                                                               | 40 |

### **REVISION HISTORY**

10/12—Revision 0: Initial Version

### **SPECIFICATIONS**

### **ADC SPECIFICATIONS**

$AV_{DD} = 4.75 \text{ V to } 5.25 \text{ V}, DV_{DD} = 1.8 \text{ V to } 5.25 \text{ V}, V_{REF} = 1.25 \text{ V internal}, V_{DRIVE} = 1.8 \text{ V to } 5.25 \text{ V}, A_{GND} = 0 \text{ V}, T_{A} = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1.

| Parameter                                       | Min                        | Тур   | Max                 | Unit   | Test Conditions/Comments                                |

|-------------------------------------------------|----------------------------|-------|---------------------|--------|---------------------------------------------------------|

| DC ACCURACY                                     |                            |       |                     |        |                                                         |

| Resolution                                      | 10                         |       |                     | Bits   |                                                         |

| Integral Nonlinearity (INL) <sup>1</sup>        |                            | ±0.11 | ±0.5                | LSB    |                                                         |

|                                                 |                            |       | ±0.6                | LSB    | $(AV_{DD} - 4 \times V_{REF})$ to $AV_{DD}$ input range |

| Differential Nonlinearity (DNL) <sup>1</sup>    |                            | ±0.1  | ±0.99               | LSB    |                                                         |

| Offset Error                                    |                            | ±3    | ±8                  | mV     |                                                         |

|                                                 |                            |       | ±12                 | mV     | $(AV_{DD} - 4 \times V_{REF})$ to $AV_{DD}$ input range |

| Offset Error Matching                           |                            | 0.5   | ±1                  | mV     |                                                         |

| Offset Error Drift                              |                            | ±0.22 |                     | ppm/°C |                                                         |

| Gain Error                                      |                            | ±0.09 | ±0.25               | % FS   |                                                         |

|                                                 |                            |       | ±0.36               | % FS   | $(AV_{DD} - 4 \times V_{REF})$ to $AV_{DD}$ input range |

| Gain Error Matching                             |                            | ±0.5  |                     | % FS   |                                                         |

| Gain Error Drift                                |                            | ±4.17 |                     | ppm/°C |                                                         |

| DYNAMIC PERFORMANCE <sup>1</sup>                |                            |       |                     |        | f <sub>IN</sub> = 10 kHz sine wave                      |

| Signal-to-Noise Ratio (SNR)                     |                            | 61.5  |                     | dB     |                                                         |

| Signal-to-Noise-and-Distortion (SINAD)<br>Ratio |                            | 61.5  |                     | dB     |                                                         |

| Total Harmonic Distortion (THD)                 |                            | -84   |                     | dB     |                                                         |

| Spurious-Free Dynamic Range (SFDR)              |                            | 84.5  |                     | dB     |                                                         |

| Channel-to-Channel Isolation                    |                            | -80   |                     | dB     | $f_{IN} = 3 \text{ kHz to } 1000 \text{ kHz}$           |

| Full Power Bandwidth                            |                            | 60    |                     | MHz    | At $-3$ dB (0 V to $V_{REF}$ input range)               |

|                                                 |                            | 3     |                     | MHz    | At –0.1 dB (0 V to V <sub>REF</sub> input range)        |

| CONVERSION RATE                                 |                            |       |                     |        |                                                         |

| Conversion Time                                 |                            | 900   |                     | ns     | See Table 5                                             |

| Track-and-Hold Acquisition Time                 |                            |       | 45                  | ns     |                                                         |

| Throughput Rate                                 |                            |       | 625                 | kSPS   | ADC only; temperature sensor disabled                   |

|                                                 |                            |       | 150                 | kSPS   | ADC and temperature sensor                              |

| ANALOG INPUT                                    |                            |       |                     |        |                                                         |

| Single-Ended Input Range                        |                            |       |                     |        |                                                         |

| With Respect to A <sub>GND</sub>                | 0                          |       | $4 \times V_{REF}$  | V      |                                                         |

|                                                 | 0                          |       | $2 \times V_{REF}$  | V      |                                                         |

|                                                 | 0                          |       | $V_{REF}$           | V      |                                                         |

| With Respect to AV <sub>DD</sub>                | $AV_{DD} - 4 \times V_{R}$ | EF    | $AV_{DD}$           | V      |                                                         |

| Fully Differential Input Range                  | $-4 \times V_{REF}$        |       | $+4 \times V_{REF}$ | V      | VINO and VIN1 inputs only                               |

|                                                 | $-2 \times V_{REF}$        |       | $+2 \times V_{REF}$ | V      |                                                         |

|                                                 | $-V_{REF}$                 |       | $+V_{REF}$          | V      |                                                         |

| Input Capacitance                               |                            | 23    |                     | pF     | 0 V to V <sub>REF</sub> input range                     |

|                                                 |                            | 18    |                     | pF     | $0 \text{ V}$ to $2 \times V_{REF}$ input range         |

|                                                 |                            | 15    |                     | pF     | $0 \text{ V}$ to $4 \times V_{REF}$ input range         |

| DC Input Leakage Current                        |                            |       | ±1                  | μΑ     |                                                         |

| INTERNAL REFERENCE                              |                            |       |                     |        |                                                         |

| Reference Output Voltage                        | 1.245                      | 1.25  | 1.255               | V      | At 25°C                                                 |

| Reference Temperature Coefficient               |                            | ±13   |                     | ppm/°C |                                                         |

| Parameter               | Min  | Тур | Max     | Unit | Test Conditions/Comments             |

|-------------------------|------|-----|---------|------|--------------------------------------|

| EXTERNAL REFERENCE      |      |     |         |      |                                      |

| Reference Input Voltage | 4.75 |     | $AV_DD$ | V    | Internal reference used to calibrate |

|                         |      |     |         |      | temperature sensor                   |

| Input Resistance        |      | 100 |         | kΩ   |                                      |

$<sup>^{\</sup>rm 1}$  Specifications also apply to differential mode.

### **DAC SPECIFICATIONS**

$AV_{DD} = 4.75 \text{ V}$  to 5.25 V,  $DV_{DD} = 1.8 \text{ V}$  to 5.25 V,  $V_{REF} = 1.25 \text{ V}$  internal,  $V_{DRIVE} = 1.8 \text{ V}$  to 5.25 V,  $A_{GND} = 0 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to +125 °C, unless otherwise noted.

Table 2.

| Parameter                                    | Min | Тур   | Max                | Unit   | Test Conditions/Comments                                                                                                   |

|----------------------------------------------|-----|-------|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| DC ACCURACY                                  |     |       |                    |        |                                                                                                                            |

| Resolution                                   | 10  |       |                    | Bits   |                                                                                                                            |

| Integral Nonlinearity (INL)                  |     | ±0.2  | ±1                 | LSB    |                                                                                                                            |

| Differential Nonlinearity (DNL)              |     | ±0.1  | ±0.3               | LSB    | Guaranteed monotonic                                                                                                       |

| Zero-Scale Error                             |     | 4.8   | ±10                | mV     | All 0s loaded to DAC register                                                                                              |

| Full-Scale Error                             |     | ±0.1  | ±0.5               | % FS   | All 1s loaded to DAC register                                                                                              |

| Offset Error                                 |     | ±1.62 | ±10                | mV     | Measured in the linear region,<br>$T_A = -40$ °C to $+125$ °C                                                              |

| Offset Error Drift                           |     | ±4.4  |                    | ppm/°C | Measured in the linear region, $T_A = 25^{\circ}C$                                                                         |

| Gain Error                                   |     | ±0.35 | ±0.5               | % FS   |                                                                                                                            |

| Gain Error Drift                             |     | ±2.6  |                    | ppm/°C |                                                                                                                            |

| DC Power Supply Rejection Ratio (PSRR)       |     | -50   |                    | dB     | f <sub>RIPPLE</sub> up to 100 kHz                                                                                          |

| DC Crosstalk                                 |     | 5     |                    | μV     |                                                                                                                            |

| DAC OUTPUT CHARACTERISTICS                   |     |       |                    |        |                                                                                                                            |

| Output Voltage Range                         | 0   |       | $4 \times V_{REF}$ | V      |                                                                                                                            |

| Short-Circuit Current                        |     | ±30   |                    | mA     |                                                                                                                            |

| Load Current                                 |     | ±10   |                    | mA     | Sink/source current; within ±200 mV of supply                                                                              |

| Resistive Load to A <sub>GND</sub>           |     | 500   |                    | Ω      |                                                                                                                            |

| Capacitive Load Stability                    |     |       | 1                  | nF     |                                                                                                                            |

| DC Output Impedance                          |     | 1     |                    | Ω      |                                                                                                                            |

| AC CHARACTERISTICS <sup>1</sup>              |     |       |                    |        |                                                                                                                            |

| Output Voltage Settling Time                 |     | 1     | 2                  | μs     | 1/4 to 3/4 scale step change within 1 LSB, measured from last SCLK edge                                                    |

| Overshoot                                    |     | 200   |                    | mV     | $\frac{1}{4}$ to $\frac{3}{4}$ scale step change within 1 LSB, measured from last SCLK edge; $C_L = 200$ pF, $R_L = 25$ kΩ |

| Slew Rate                                    | 9   | 12    |                    | V/µs   |                                                                                                                            |

| Digital-to-Analog Glitch Impulse             |     | 4     |                    | nV-sec |                                                                                                                            |

| Digital Feedthrough                          |     | 0.4   |                    | nV-sec |                                                                                                                            |

| DAC-to-DAC Crosstalk                         |     | 2     |                    | nV-sec |                                                                                                                            |

| Output Noise Spectral Density                |     | 730   |                    | nV/√Hz | DAC code = midscale, 1 kHz                                                                                                 |

| Output Noise                                 |     | 28    |                    | μV rms | 0.1 Hz to 10 Hz                                                                                                            |

| Output Transient Response During<br>Power-Up |     | 5     |                    | mV     | $AV_{DD}$ ramp of 1 ms with 100 k $\Omega$ load                                                                            |

$<sup>^1</sup>$  The DAC buffer output level is undefined until 30  $\mu s$  after all supplies reach their minimum specified operating voltages.

### **GENERAL SPECIFICATIONS**

$AV_{DD} = 4.75 \text{ V}$  to 5.25 V,  $DV_{DD} = 1.8 \text{ V}$  to 5.25 V,  $V_{REF} = 1.25 \text{ V}$  internal,  $V_{DRIVE} = 1.8 \text{ V}$  to 5.25 V,  $A_{GND} = 0 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+125 ^{\circ}\text{C}$ , unless otherwise noted.

Table 3.

| Parameter                              | Min                    | Тур                   | Max                           | Unit | Test Conditions/Comments                                                                                                                              |

|----------------------------------------|------------------------|-----------------------|-------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC INPUTS                           |                        |                       |                               |      |                                                                                                                                                       |

| Input High Voltage, V <sub>IH</sub>    | $0.7 \times V_{DRIVE}$ |                       |                               | V    | $V_{DRIVE} = 2.3 \text{ V to } 5.25 \text{ V}$                                                                                                        |

|                                        | $0.8 \times V_{DRIVE}$ |                       |                               | V    | $V_{DRIVE} = 1.8 V \text{ to } 1.95 V$                                                                                                                |

| Input Low Voltage, V <sub>I</sub> L    |                        |                       | $0.3 \times V_{\text{DRIVE}}$ | V    | $V_{DRIVE} = 2.3 \text{ V to } 5.25 \text{ V}$                                                                                                        |

|                                        |                        |                       | $0.2 \times V_{DRIVE}$        | V    | $V_{DRIVE} = 1.8 V \text{ to } 1.95 V$                                                                                                                |

| Input Leakage Current, I <sub>IN</sub> |                        |                       | ±1                            | μΑ   |                                                                                                                                                       |

| Input Capacitance, C <sub>IN</sub>     |                        | 3                     |                               | рF   |                                                                                                                                                       |

| Input Hysteresis, V <sub>HYST</sub>    |                        | $0.05 \times V_{DRI}$ | VE                            | V    |                                                                                                                                                       |

| GPIO OUTPUTS                           |                        |                       |                               |      |                                                                                                                                                       |

| Isink/Isource                          |                        | 1.6                   |                               | mA   |                                                                                                                                                       |

| Output High Voltage, V <sub>OH</sub>   | $DV_{DD} - 0.2$        |                       |                               | V    | $I_{SINK}/I_{SOURCE} = 1.6 \text{ mA}$                                                                                                                |

| Output Low Voltage, Vol                |                        |                       | 0.4                           | V    | I <sub>SINK</sub> /I <sub>SOURCE</sub> = 1.6 mA                                                                                                       |

| POWER REQUIREMENTS                     |                        |                       |                               |      |                                                                                                                                                       |

| $AV_DD$                                | 4.75                   |                       | 5.25                          | V    |                                                                                                                                                       |

| $DV_{DD}$                              | 1.8                    |                       | 5.25                          | V    |                                                                                                                                                       |

| $V_{DRIVE}$                            | 1.8                    |                       | 5.25                          | V    |                                                                                                                                                       |

| Static Current                         |                        |                       |                               |      |                                                                                                                                                       |

| lavdd                                  |                        | 4.2                   | 5.4                           | mA   |                                                                                                                                                       |

| l <sub>DVDD</sub>                      |                        | 0.65                  | 1.3                           | mA   |                                                                                                                                                       |

| I <sub>DRIVE</sub>                     |                        | 0.12                  | 0.35                          | mA   |                                                                                                                                                       |

| Total Static Current                   |                        | 4.97                  |                               | mA   | $AV_{DD} + DV_{DD} + V_{DRIVE}$                                                                                                                       |

| Dynamic Current                        |                        |                       |                               |      |                                                                                                                                                       |

| I <sub>AVDD</sub>                      |                        | 6.45                  | 8.5                           | mA   |                                                                                                                                                       |

| l <sub>DVDD</sub>                      |                        | 0.65                  | 1.3                           | mA   |                                                                                                                                                       |

| I <sub>DRIVE</sub>                     |                        | 0.12                  | 0.35                          | mA   |                                                                                                                                                       |

| Total Dynamic Current                  |                        | 7.22                  |                               | mA   | AV <sub>DD</sub> + DV <sub>DD</sub> + V <sub>DRIVE</sub> , DAC outputs loaded<br>and converting at full scale, continuous<br>conversion on ADC inputs |

| Power Dissipation                      |                        |                       |                               |      |                                                                                                                                                       |

| Static                                 |                        | 26                    | 34.125                        | mW   |                                                                                                                                                       |

| Dynamic                                |                        | 37.9                  | 50.925                        | mW   |                                                                                                                                                       |

### **TEMPERATURE SENSOR SPECIFICATIONS**

$AV_{DD} = 4.75 \text{ V}$  to 5.25 V,  $DV_{DD} = 1.8 \text{ V}$  to 5.25 V,  $V_{REF} = 1.25 \text{ V}$  internal,  $V_{DRIVE} = 1.8 \text{ V}$  to 5.25 V,  $A_{GND} = 0 \text{ V}$ ,  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise noted.

Table 4.

| Parameter                   | Min | Тур     | Max  | Unit | Test Conditions/Comments                             |

|-----------------------------|-----|---------|------|------|------------------------------------------------------|

| INTERNAL TEMPERATURE SENSOR |     |         |      |      |                                                      |

| Operating Range             | -40 |         | +125 | °C   |                                                      |

| Accuracy                    |     | ±1      | ±3   | °C   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

|                             |     | ±1      | ±2   | °C   | $T_A = 0$ °C to +125°C                               |

|                             |     | 0.5     | ±1.5 | °C   | T <sub>A</sub> = 25°C                                |

| Resolution                  |     | 0.03125 |      | °C   | Digital filter enabled                               |

| Update Rate                 |     | 1.25    |      | ms   |                                                      |

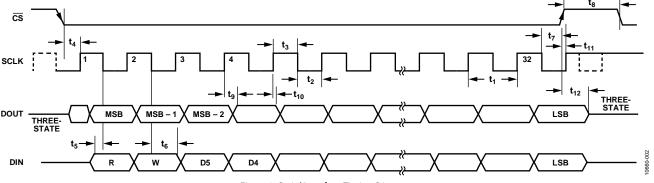

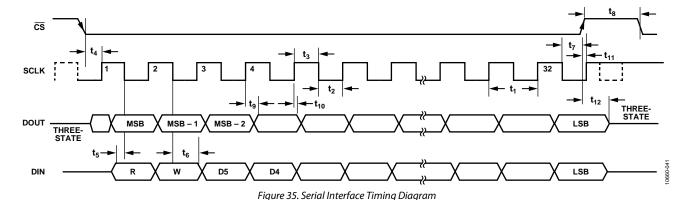

### **TIMING SPECIFICATIONS**

$AV_{DD} = 4.75 \text{ V}$  to 5.25 V,  $DV_{DD} = 1.8 \text{ V}$  to 5.25 V,  $V_{REF} = 1.25 \text{ V}$  internal,  $V_{DRIVE} = 1.8 \text{ V}$  to 5.25 V,  $A_{GND} = 0 \text{ V}$ ,  $C_{L} = 27 \text{ pF}$ ,  $T_{A} = -40 ^{\circ}\text{C}$ to +125°C, unless otherwise noted.1

Table 5.

|                             |                                             | Limit at                                 |                                      |         |

|-----------------------------|---------------------------------------------|------------------------------------------|--------------------------------------|---------|

| Parameter                   | Description                                 | <b>V</b> <sub>DRIVE</sub> = <b>1.8 V</b> | V <sub>DRIVE</sub> = 2.7 V to 5.25 V | Unit    |

| t <sub>CONVERT</sub>        | ADC conversion time/BUSY high time          |                                          |                                      |         |

|                             | Temperature sensor disabled                 | 950                                      | 950                                  | ns max  |

|                             | Temperature sensor enabled                  | 5.85                                     | 5.85                                 | μs max  |

| $t_{ACQ}$                   | ADC acquisition time                        | 50                                       | 50                                   | ns max  |

| $f_{SCLK}$                  | Frequency of serial read clock <sup>2</sup> | 15                                       | 25                                   | MHz max |

| t <sub>1</sub>              | SCLK period                                 | 66                                       | 40                                   | ns min  |

| $t_2$                       | SCLK low                                    | 33                                       | 20                                   | ns min  |

| t <sub>3</sub>              | SCLK high                                   | 33                                       | 20                                   | ns min  |

| t <sub>4</sub>              | CS falling edge to SCLK rising edge         | 4                                        | 4                                    | ns min  |

| t <sub>5</sub>              | DIN setup time to SCLK falling edge         | 4                                        | 4                                    | ns min  |

| t <sub>6</sub> <sup>3</sup> | DIN hold time after SCLK falling edge       | 2                                        | 2                                    | ns max  |

| t <sub>7</sub>              | SCLK falling edge to CS rising edge         | 5                                        | 5                                    | ns min  |

| t <sub>8</sub>              | CS high                                     | 5                                        | 5                                    | ns min  |

| t <sub>9</sub>              | SCLK to output data valid delay time        | 30                                       | 19                                   | ns max  |

| t <sub>10</sub>             | SCLK to output data valid hold time         | 7                                        | 5                                    | ns min  |

| t <sub>11</sub> 4, 5        | CS rising edge to SCLK rising edge          | 4                                        | 4                                    | ns max  |

| t <sub>12</sub>             | CS rising edge to DOUT high impedance       | 15                                       | 15                                   | ns max  |

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $V_{DRIVE}$ ).

### **Timing Diagram**

Figure 2. Serial Interface Timing Diagram

<sup>&</sup>lt;sup>2</sup> For  $V_{DRIVE} = 2.5 \text{ V}$ ,  $f_{SCLK} = 22 \text{ MHz maximum}$ .

<sup>3</sup> Time required for the output to cross  $0.2 \times V_{DRIVE}$  and  $0.8 \times V_{DRIVE}$  when  $V_{DRIVE} = 1.8 \text{ V}$ ; time required for the output to cross  $0.3 \times V_{DRIVE}$  and  $0.7 \times V_{DRIVE}$  when  $V_{DRIVE} = 2.7 \text{ V}$  to 5.25 V.

<sup>&</sup>lt;sup>4</sup>t<sub>11</sub> applies when using a continuous SCLK.

<sup>&</sup>lt;sup>5</sup> Guaranteed by design.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

### Table 6.

| Parameter                                      | Rating                                        |

|------------------------------------------------|-----------------------------------------------|

| AV <sub>DD</sub> to A <sub>GND</sub>           | -0.3 V to +6 V                                |

| $DV_DD$ to $D_GND$                             | -0.3 V to +6 V                                |

| $V_{DRIVE}$ to $D_{GND}$                       | −0.3 V to +6 V                                |

| VINx to A <sub>GND</sub>                       | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$   |

| VOUTx to A <sub>GND</sub>                      | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$   |

| Digital Inputs/Outputs to D <sub>GND</sub>     | $-0.3 \text{ V to DV}_{DD} + 0.3 \text{ V}$   |

| $\overline{CS}$ , SCLK, DIN, DOUT to $D_{GND}$ | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |

| REF <sub>OUT</sub> to A <sub>GND</sub>         | -0.3 V to +2.2 V                              |

| $REF_IN$ to $A_GND$                            | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$   |

| $D_{GND}$ to $A_{GND}$                         | 0.3 V                                         |

| Operating Temperature Range                    | −40°C to +125°C                               |

| Storage Temperature Range                      | −65°C to +150°C                               |

| Junction Temperature (T <sub>J</sub> max)      | 150°C                                         |

| ESD, Human Body Model                          | 2.5 kV                                        |

| Reflow Soldering Peak Temperature              | 260°C                                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

Table 7. Thermal Resistance

| Package Type  | $\theta_{JA}$ | Unit |

|---------------|---------------|------|

| 36-Lead LFCSP | 54.1          | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

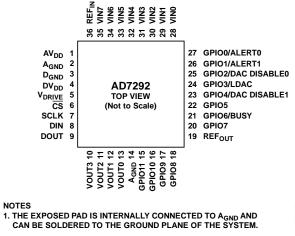

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No.  | Mnemonic               | Description                                                                                                                                                                                                                                                                                         |

|----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | $AV_{DD}$              | Supply Pin. This pin should be decoupled to A <sub>GND</sub> with a 0.1 µF decoupling capacitor.                                                                                                                                                                                                    |

| 2, 14    | A <sub>GND</sub>       | Analog Ground. Ground reference point for all analog circuitry on the AD7292. All analog signals should be referred to $A_{GND}$ . Both the $A_{GND}$ and $D_{GND}$ pins should be connected to the ground plane of the system.                                                                     |

| 3        | $D_{GND}$              | Digital Ground. Ground reference point for all digital circuitry on the AD7292. All digital signals should be referred to $D_{GND}$ . Both the $D_{GND}$ and $A_{GND}$ pins should be connected to the ground plane of the system.                                                                  |

| 4        | $DV_{DD}$              | Sets the GPIO voltage level. This pin should be decoupled to $D_{GND}$ with a 0.1 $\mu F$ decoupling capacitor.                                                                                                                                                                                     |

| 5        | V <sub>DRIVE</sub>     | This pin sets the reference level of the SPI bus from 1.8 V to 5.25 V. This pin should be decoupled to $D_{\text{GND}}$ with a 0.1 $\mu\text{F}$ decoupling capacitor.                                                                                                                              |

| 6        | <del>CS</del>          | Chip Select Signal. This active low logic input signal is used to frame the serial data input.                                                                                                                                                                                                      |

| 7        | SCLK                   | SPI Clock Input.                                                                                                                                                                                                                                                                                    |

| 8        | DIN                    | SPI Serial Data Input. Serial data to be loaded into the registers of the AD7292 is provided on this pin.  Data is clocked into the serial interface on the falling edge of SCLK.                                                                                                                   |

| 9        | DOUT                   | SPI Serial Data Output. Serial data to be read from the registers of the AD7292 is provided on this pin.  Data is clocked out on the rising edge of SCLK. DOUT is high impedance when it is not outputting data.                                                                                    |

| 10 to 13 | VOUT3 to VOUT0         | Buffered DAC Analog Outputs. Each DAC analog output is driven from an output amplifier and has a maximum output voltage span of 5 V. Each DAC is capable of sourcing and sinking 10 mA and driving a 1 nF load.                                                                                     |

| 15 to 18 | GPIO11 to GPIO8        | General-Purpose Input/Output Pins.                                                                                                                                                                                                                                                                  |

| 19       | REF <sub>OUT</sub>     | ADC Internal Reference Output. Decouple the internal ADC reference buffer to $A_{\text{GND}}$ with a 0.1 $\mu\text{F}$ decoupling capacitor.                                                                                                                                                        |

| 20       | GPIO7                  | General-Purpose Input/Output Pin.                                                                                                                                                                                                                                                                   |

| 21       | GPIO6/BUSY             | General-Purpose Input/Output Pin (GPIO6).  Busy Output Pin (BUSY). When a conversion starts, this output pin transitions high and remains high until the conversion is completed.                                                                                                                   |

| 22       | GPIO5                  | General-Purpose Input/Output Pin.                                                                                                                                                                                                                                                                   |

| 23       | GPIO4/<br>DAC DISABLE1 | General-Purpose Input/Output Pin (GPIO4).  DAC Disable Pin 1 (DAC DISABLE1). When this pin is activated, the selected DAC outputs are disabled.  Select the DAC channels to be disabled by this pin using the GPIO4/DAC DISABLE1 subregister within the configuration register bank (see Table 30). |

| 24       | GPIO3/LDAC             | General-Purpose Input/Output Pin (GPIO3).  LDAC Input Pin (LDAC). When this input is taken high, the DAC registers are updated.                                                                                                                                                                     |

| 25       | GPIO2/<br>DAC DISABLE0 | General-Purpose Input/Output Pin (GPIO2).  DAC Disable Pin 0 (DAC DISABLE0). When this pin is activated, the selected DAC outputs are disabled.  Select the DAC channels to be disabled by this pin using the GPIO2/DAC DISABLE0 subregister within the configuration register bank (see Table 29). |

| Pin No.  | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26       | GPIO1/ALERT1      | General-Purpose Input/Output Pin (GPIO1).                                                                                                                                                                                                                                                                                                 |

|          |                   | Alert Pin 1 (ALERT1). When configured as an alert, this pin acts as an out-of-range indicator and becomes active when the conversion result violates the high or low limit stored in the alert limits register bank. The polarity of the alert signal is controlled using the general subregister within the configuration register bank. |

| 27       | GPIO0/ALERT0      | General-Purpose Input/Output Pin (GPIO0).                                                                                                                                                                                                                                                                                                 |

|          |                   | Alert Pin 0 (ALERTO). When configured as an alert, this pin acts as an out-of-range indicator and becomes active when the conversion result violates the high or low limit stored in the alert limits register bank. The polarity of the alert signal is controlled using the general subregister within the configuration register bank. |

| 28 to 35 | VIN0 to VIN7      | Analog Inputs. The eight single-ended analog inputs of the AD7292 are multiplexed into the on-chip track-and-hold amplifier. Each input channel can accept analog inputs from 0 V to 5 V. Any unused input channels should be connected to A <sub>GND</sub> to avoid noise pickup.                                                        |

| 36       | REF <sub>IN</sub> | Voltage Reference Input. An external reference for the AD7292 can be applied to this pin. If this pin is unused, connect it to $A_{GND}$ .                                                                                                                                                                                                |

| EPAD     | EPAD              | The exposed pad is internally connected to A <sub>GND</sub> and can be soldered to the ground plane of the system.                                                                                                                                                                                                                        |

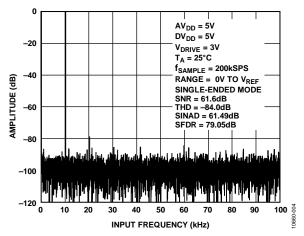

### TYPICAL PERFORMANCE CHARACTERISTICS

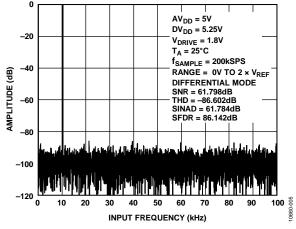

Figure 4. ADC FFT, 200 kSPS,  $f_{IN} = 10$  kHz, Single-Ended Mode

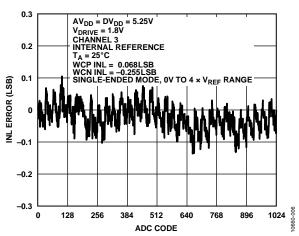

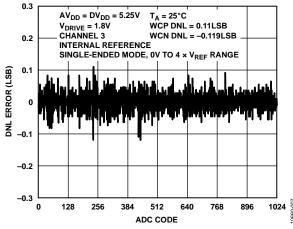

Figure 5. Typical ADC INL, Single-Ended Mode

Figure 6. Typical ADC DNL, Single-Ended Mode

Figure 7. ADC FFT, 200 kSPS,  $f_{IN} = 10$  kHz, Differential Mode

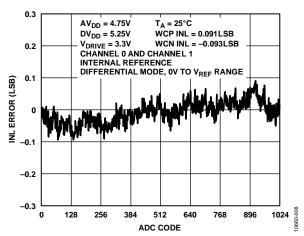

Figure 8. Typical ADC INL, Differential Mode

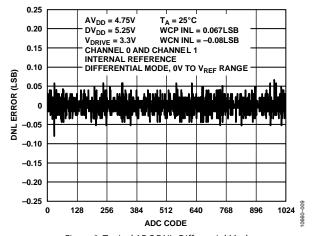

Figure 9. Typical ADC DNL, Differential Mode

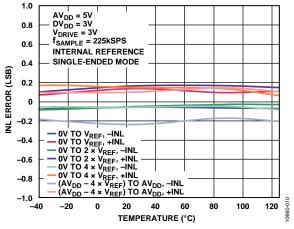

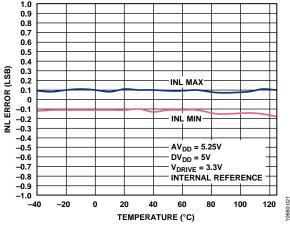

Figure 10. ADC INL vs. Temperature

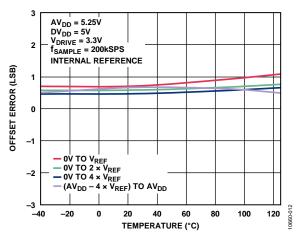

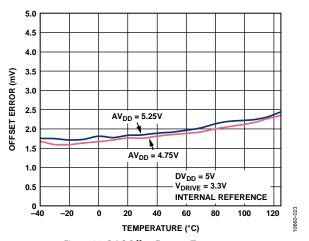

Figure 11. Offset Error vs. Temperature, Single-Ended and Differential Modes

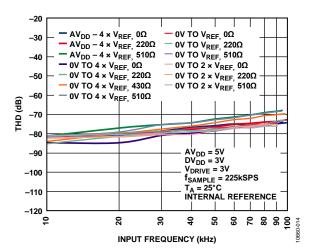

Figure 12. THD vs. Input Frequency for Various Source Impedances, Single-Ended Mode

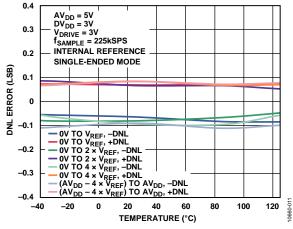

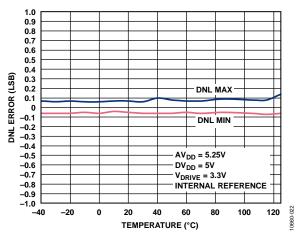

Figure 13. ADC DNL vs. Temperature

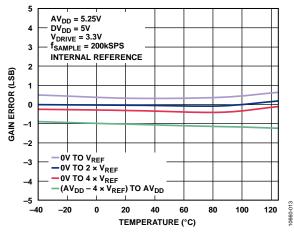

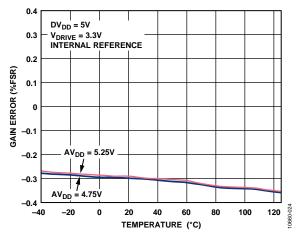

Figure 14. ADC Gain Error vs. Temperature, Single-Ended and Differential Modes

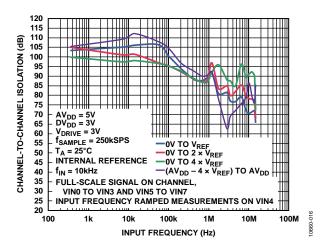

Figure 15. ADC Channel-to-Channel Isolation

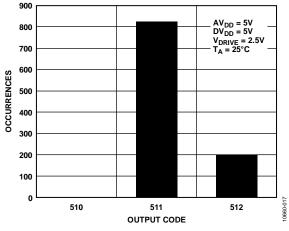

Figure 16. Histogram of Codes

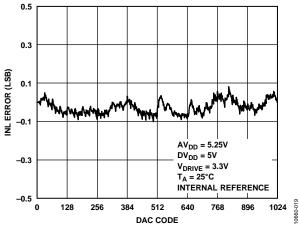

Figure 17. Typical DAC INL vs. Output Code

Figure 18. DAC INL vs. Temperature

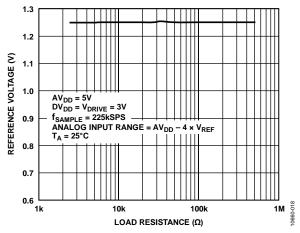

Figure 19. Reference Voltage vs. Load Resistance

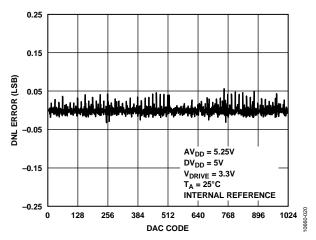

Figure 20. Typical DAC DNL vs. Output Code

Figure 21. DAC DNL vs. Temperature

Figure 22. DAC Offset Error vs. Temperature

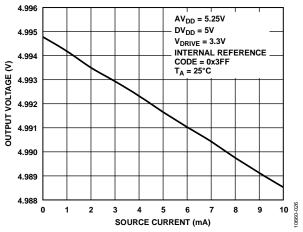

Figure 23. DAC Source Current (Full Scale)

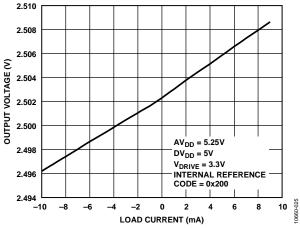

Figure 24. DAC Output Voltage vs. Load Current (Midscale)

Figure 25. DAC Gain Error vs. Temperature

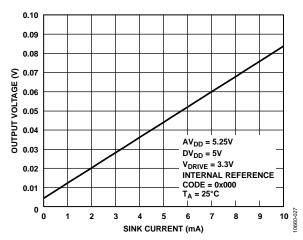

Figure 26. DAC Sink Current (Zero Scale)

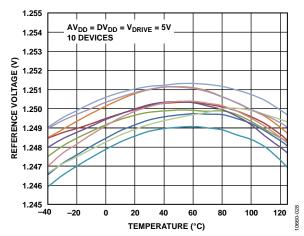

Figure 27. Reference Voltage vs. Temperature

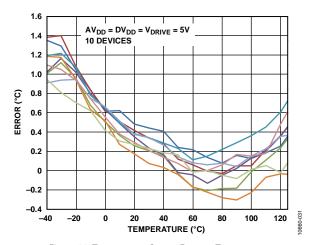

Figure 28. Temperature Sensor Error vs. Temperature

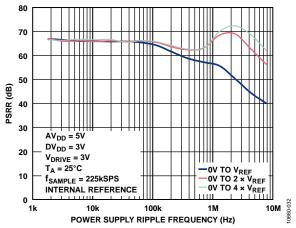

Figure 29. PSRR vs. Power Supply Ripple Frequency

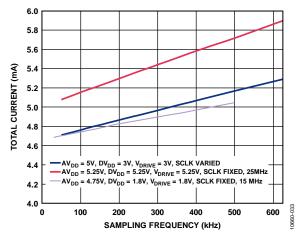

Figure 30. Total Supply Current vs. Throughput Rate

# THEORY OF OPERATION ANALOG INPUTS

The AD7292 has eight analog input channels. By default, these channels are configured as single-ended inputs. Differential operation is also available by configuring VIN0 and VIN1 to operate as a differential pair.

### Single-Ended Mode

In applications where the signal source has high impedance, it is recommended that the analog input be buffered before it is applied to the ADC.

The analog input range is programmed to one of these values: 0 V to  $V_{\text{REF}}$ , 0 V to 2 ×  $V_{\text{REF}}$ , or 0 V to 4 ×  $V_{\text{REF}}$ . For information about programming the input range, see the VIN RANGE0 and VIN RANGE1 Subregisters (Address 0x10 and Address 0x11) section.

In 0 V to 2 ×  $V_{REF}$  mode, the input is scaled by a factor of 2 before the conversion takes place. In 0 V to 4 ×  $V_{REF}$  mode, the input is scaled by a factor of 4 before the conversion takes place. Note that the voltage with respect to  $A_{GND}$  on the ADC analog input pins cannot exceed  $AV_{DD}$ .

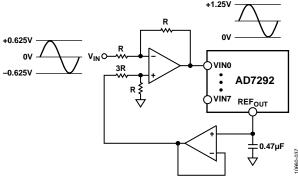

If the analog input signal to be sampled is bipolar, the internal reference of the ADC can be used to externally bias this signal up so that it is correctly formatted for the ADC. Figure 31 shows a typical connection diagram when operating the ADC in single-ended mode with a bipolar  $\pm 0.625$  V input signal.

Figure 31. Interfacing to a Bipolar Input Signal

### **Differential Mode**

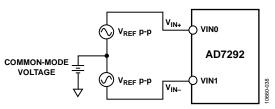

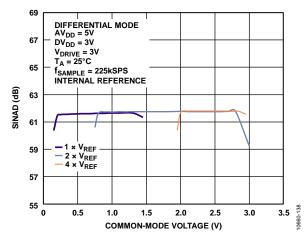

The AD7292 can be configured to have one differential analog input pair (VIN0 and VIN1). Differential signals have some benefits over single-ended signals, including noise immunity based on the common-mode rejection of the device and improvements in distortion performance. Figure 32 shows the fully differential analog input of the AD7292.

Figure 32. Differential Analog Input

The amplitude of the differential signal is the difference between the signals applied to the input pins of the differential pair, VIN0 and VIN1. The resulting converted data is stored in straight binary format in the ADC data register. VIN0 and VIN1 should be simultaneously driven by two signals that are 180° out of phase; each signal should be of maximum amplitude  $V_{\text{REF}}$ ,  $2\times V_{\text{REF}}$ , or  $4\times V_{\text{REF}}$ , depending on the selected range.

Therefore, if the 0 V to  $V_{REF}$  range is selected, the amplitude of the differential signal is  $-V_{REF}$  to  $+V_{REF}$  peak-to-peak (2 ×  $V_{REF}$ ), regardless of the common-mode voltage ( $V_{CM}$ ).

The common-mode voltage is the average of the two signals.

$$V_{CM} = (V_{IN+} + V_{IN-})/2$$

The common-mode voltage is, therefore, the voltage on which the two inputs are centered; the resulting span for each input is  $V_{\text{CM}} \pm V_{\text{REF}}/2$ . This voltage must be set up externally. When the inputs are driven with an amplifier, the actual common-mode range is determined by the output voltage swing of the amplifier and the input common-mode range of the AD7292. The common-mode voltage must be in this range to guarantee the functionality of the AD7292 (see Figure 33). When a conversion takes place, the common-mode voltage is rejected, resulting in a virtually noise-free signal of amplitude  $-V_{\text{REF}}$  to  $+V_{\text{REF}}$ .

Figure 33. Common-Mode Voltage (Dependent on Input Range)

### **ADC TRANSFER FUNCTIONS**

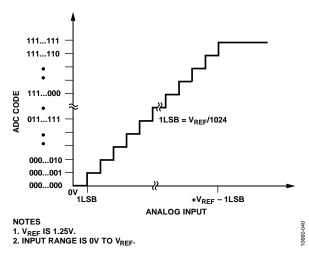

The output coding of the AD7292 is 10-bit straight binary for the analog input channels. The designated code transitions occur at successive LSB values.

To select the input range, set the appropriate bits in the VIN RANGE1 and VIN RANGE0 subregisters of the configuration register bank (see Table 10).

The LSB size depends on the input range selected (see Table 9).

Table 9. Input Range and LSB Size

| Input Range               | LSB Size                           |

|---------------------------|------------------------------------|

| 0 V to V <sub>REF</sub>   | V <sub>REF</sub> /2 <sup>10</sup>  |

| $0 V to 2 \times V_{REF}$ | 2V <sub>REF</sub> /2 <sup>10</sup> |

| $0 V to 4 \times V_{REF}$ | 4V <sub>REF</sub> /2 <sup>10</sup> |

The ideal transfer function for the AD7292 when operating with an input range of 0 V to  $V_{REF}$  is shown in Figure 34.

Table 10. Analog Input Range Selection

|                                       |            | Sample with R                      | Respect to A <sub>GND</sub>                | Sample with Respect to AV <sub>DD</sub> <sup>2</sup> |

|---------------------------------------|------------|------------------------------------|--------------------------------------------|------------------------------------------------------|

| Subregister Bit Settings <sup>1</sup> |            | Single-Ended Input Range           | Differential Input Range                   | Single-Ended Input Range                             |

| VIN RANGE1                            | VIN RANGEO | (VIN0 to VIN7)                     | (VIN0 and VIN1 Only)                       | (VIN0 to VIN7)                                       |

| 0                                     | 0          | $0 \text{ V to } 4 \times V_{REF}$ | $-4 \times V_{REF}$ to $+4 \times V_{REF}$ | $(AV_{DD} - 4 \times V_{REF})$ to $AV_{DD}$          |

| 0                                     | 1          | $0 \text{ V to } 2 \times V_{REF}$ | $-2 \times V_{REF}$ to $+2 \times V_{REF}$ | Not applicable                                       |

| 1                                     | 0          | $0 \text{ V to } 2 \times V_{REF}$ | $-2 \times V_{REF}$ to $+2 \times V_{REF}$ | Not applicable                                       |

| 1                                     | 1          | 0 V to V <sub>REF</sub>            | $-V_{REF}$ to $+V_{REF}$                   | Not applicable                                       |

<sup>&</sup>lt;sup>1</sup> For more information, see the ADC Sampling Mode Subregister (Address 0x12) section.

$<sup>^2</sup>$  The contents of the VIN RANGE0 and VIN RANGE1 subregisters are ignored when the AD7292 is configured to sample with respect to AV<sub>DD</sub>; the only input range allowed when sampling with respect to AV<sub>DD</sub> is from (AV<sub>DD</sub> –  $4 \times V_{REF}$ ) to AV<sub>DD</sub>.

Figure 34. Straight Binary Transfer Characteristic Corresponding to Single-Ended Input Range of 0 V to V<sub>RFF</sub>

Table 11. Output Codes and Ideal Input Voltages ( $AV_{DD} = 5 \text{ V}$ )

|                  | Analog Input Range             |                                |                         |                                               |                                                                                  |                                                     |                                        |                              |

|------------------|--------------------------------|--------------------------------|-------------------------|-----------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------|------------------------------|

|                  | 9                              | Single-Ended                   | Mode of Oper            | ation                                         | Differe                                                                          | ntial Mode of O                                     |                                        |                              |

| Description      | 0 V to<br>4 × V <sub>REF</sub> | 0 V to<br>2 × V <sub>REF</sub> | 0 V to V <sub>REF</sub> | $ (AV_{DD} - 4 \times V_{REF}) $ to $AV_{DD}$ | $\begin{array}{c} -4 \times V_{REF} \text{ to} \\ +4 \times V_{REF} \end{array}$ | $-2 \times V_{REF} \text{ to} \\ +2 \times V_{REF}$ | -V <sub>REF</sub> to +V <sub>REF</sub> | Digital Output<br>Code (Hex) |

| +FSR – 1 LSB     | 4.995117 V                     | 2.497559 V                     | 1.248779 V              | 4.995117 V                                    | 4.990234 V                                                                       | 2.495117 V                                          | 1.247559 V                             | 0x3FF                        |

| Midscale + 1 LSB | 2.504883 V                     | 1.252441 V                     | 0.626221 V              | 2.504883 V                                    | 0.009766 V                                                                       | 0.004883 V                                          | 0.002441 V                             | 0x201                        |

| Midscale         | 2.5 V                          | 1.25 V                         | 0.625 V                 | 2.5 V                                         | 0 V                                                                              | 0 V                                                 | 0 V                                    | 0x200                        |

| Midscale – 1 LSB | 2.495117 V                     | 1.247559 V                     | 0.623779 V              | 2.495117 V                                    | -0.009766 V                                                                      | -0.004883 V                                         | -0.002441 V                            | 0x1FF                        |

| -FSR + 1 LSB     | 0.004883 V                     | 0.002441 V                     | 0.001221 V              | 0.004883 V                                    | 4.995117 V                                                                       | -2.495117 V                                         | -1.247559 V                            | 0x001                        |

| –FSR             | 0 V                            | 0 V                            | 0 V                     | 0 V                                           | −5 V                                                                             | −2.5 V                                              | −1.25 V                                | 0x000                        |

### **TEMPERATURE SENSOR**

The AD7292 contains one local temperature sensor. The on-chip, band gap temperature sensor measures the temperature of the AD7292 die. The temperature sensor input gathers data and computes a value over a period of several hundred microseconds. The temperature measurement takes place continuously in the background, leaving the user free to perform conversions on the other channels.

After a temperature value is computed, a signal passes to the control logic to initiate a conversion automatically. If an ADC conversion is in progress, the temperature sensor conversion is performed as soon as the ADC conversion is completed. If the ADC is idle, the temperature sensor conversion takes place immediately.

The  $T_{\text{SENSE}}$  conversion result register stores the result of the last conversion on the temperature channel; this result can be read at any time provided that the temperature sensor is enabled via the temperature sensor subregister within the configuration register bank (see the Temperature Sensor Subregister (Address 0x20) section).

Temperature readings from the ADC are stored in the  $T_{\text{SENSE}}$  conversion result register. Results are in 14-bit straight binary format and accommodate both positive and negative temperature measurements. Bit D0 and Bit D1 hold alert flags; Bit D2 stores the LSB, which corresponds to 0.03125°C if the digital filter is enabled.

Table 12 provides examples of temperature sensor data. An output of all 0s is equal to  $-256^{\circ}$ C; this value is output by the AD7292 until the first measurement is completed. Note that when digital filtering is disabled, Bit D3 and Bit D2 of the  $T_{\text{SENSE}}$  conversion result register are set to 0, producing a 12-bit straight binary result with an LSB of 0.125°C. When the  $T_{\text{SENSE}}$  conversion result is read via the ADC data register (Address 0x01), the temperature sensor result is a 10-bit result with an LSB that equates to 0.5°C.

Table 12. Temperature Sensor Data Format

|                  | T <sub>SENSE</sub> Conversion Result Register, |

|------------------|------------------------------------------------|

| Temperature (°C) | Bits[D15:D2]                                   |

| -40              | 01 1011 0000 0000                              |

| -25              | 01 1100 1110 0000                              |

| -10              | 01 1110 1100 0000                              |

| -0.03125         | 01 1111 1111 1111                              |

| 0                | 10 0000 0000 0000                              |

| +0.03125         | 10 0000 0000 0001                              |

| +10              | 10 0001 0100 0000                              |

| +25              | 10 0011 0010 0000                              |

| +50              | 10 0110 0100 0000                              |

| +75              | 10 1001 0110 0000                              |

| +100             | 10 1100 1000 0000                              |

| +125             | 10 1111 1010 0000                              |

### **DAC OPERATION**

The four DACs of the AD7292 provide digital control with 10 bits of resolution. DAC outputs VOUT0 to VOUT3 feature an output voltage range up to 5 V (LSB of 4.88 mV).

The DAC output buffer can be controlled via software using the GPIO2/DAC DISABLE0 and GPIO4/DAC DISABLE1 subregisters within the configuration register bank, or via hardware using the GPIO2/DAC DISABLE0 and GPIO4/DAC DISABLE1 pins.

#### **DIGITAL I/O PINS**

To aid in system monitoring, the AD7292 features 12 digital I/O pins. All 12 pins can be configured as GPIO pins. Six of the digital I/O pins can be configured for other functionality; on power-up, the non-GPIO functionality of these six pins is enabled by default. For more information, see the Digital Output Driver Subregister (Address 0x01) section and the Digital I/O Function Subregister (Address 0x02) section.

#### **GPIO0/ALERTO and GPIO1/ALERT1 Pins**

When Pin 27 and Pin 26 (GPIO0/ALERT0 and GPIO1/ALERT1, respectively) are configured as alert pins, they act as out-of-range indicators that become active when the selected conversion result exceeds the high or low limit stored in the alert limits register bank. The polarity of the alert output pins can be set to active high or active low via the general subregister within the configuration register bank (see the General Subregister (Address 0x08) section).

#### GPIO2/DAC DISABLEO and GPIO4/DAC DISABLE1 Pins

When Pin 25 and Pin 23 (GPIO2/DAC DISABLE0 and GPIO4/DAC DISABLE1, respectively) are configured as DAC disable pins, they can be used to power down the selected DAC outputs, as determined by the contents of the GPIO2/DAC DISABLE0 and GPIO4/DAC DISABLE1 subregisters within the configuration register bank. For more information, see the GPIO2/DAC DISABLE0 and GPIO4/DAC DISABLE1 Subregisters (Address 0x30 and Address 0x31) section.

#### **GPIO3/LDAC Pin**

When Pin 24 (GPIO3/LDAC) is configured as an LDAC pin, the DAC registers are updated when this input pin is taken high.

### **GPIO6/BUSY Pin**

Pin 21 (GPIO6/BUSY) can be configured as a general-purpose input/output or as a busy output pin. When configured as a busy output pin, this pin transitions high when a conversion starts and remains high until the conversion is completed.

### **SERIAL PORT INTERFACE (SPI)**

The AD7292 serial port interface (SPI) allows the user to configure the device for specific functions and operations through an internal structured register space. The interface consists of four signals:  $\overline{\text{CS}}$ , SCLK, DIN, and DOUT. The SPI reference level is set by Pin 5 ( $V_{\text{DRIVE}}$ ) to a level in the range of 1.8 V to 5.25 V.

SCLK is the serial clock input for the device; all data transfers on DIN or  $\overrightarrow{DOUT}$  take place with respect to SCLK. The chip select input pin  $(\overrightarrow{CS})$  is an active low control that initiates the data transfer and conversion process.

Data is clocked into the AD7292 on the SCLK falling edge. Data is loaded into the device MSB first. The length of each frame can vary and depends on the command being sent. Data is clocked out of the AD7292 on DOUT in the same frame as the read command, on the rising edge of SCLK while  $\overline{\text{CS}}$  is low. When  $\overline{\text{CS}}$  is high, the SCLK and DIN signals are ignored and the DOUT line becomes high impedance.

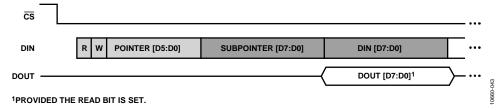

### INTERFACE PROTOCOL

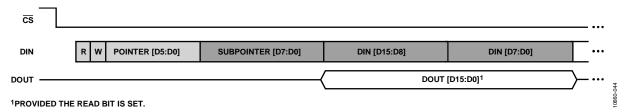

When reading from or writing to the AD7292, the first byte contains the address pointer (see Table 13). Bit D7 and Bit D6 of the address pointer are the read and write bits, respectively. Bit D5 to Bit D0 of the address pointer specify the register address for the read or write operation. A register can be simultaneously read from and written to by setting both Bit D7 and Bit D6 to 1.

Table 13. Address Pointer

| D7 | D6 | D5 | D4 | D3      | D2       | D1 | D0 |

|----|----|----|----|---------|----------|----|----|

| R  | W  |    |    | Registe | r select |    |    |

After the address pointer, subsequent data for writing to the part is supplied in bytes (see Figure 36). Some registers are located within register banks and, therefore, require both a pointer address and a subpointer address. The subpointer address is specified in the first byte following the pointer address (see Figure 37). Figure 36 through Figure 38 show the read and write data formats. These figures show read operations; for a write to a register or subregister, the write bit is set and the DOUT line remains high impedance.

If neither the read nor write bit is set (Bit D7 and Bit D6 of the address pointer are set to 0), the address pointer is updated but no data is read or written. Note that writing this command also reinitializes the ADC sequencer (see the ADC Conversion Control section).

On completion of a read or write, the  $\overline{\text{CS}}$  pin can be taken high to terminate the operation.

DOUT [D15:D0]1

<sup>1</sup>PROVIDED THE READ BIT IS SET.

ดร

DIN

DOUT

Figure 36. Accessing a 16-Bit Register

Figure 37. Accessing an 8-Bit Subregister Within a Register Bank

Figure 38. Accessing a 16-Bit Subregister Within a Register Bank

### **REGISTER STRUCTURE**

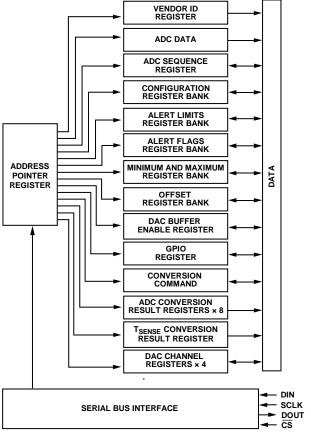

The AD7292 contains internal registers that store conversion results, high and low conversion limits, and information to configure and control the device (see Figure 39). Each register has an address; the address pointer register points to the address when communicating with the register. Some registers and subregisters contain reserved bits. The AD7292 allows either a 0 or a 1 to be written to these reserved bits.

Figure 39. AD7292 Register Structure

Table 14 lists each register and specifies whether the register has read access or read and write access.

Table 14. AD7292 Registers

| Address | Register Name                                 | Access <sup>1</sup> | Data<br>Format |

|---------|-----------------------------------------------|---------------------|----------------|

| 0x00    | Vendor ID register                            | R                   | Figure 36      |

| 0x01    | ADC data register                             | R                   | Figure 36      |

| 0x03    | ADC sequence register                         | R/W                 | Figure 36      |

| 0x05    | Configuration register bank                   | R/W                 | Figure 38      |

| 0x06    | Alert limits register bank                    | R/W                 | Figure 38      |

| 0x07    | Alert flags register bank                     | R/W                 | Figure 38      |

| 0x08    | Minimum and maximum register bank             | R/W                 | Figure 38      |

| 0x09    | Offset register bank                          | R/W                 | Figure 37      |

| 0x0A    | DAC buffer enable register                    | R/W                 | Figure 36      |

| 0x0B    | GPIO register                                 | R/W                 | Figure 36      |

| 0x0E    | Conversion command <sup>2</sup>               | N/A                 | N/A            |

| 0x10    | ADC conversion result register,<br>Channel 0  | R                   | Figure 36      |

| 0x11    | ADC conversion result register,<br>Channel 1  | R                   | Figure 36      |

| 0x12    | ADC conversion result register,<br>Channel 2  | R                   | Figure 36      |

| 0x13    | ADC conversion result register,<br>Channel 3  | R                   | Figure 36      |

| 0x14    | ADC conversion result register,<br>Channel 4  | R                   | Figure 36      |

| 0x15    | ADC conversion result register,<br>Channel 5  | R                   | Figure 36      |

| 0x16    | ADC conversion result register,<br>Channel 6  | R                   | Figure 36      |

| 0x17    | ADC conversion result register,<br>Channel 7  | R                   | Figure 36      |

| 0x20    | T <sub>SENSE</sub> conversion result register | R                   | Figure 36      |

| 0x30    | DAC Channel 0 register                        | R/W                 | Figure 36      |

| 0x31    | DAC Channel 1 register                        | R/W                 | Figure 36      |

| 0x32    | DAC Channel 2 register                        | R/W                 | Figure 36      |

| 0x33    | DAC Channel 3 register                        | R/W                 | Figure 36      |

<sup>&</sup>lt;sup>1</sup> R is read only; R/W is read/write.

<sup>&</sup>lt;sup>2</sup> See the ADC Conversion Command section for more information.

# REGISTER DESCRIPTIONS VENDOR ID REGISTER (ADDRESS 0x00)

The 16-bit, read-only vendor ID register stores the Analog Devices vendor ID, 0x0018. The vendor ID register is provided to identify the AD7292 to an SPI master such as a microcontroller.

### **ADC DATA REGISTER (ADDRESS 0x01)**

The 16-bit, read-only ADC data register provides read access to the most recent ADC conversion result. This register provides 10 bits of conversion data, four channel identifier bits, and two alert bits (see the ADC Conversion Control section).

### **ADC SEQUENCE REGISTER (ADDRESS 0x03)**

The 16-bit, read/write ADC sequence register allows the user to specify a preprogrammed sequence of ADC channels for conversion. The ADC converts on each of the specified ADC channels in turn. For more information, see the ADC Conversion Control section. Table 16 describes the register bit functions. Bit D15 is the first bit in the data stream. On power-up, the ADC sequence register contains all 0s by default.

Temperature sensor results can be inserted into the sequence by writing a 1 to Bit D8 of the ADC sequence register, provided that the temperature sensor has been enabled in the temperature sensor subregister within the configuration register bank (see the Temperature Sensor Subregister (Address 0x20) section).

### **CONFIGURATION REGISTER BANK (ADDRESS 0x05)**

The configuration register bank subregisters are listed in Table 15. On power-up, the subregisters within the configuration register bank contain all 0s by default.

**Table 15. Configuration Register Bank Subregisters**

| Subaddress (Hex) | Subregister Name <sup>1</sup>    |

|------------------|----------------------------------|

| 0x01             | Digital output driver            |

| 0x02             | Digital I/O function             |

| 0x08             | General                          |

| 0x10             | VIN RANGE0                       |

| 0x11             | VIN RANGE1                       |

| 0x12             | ADC sampling mode                |

| 0x13             | VIN ALERT0 routing               |

| 0x14             | VIN ALERT1 routing               |

| 0x15             | VIN filter                       |

| 0x16             | Conversion delay control         |

| 0x20             | Temperature sensor               |

| 0x21             | Temperature sensor alert routing |

| 0x30             | GPIO2/DAC DISABLE0               |

| 0x31             | GPIO4/DAC DISABLE1               |

<sup>&</sup>lt;sup>1</sup> All subregisters in the configuration register bank are read/write.

Table 16. ADC Sequence Register, Bit Function Descriptions

| Bits     | Bit Name                           | R/W | Description                                                                       |

|----------|------------------------------------|-----|-----------------------------------------------------------------------------------|

| [D15:D9] | Reserved                           | R/W | Reserved                                                                          |

| D8       | T <sub>SENSE</sub> readback enable | R/W | 0 = disable T <sub>SENSE</sub> readback<br>1 = enable T <sub>SENSE</sub> readback |

| D7       | ADC Channel 7 convert              | R/W | 0 = disable conversion of Channel 7<br>1 = enable conversion of Channel 7         |

| D6       | ADC Channel 6 convert              | R/W | 0 = disable conversion of Channel 6<br>1 = enable conversion of Channel 6         |

| D5       | ADC Channel 5 convert              | R/W | 0 = disable conversion of Channel 5<br>1 = enable conversion of Channel 5         |

| D4       | ADC Channel 4 convert              | R/W | 0 = disable conversion of Channel 4<br>1 = enable conversion of Channel 4         |

| D3       | ADC Channel 3 convert              | R/W | 0 = disable conversion of Channel 3<br>1 = enable conversion of Channel 3         |