# 1.65 GHz Clock Fanout Buffer with Output Dividers and Delay Adjust

# **Data Sheet**

### FEATURES

1.65 GHz differential clock inputs/outputs

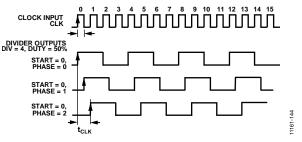

10-bit programmable dividers, 1 to 1024, all integers

Up to 4 differential outputs or 8 CMOS outputs

Pin strapping capability for hardwired programming at power-up

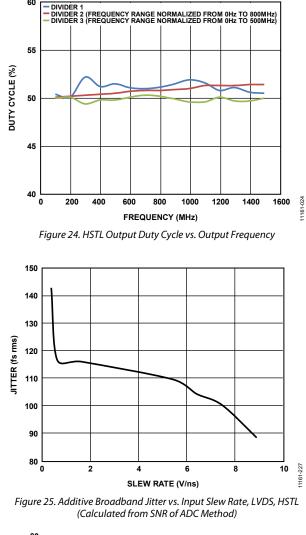

<115 fs rms broadband random jitter (see Figure 25)</li>

Additive output jitter: 41 fs rms typical (12 kHz to 20 MHz) Excellent output-to-output isolation

Automatic synchronization of all outputs

Single 2.5 V/3.3 V power supply

Internal LDO (low drop-out) voltage regulator for enhanced power supply immunity

Phase offset select for output-to-output coarse delay adjust 3 programmable output logic levels, LVDS, HSTL, and CMOS Serial control port (SPI/I<sup>2</sup>C) or pin-programmable mode Space-saving 24-lead LFCSP

#### **APPLICATIONS**

Low jitter, low phase noise clock distribution Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers High performance instrumentation Broadband infrastructure

#### **GENERAL DESCRIPTION**

The AD9508 provides clock fanout capability in a design that emphasizes low jitter to maximize system performance. This device benefits applications like clocking data converters with demanding phase noise and low jitter requirements.

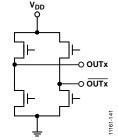

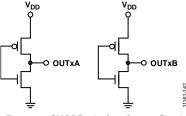

There are four independent differential clock outputs, each with various types of logic levels available. Available logic types include LVDS (1.65 GHz), HSTL (1.65 GHz), and 1.8 V CMOS (250 MHz). In 1.8 V CMOS output mode, the differential output becomes two CMOS single-ended signals. The CMOS outputs are 1.8 V logic levels, regardless of the operating supply voltage.

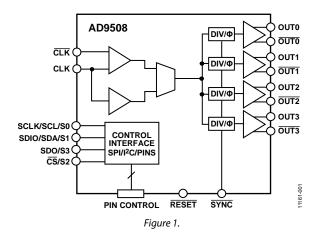

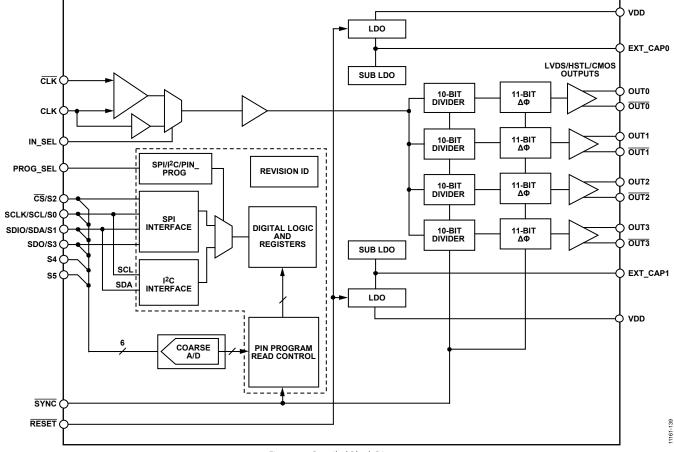

### FUNCTIONAL BLOCK DIAGRAM

**AD9508**

Each output has a programmable divider that can be bypassed or be set to divide by any integer up to 1024. In addition, the AD9508 supports a coarse output phase adjustment between the outputs.

The device can also be pin programmed for various fixed configurations at power-up without the need for SPI or I<sup>2</sup>C programming.

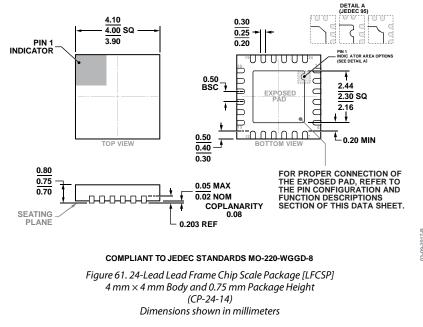

The AD9508 is available in a 24-lead LFCSP and operates from a either a single 2.5 V or 3.3 V supply. The temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Rev. G

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features 1                                       |

|--------------------------------------------------|

| Applications1                                    |

| Functional Block Diagram1                        |

| General Description                              |

| Revision History                                 |

| Specifications                                   |

| Electrical Characteristics                       |

| Power Supply Current and Temperature Conditions  |

| Clock Inputs and Output DC Specifications        |

| Output Driver Timing Characteristics             |

| Logic Inputs7                                    |

| Serial Port Specifications—SPI Mode7             |

| Serial Port Specifications—I <sup>2</sup> C Mode |

| External Resistor Values For Pin Strapping Mode9 |

| Clock Output Additive Phase Noise                |

| Clock Output Additive Time Jitter10              |

| Absolute Maximum Ratings11                       |

| Thermal Characteristics11                        |

| ESD Caution11                                    |

| Pin Configuration and Function Descriptions12    |

| Typical Performance Characteristics14            |

| Test Circuits                                    |

| Input/Output Termination Recommendations         |

| Terminology                                      |

| Theory of Operation                              |

| Detailed Block Diagram22                         |

| Programming Mode Selection22                     |

| Clock Input                                           | 23 |

|-------------------------------------------------------|----|

| Clock Outputs                                         | 24 |

| Clock Dividers                                        | 24 |

| Phase Delay Control                                   | 24 |

| Reset Modes                                           | 25 |

| Power-Down Mode                                       | 25 |

| Output Clock Synchronization                          | 25 |

| Power Supply                                          | 25 |

| Thermally Enhanced Package Mounting Guidelines        | 25 |

| Pin Strapping to Program on Power-Up                  | 26 |

| Serial Control Port                                   | 27 |

| SPI/I <sup>2</sup> C Port Selection                   | 27 |

| SPI Serial Port Operation                             | 27 |

| I <sup>2</sup> C Serial Port Operation                | 30 |

| Register Map                                          | 33 |

| Register Map Bit Descriptions                         | 34 |

| Serial Port Configuration (Register 0x00)             | 34 |

| Silicon Revision (Register 0x0A to Register 0x0D)     | 34 |

| Chip Level Functions (Register 0x12 to Register 0x14) | 34 |

| OUT0 Functions (Register 0x15 to Register 0x1A)       | 35 |

| OUT1 Functions (Register 0x1B to Register 0x20)       | 36 |

| OUT2 Functions (Register 0x21 to Register 0x26)       | 37 |

| OUT3 Functions (Register 0x27 to Register 0x2C)       | 38 |

| Packaging and Ordering Information                    | 40 |

| Outline Dimensions                                    | 40 |

| Ordering Guide                                        | 40 |

### **REVISION HISTORY**

| 6/2017—Rev. F to Rev. G    |    |

|----------------------------|----|

| Updated Outline Dimensions | 40 |

| Changes to Ordering Guide  | 40 |

#### 4/2015—Rev. E to Rev. F

| Changes to Clock Outputs Section | 24 |

|----------------------------------|----|

| Changes to Table 28              | 35 |

| Changes to Table 30              |    |

| Changes to Table 32              |    |

| Changes to Table 34              |    |

#### 11/2014—Rev. D to Rev. E

| Changes to Figure 11                                          |

|---------------------------------------------------------------|

| Moved Revision History Section                                |

| Changes to Table 1212                                         |

| Changes to Clock Outputs Section, Clock Dividers Section, and |

| Phase Delay Control Section24                                 |

| Changed Individual Clock Channel Power-Down Section to        |

| Individual Clock Divider Power-Down Section25                 |

| Changes to Individual Clock Divider Power-Down Section and    |

| Output Clock Synchronization Section25                        |

| Changes to Pin Strapping to Program on Power-up Section and   |

| Table 15                                                      |

| Changes to Table 27 and Table 28                              |

| Changes to Table 29 and Table 30                              |

| Changes to Table 31 and Table 32                              |

| Changes to Table 33                                           |

| Changes to Table 34                                           |

|                                                               |

### 9/2014—Rev. C to Rev. D

| Changes to Table 1                                        | .3 |

|-----------------------------------------------------------|----|

| Changes to Table 2                                        | .4 |

| Changes to Figure 37 Caption; Added Figure 38; Renumbered |    |

| Sequentially1                                             | 9  |

| Changes to Clock Input Section and Table 142              | 23 |

#### 2/2014—Rev. B to Rev. C

| Changes to Table 14 |

|---------------------|

|---------------------|

#### 10/2013—Rev. A to Rev. B

| Change to Figure 5 Caption                              |

|---------------------------------------------------------|

| Change to Figure 13 Caption14                           |

| Change to Figure 19 Caption15                           |

| Change to Individual Clock Channel Power-Down Section23 |

| Change to Write Section27                               |

| Changes to Table 27                                     |

| Changes to Table 29                                     |

| Changes to Table 31                                     |

| Changes to Table 33                                     |

#### 4/2013—Rev. 0 to Rev. A

| Changes to Ta  | ble 9                           | 9  |

|----------------|---------------------------------|----|

| Changes to Fig | gure 10                         |    |

| Changes to Fig | gure 15                         |    |

| Changes to Fig | gure 24 and Figure 26           | 16 |

| Changes to Fig | gure 27, Figure 29 to Figure 32 | 17 |

| Changes to Fig | gure 33                         |    |

1/2013—Revision 0: Initial Version

# **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

Typical values are given for  $V_S = 3.3$  V and 2.5 V and  $T_A = 25^{\circ}$ C; minimum and maximum values are given over the full  $V_{DD} = 3.3$  V + 5% down to 2.5 V - 5% and  $T_A = -40^{\circ}$ C to +85°C variation; and input slew rate > 1 V/ns, unless otherwise noted.

### POWER SUPPLY CURRENT AND TEMPERATURE CONDITIONS

| Parameter                                 | Min   | Тур | Мах   | Unit | Test Conditions/Comments                                                                                                                                                                    |

|-------------------------------------------|-------|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY VOLTAGE                            | 2.375 | 2.5 | 3.465 | V    | Use supply voltage setting (2.5 V or 3.3 V) and<br>appropriate current consumption configuration<br>(see Current Consumption parameters in Table 1)<br>to calculate total power dissipation |

| CURRENT CONSUMPTION                       |       |     |       |      |                                                                                                                                                                                             |

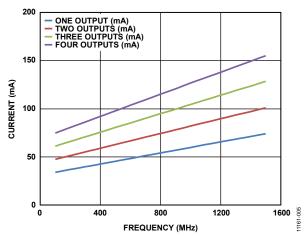

| LVDS Configuration                        |       | 165 | 182   | mA   | Input clock: 1500 MHz in differential mode, all LVDS output drivers at 1500 MHz                                                                                                             |

|                                           |       | 122 | 134   | mA   | Input clock: 800 MHz in differential mode, all LVDS output drivers at 200 MHz                                                                                                               |

| HSTL Configuration                        |       | 194 | 213   | mA   | Input clock: 1500 MHz in differential mode, all<br>HSTL output drivers at 1500 MHz                                                                                                          |

|                                           |       | 131 | 144   | mA   | Input clock: 491.52 MHz in differential mode, all output drivers at 491.52 MHz                                                                                                              |

|                                           |       | 92  | 101   | mA   | Input clock: 122.88 MHz in differential mode, all output drivers at 122.88 MHz                                                                                                              |

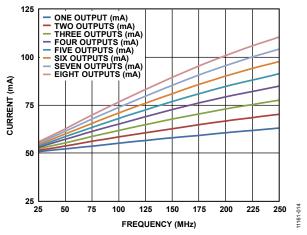

| CMOS Configuration                        |       | 141 | 185   | mA   | Input clock: 1500 MHz in differential mode, all<br>CMOS output drivers at 250 MHz, 10 pF load                                                                                               |

|                                           |       | 122 | 134   | mA   | Input clock: 800 MHz in differential mode, all CMOS outputs drivers at 200 MHz, 10 pF load                                                                                                  |

|                                           |       | 85  | 94    | mA   | Input clock: 100 MHz in differential mode, all CMOS outputs drivers at 100 MHz, 10 pF load                                                                                                  |

| Full Power-Down                           |       | 6   | 10    | mA   |                                                                                                                                                                                             |

| TEMPERATURE                               |       |     |       |      |                                                                                                                                                                                             |

| Ambient Temperature Range, T <sub>A</sub> | -40   | +25 | +85   | °C   |                                                                                                                                                                                             |

| Junction Temperature, T                   |       |     | 115   | ℃    | Junction temperatures above 115°C can<br>degrade performance but no damage should<br>occur, unless the absolute temperature is<br>exceeded                                                  |

# CLOCK INPUTS AND OUTPUT DC SPECIFICATIONS

#### Table 2.

| Parameter                              | Symbol                 | Min          | Тур  | Max          | Unit   | Test Conditions/Comments                                                                                                                                             |

|----------------------------------------|------------------------|--------------|------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK INPUTS                           |                        |              |      |              |        |                                                                                                                                                                      |

| Differential Mode                      |                        |              |      |              |        |                                                                                                                                                                      |

| Input Frequency                        |                        | 0            |      | 1650         | MHz    | Differential input                                                                                                                                                   |

| Input Sensitivity                      |                        | 360          |      | 2200         | mV p-p | As measured with a differential probe; jitter performance improves with higher slew rates (greater voltage swing)                                                    |

| Input Common-Mode Voltage              | V <sub>ICM</sub>       | 0.95         | 1.05 | 1.15         | v      | Input pins are internally self biased, which enables ac coupling                                                                                                     |

| Input Voltage Offset                   |                        |              | 30   |              | mV     |                                                                                                                                                                      |

| DC-Coupled Input Common-<br>Mode Range | V <sub>CMR</sub>       | 0.58         |      | 1.67         | V      | This is the allowable common-mode<br>voltage range when dc-coupled                                                                                                   |

| Pulse Width                            |                        |              |      |              |        |                                                                                                                                                                      |

| Low                                    |                        | 303          |      |              | ps     |                                                                                                                                                                      |

| High                                   |                        | 303          |      |              | ps     |                                                                                                                                                                      |

| Input Resistance (Single-Ended)        |                        | 5.0          | 7    | 9            | kΩ     |                                                                                                                                                                      |

| Input Capacitance                      | CIN                    |              | 2    |              | pF     |                                                                                                                                                                      |

| Input Bias Current (Each Pin)          |                        | 100          |      | 400          | μA     | Full input swing                                                                                                                                                     |

| CMOS CLOCK MODE (SINGLE-ENDED)         |                        |              |      |              |        | 2.5 V or 3.3 V CMOS only; for 1.8 V CMOS, use (ac-coupled) differential input mode                                                                                   |

| Input Frequency                        |                        |              |      | 250          | MHz    |                                                                                                                                                                      |

| Input Voltage                          |                        |              |      |              |        |                                                                                                                                                                      |

| High                                   | VIH                    | VDD/2 + 0.15 |      |              | V      |                                                                                                                                                                      |

| Low                                    | VIL                    |              |      | VDD/2 - 0.15 | V      |                                                                                                                                                                      |

| Input Current                          |                        |              |      |              |        |                                                                                                                                                                      |

| High                                   | I <sub>INH</sub>       |              | 1    |              | μA     |                                                                                                                                                                      |

| Low                                    | I <sub>INL</sub>       |              | -142 |              | μA     |                                                                                                                                                                      |

| Input Capacitance                      | CIN                    |              | 2    |              | pF     |                                                                                                                                                                      |

| LVDS CLOCK OUTPUTS                     |                        |              |      |              |        | Termination = 100 $\Omega$ differential (OUTx, $\overline{OUTx}$ )                                                                                                   |

| Output Frequency                       |                        |              |      | 1650         | MHz    |                                                                                                                                                                      |

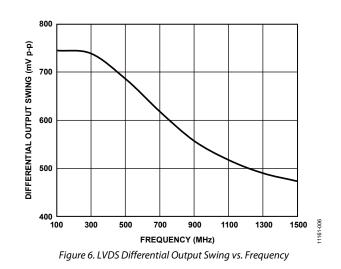

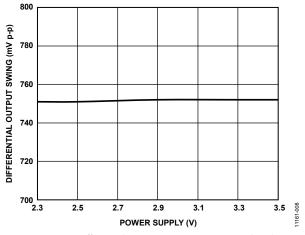

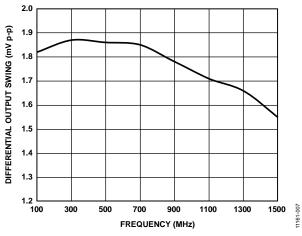

| Output Voltage Differential            | Vod                    | 247          | 375  | 454          | mV     | $V_{OH} - V_{OL}$ measurement across a differential pair at the default amplitude setting with output driver not toggling; see Figure 6 for variation over frequency |

| Delta $V_{\text{OD}}$                  | $\Delta V_{\text{OD}}$ |              |      | 50           | mV     | This is the absolute value of the difference<br>between $V_{OD}$ when the normal output is high<br>vs. when the complementary output is high                         |

| Offset Voltage                         | Vos                    | 1.125        | 1.18 | 1.375        | v      | $(V_{OH} + V_{OL})/2$ across a differential pair                                                                                                                     |

| Delta Vos                              | ΔVos                   | 1.125        | 1.10 | 50           | mV     | This is the absolute value of the difference between $V_{\text{OS}}$ when the normal output is high                                                                  |

|                                        |                        |              | 12.5 | 24           |        | vs. when the complementary output is high                                                                                                                            |

| Short-Circuit Current                  | IsA, IsB               |              | 13.6 | 24           | mA     | Each pin (output shorted to GND)                                                                                                                                     |

| LVDS Duty Cycle                        |                        | 45           |      | 55           | %      | Up to 750 MHz input                                                                                                                                                  |

|                                        |                        | 39           |      | 61           | %      | 750 MHz to1500 MHz input                                                                                                                                             |

|                                        |                        |              | 50.1 |              | %      | 1650 MHz input                                                                                                                                                       |

| HSTL CLOCK OUTPUTS                     |                        |              |      |              |        | 100 $\Omega$ across differential pair; default amplitude setting                                                                                                     |

| Output Frequency                       | 1                      |              |      | 1650         | MHz    |                                                                                                                                                                      |

| Differential Output Voltage            | Vo                     | 859          | 925  | 978          | mV     | $V_{OH} - V_{OL}$ with output driver static                                                                                                                          |

| Common-Mode Output Voltage             | Vocm                   | 905          | 940  | 971          | mV     | $(V_{OH} + V_{OL})/2$ with output driver static                                                                                                                      |

| HSTL Duty Cycle                        |                        | 45           |      | 55           | %      | Up to 750 MHz input                                                                                                                                                  |

|                                        |                        | 40           |      | 60           | %      | 750 MHz to 1500 MHz input                                                                                                                                            |

|                                        |                        |              | 50.9 |              | %      | 1650 MHz input                                                                                                                                                       |

| Parameter                     | Symbol          | Min  | Тур | Max  | Unit | Test Conditions/Comments                                             |

|-------------------------------|-----------------|------|-----|------|------|----------------------------------------------------------------------|

| CMOS CLOCK OUTPUTS            |                 |      |     |      |      | Sing <u>le-end</u> ed; termination = open; OUTx<br>and OUTx in phase |

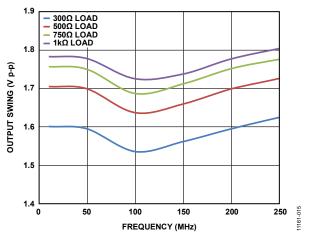

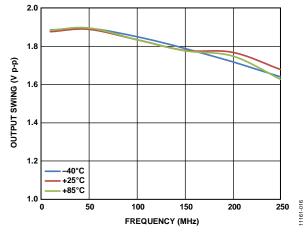

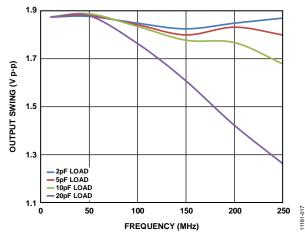

| Output Frequency              |                 |      |     | 250  | MHz  | With 10 pF load per output, see Figure 14 for swing vs. frequency    |

| Output Voltage                |                 |      |     |      |      |                                                                      |

| At 1 mA Load                  |                 |      |     |      |      |                                                                      |

| High                          | Vон             | 1.7  |     |      | V    |                                                                      |

| Low                           | Vol             |      |     | 0.1  | V    |                                                                      |

| At 10 mA load                 |                 |      |     |      |      |                                                                      |

| High                          | Vон             | 1.2  |     |      | V    |                                                                      |

| Low                           | Vol             |      |     | 0.6  | V    |                                                                      |

| At 10 mA Load (2 × CMOS Mode) |                 |      |     |      |      |                                                                      |

| High                          | V <sub>OH</sub> | 1.45 |     |      | V    |                                                                      |

| Low                           | Vol             |      |     | 0.35 | V    |                                                                      |

| CMOS Duty Cycle               |                 | 45   |     | 55   | %    | Up to 250 MHz                                                        |

### **OUTPUT DRIVER TIMING CHARACTERISTICS**

| Parameter                               | Symbol                          | Min  | Тур  | Мах  | Unit  | Test Conditions/Comments                                                                                                                |

|-----------------------------------------|---------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| LVDS OUTPUTS                            |                                 |      |      |      |       | Termination = $100 \Omega$ differential, $1 \times LVDS$                                                                                |

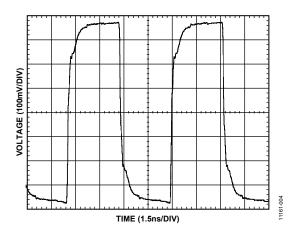

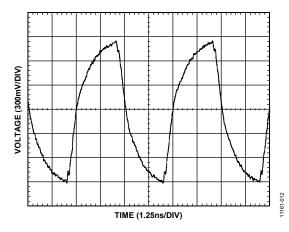

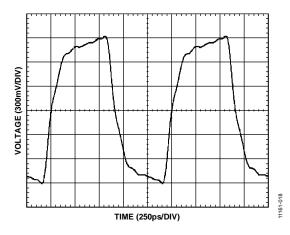

| Output Rise/Fall Time                   | t <sub>R</sub> , t <sub>F</sub> |      | 152  | 177  | ps    | 20% to 80% measured differentially                                                                                                      |

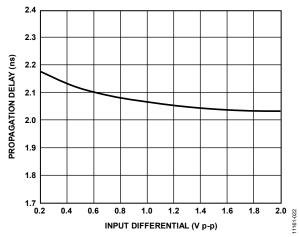

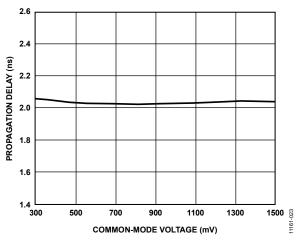

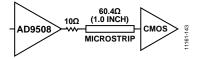

| Propagation Delay, Clock-to-LVDS Output | <b>t</b> PD                     | 1.56 | 2.01 | 2.43 | ns    |                                                                                                                                         |

| Temperature Coefficient                 |                                 |      | 2.8  |      | ps/°C |                                                                                                                                         |

| Output Skew <sup>1</sup>                |                                 |      |      |      |       |                                                                                                                                         |

| All LVDS Outputs                        |                                 |      |      |      |       |                                                                                                                                         |

| On the Same Part                        |                                 |      |      | 48   | ps    |                                                                                                                                         |

| Across Multiple Parts                   |                                 |      |      | 781  | ps    | Assumes same temperature and supply;<br>takes into account worst-case propagation<br>delay delta due to worst-case process<br>variation |

| HSTL OUTPUTS                            |                                 |      |      |      |       | Termination = $100 \Omega$ differential, $1 \times HSTL$                                                                                |

| Output Rise/Fall Time                   | t <sub>R</sub> , t <sub>F</sub> |      | 118  | 143  | ps    | 20% to 80% measured differentially                                                                                                      |

| Propagation Delay, Clock-to-HSTL Output | <b>t</b> PD                     | 1.59 | 2.05 | 2.5  | ns    |                                                                                                                                         |

| Temperature Coefficient                 |                                 |      | 2.9  |      | ps/°C |                                                                                                                                         |

| Output Skew <sup>1</sup>                |                                 |      |      |      |       |                                                                                                                                         |

| All HSTL Outputs                        |                                 |      |      |      |       |                                                                                                                                         |

| On the Same Part                        |                                 |      |      | 59   | ps    |                                                                                                                                         |

| Across Multiple Parts                   |                                 |      |      | 825  | ps    | Assumes same temperature and supply;<br>takes into account worst-case propagation<br>delay delta due to worst-case process<br>variation |

| CMOS OUTPUTS                            |                                 |      |      |      |       |                                                                                                                                         |

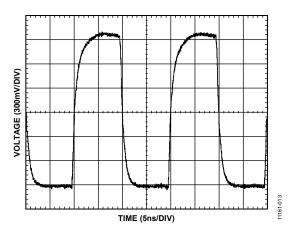

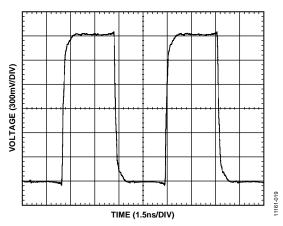

| Output Rise/Fall Time                   | t <sub>R</sub> , t <sub>F</sub> |      | 1.18 | 1.45 | ns    | 20% to 80%; $C_{LOAD} = 10 \text{ pF}$                                                                                                  |

| Propagation Delay, Clock-to-CMOS Output | <b>t</b> PD                     | 2.04 | 2.56 | 3.07 | ns    | 10 pF load                                                                                                                              |

| Temperature Coefficient                 |                                 |      | 3.3  |      | ps/°C |                                                                                                                                         |

| Output Skew <sup>1</sup>                |                                 |      |      |      |       |                                                                                                                                         |

| All CMOS Outputs                        |                                 |      |      |      |       |                                                                                                                                         |

| On the Same Part                        |                                 |      |      | 112  | ps    |                                                                                                                                         |

| Across Multiple Parts                   |                                 |      |      | 965  | ps    | Assumes same temperature and supply;<br>takes into account worst-case propagation<br>delay delta due to worst-case process<br>variation |

# **Data Sheet**

# AD9508

| Parameter                         | Symbol | Min | Тур | Max | Unit | Test Conditions/Comments                                          |

|-----------------------------------|--------|-----|-----|-----|------|-------------------------------------------------------------------|

| OUTPUT LOGIC SKEW <sup>1</sup>    |        |     |     |     |      | CMOS load = 10 pF and LVDS load = $100 \Omega$                    |

| LVDS Output(s) and HSTL Output(s) |        |     | 77  | 119 | ps   | Outputs on the same device; assumes worst-case output combination |

| LVDS Output(s) and CMOS Output(s) |        |     | 497 | 700 | ps   | Outputs on the same device; assumes worst-case output combination |

| HSTL Output(s) and CMOS Output(s) |        |     | 424 | 622 | ps   | Outputs on the same device; assumes worst-case output combination |

<sup>1</sup> Output skew is the difference between any two similar delay paths while operating at the same voltage and temperature.

### LOGIC INPUTS

| Table 4. |

|----------|

|----------|

| Parameter                        | Symbol                              | Min  | Тур | Max  | Unit | Test Conditions/Comments       |

|----------------------------------|-------------------------------------|------|-----|------|------|--------------------------------|

| LOGIC INPUTS RESET, SYNC, IN_SEL |                                     |      |     |      |      |                                |

| Input Voltage                    |                                     |      |     |      |      |                                |

| High                             | VIH                                 | 1.7  |     |      | V    | 2.5 V supply voltage operation |

|                                  |                                     | 2.0  |     |      | V    | 3.3 V supply voltage operation |

| Low                              | VIL                                 |      |     | 0.7  | V    | 2.5 V supply voltage operation |

|                                  |                                     |      |     | 0.8  | V    | 3.3 V supply voltage operation |

| Input Current                    | I <sub>INH</sub> , I <sub>INL</sub> | -300 |     | +100 | μΑ   |                                |

| Input Capacitance                | CIN                                 |      | 2   |      | pF   |                                |

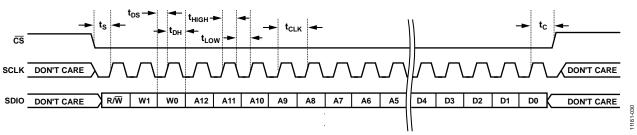

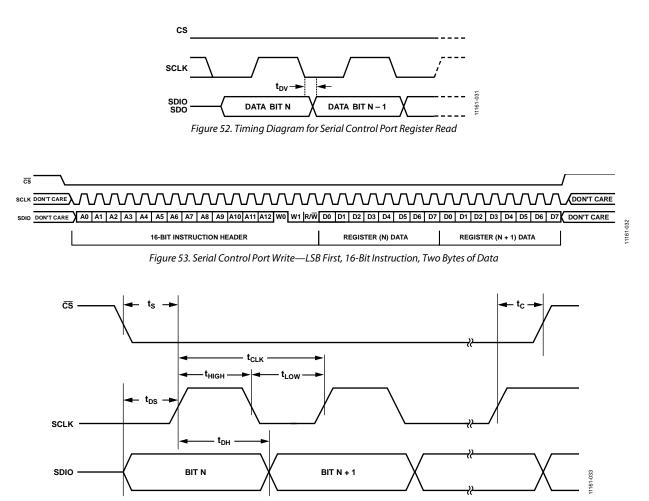

### SERIAL PORT SPECIFICATIONS—SPI MODE

#### Table 5.

| Parameter         | Min       | Тур | Max | Unit | Test Conditions/Comments                              |

|-------------------|-----------|-----|-----|------|-------------------------------------------------------|

| CS                |           |     |     |      | SCLK has a 200 k $\Omega$ internal pull-down resistor |

| Input Voltage     |           |     |     |      |                                                       |

| Logic 1           | VDD - 0.4 |     |     | V    |                                                       |

| Logic 0           |           |     | 0.4 | V    |                                                       |

| Input Current     |           |     |     |      |                                                       |

| Logic 1           |           | -4  |     | μA   |                                                       |

| Logic 0           |           | -85 |     | μA   |                                                       |

| Input Capacitance |           | 2   |     | μA   |                                                       |

| SCLK              |           |     |     |      |                                                       |

| Input Voltage     |           |     |     |      |                                                       |

| Logic 1           | VDD - 0.4 |     |     | V    |                                                       |

| Logic 0           |           |     | 0.4 | V    |                                                       |

| Input Current     |           |     |     |      |                                                       |

| Logic 1           |           | 70  |     | μA   |                                                       |

| Logic 0           |           | 13  |     | μA   |                                                       |

| Input Capacitance |           | 2   |     | pF   |                                                       |

| SDIO              |           |     |     |      |                                                       |

| As Input          |           |     |     |      |                                                       |

| Input Voltage     |           |     |     |      |                                                       |

| Logic 1           | VDD - 0.4 |     |     | V    |                                                       |

| Logic 0           |           |     | 0.4 | V    |                                                       |

| Input Current     |           |     |     |      |                                                       |

| Logic 1           |           | -1  |     | μA   |                                                       |

| Logic 0           |           | -1  |     | μA   |                                                       |

| Input Capacitance |           | 2   |     | pF   |                                                       |

| Parameter                                   | Min       | Тур | Max | Unit | Test Conditions/Comments |

|---------------------------------------------|-----------|-----|-----|------|--------------------------|

| As Output                                   |           |     |     |      |                          |

| Output Voltage                              |           |     |     |      |                          |

| Logic 1                                     | VDD - 0.4 |     |     | V    | 1 mA load current        |

| Logic 0                                     |           |     | 0.4 | V    | 1 mA load current        |

| SDO                                         |           |     |     |      |                          |

| Output Voltage                              |           |     |     |      |                          |

| Logic 1                                     | VDD - 0.4 |     |     | V    | 1 mA load current        |

| Logic 0                                     |           |     | 0.4 | V    | 1 mA load current        |

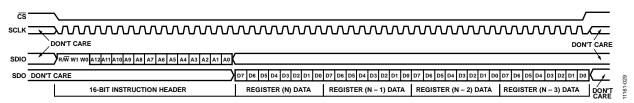

| TIMING                                      |           |     |     |      |                          |

| SCLK                                        |           |     |     |      |                          |

| Clock Rate, 1/t <sub>CLK</sub>              |           |     | 30  | MHz  |                          |

| Pulse Width High, t <sub>HIGH</sub>         | 4.6       |     |     | ns   |                          |

| Pulse Width Low, tLOW                       | 3.5       |     |     | ns   |                          |

| SDIO to SCLK Setup, t <sub>DS</sub>         | 2.9       |     |     | ns   |                          |

| SCLK to SDIO Hold, t <sub>DH</sub>          | 0         |     |     | ns   |                          |

| SCLK to Valid SDIO and SDO, $t_{\text{DV}}$ |           |     | 15  | ns   |                          |

| CS to SCLK Setup (ts)                       | 3.4       |     |     | ns   |                          |

| CS to SCLK Hold (t <sub>c</sub> )           | 0         |     |     | ns   |                          |

| CS to Minimum Pulse Width High              | 3.4       |     |     | ns   |                          |

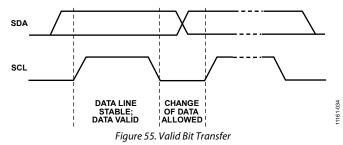

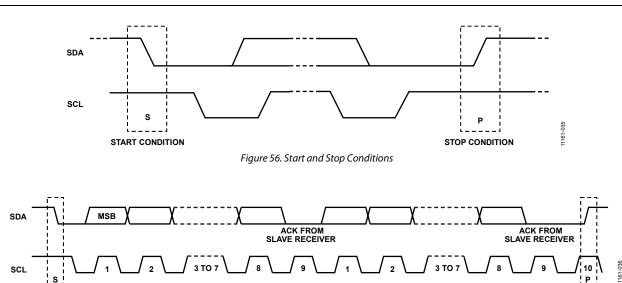

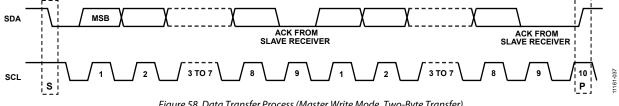

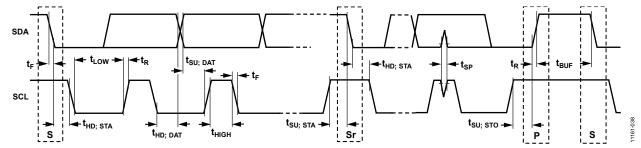

### SERIAL PORT SPECIFICATIONS—I<sup>2</sup>C MODE

| Table 6.                                                              |           |     |     |      |                                                       |  |  |

|-----------------------------------------------------------------------|-----------|-----|-----|------|-------------------------------------------------------|--|--|

| Parameter                                                             | Min       | Тур | Max | Unit | Test Conditions/Comments                              |  |  |

| SDA, SCL (AS INPUT)                                                   |           |     |     |      |                                                       |  |  |

| Input Voltage                                                         |           |     |     |      |                                                       |  |  |

| Logic 1                                                               | VDD - 0.4 |     |     | V    |                                                       |  |  |

| Logic 0                                                               |           |     | 0.4 | V    |                                                       |  |  |

| Input Current                                                         | -40       |     | 0   | μΑ   | For $V_{\text{IN}} = 10\%$ to 90% DVDD3               |  |  |

| Hysteresis of Schmitt Trigger Inputs                                  | 150       |     |     | mV   |                                                       |  |  |

| SDA (AS OUTPUT)                                                       |           |     |     |      |                                                       |  |  |

| Output Logic 0 Voltage                                                |           |     | 0.4 | V    | $I_0 = 3 \text{ mA}$                                  |  |  |

| Output Fall Time from $V_{IH (MIN)}$ to $V_{IL (MAX)}$                |           |     | 250 | ns   | $10 \text{ pF} \le C_b \le 400 \text{ pF}$            |  |  |

| TIMING                                                                |           |     |     |      |                                                       |  |  |

| SCL Clock Rate                                                        |           |     | 400 | kHz  |                                                       |  |  |

| Bus-Free Time Between a Stop and Start<br>Condition, t <sub>BUF</sub> | 1.3       |     |     | μs   |                                                       |  |  |

| Repeated Start Condition Setup Time, tsu; STA                         |           |     | 0.6 | μs   |                                                       |  |  |

| Repeated Hold Time Start Condition, $t_{\text{HD};\text{STA}}$        | 0.6       |     |     | μs   | After this period, the first clock pulse is generated |  |  |

| Stop Condition Setup Time, tsu; sto                                   | 0.6       |     |     | μs   |                                                       |  |  |

| Low Period of the SCL Clock, tLOW                                     | 1.3       |     |     | μs   |                                                       |  |  |

| High Period of the SCL Clock, thigh                                   | 0.6       |     |     | μs   |                                                       |  |  |

| Data Setup Time, t <sub>su; DAT</sub>                                 | 100       |     |     | ns   |                                                       |  |  |

| Data Hold Time, thd; dat                                              | 0         |     | 0.9 | μs   |                                                       |  |  |

### EXTERNAL RESISTOR VALUES FOR PIN STRAPPING MODE

| Parameter          | Resistor Polarity   | Min | Тур | Max | Unit | Test Conditions/Comments     |

|--------------------|---------------------|-----|-----|-----|------|------------------------------|

| EXTERNAL RESISTORS |                     |     |     |     |      | Using 10% tolerance resistor |

| Voltage Level 0    | Pull down to ground |     | 820 |     | Ω    |                              |

| Voltage Level 1    | Pull down to ground |     | 1.8 |     | kΩ   |                              |

| Voltage Level 2    | Pull down to ground |     | 3.9 |     | kΩ   |                              |

| Voltage Level 3    | Pull down to ground |     | 8.2 |     | kΩ   |                              |

| Voltage Level 4    | Pull up to VDD      |     | 820 |     | Ω    |                              |

| Voltage Level 5    | Pull up to VDD      |     | 1.8 |     | kΩ   |                              |

| Voltage Level 6    | Pull up to VDD      |     | 3.9 |     | kΩ   |                              |

| Voltage Level 7    | Pull up to VDD      |     | 8.2 |     | kΩ   |                              |

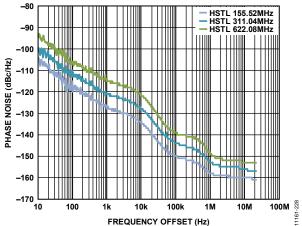

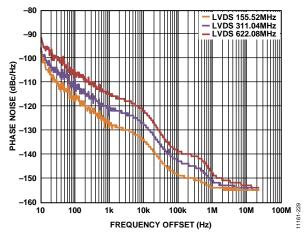

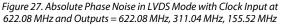

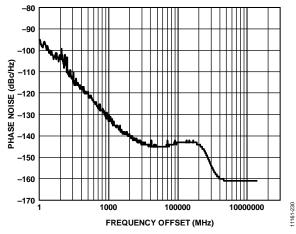

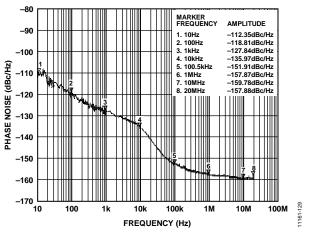

### **CLOCK OUTPUT ADDITIVE PHASE NOISE**

Table 8.

| Parameter                                        | Min | Тур  | Max | Unit   | Test Conditions/Comments |

|--------------------------------------------------|-----|------|-----|--------|--------------------------|

| CLK-TO-HSTL OR LVDS ADDITIVE PHASE NOISE         |     |      |     |        |                          |

| CLK = 1474.56 MHz, OUTx = 1474.56 MHz            |     |      |     |        | Input slew rate > 1 V/ns |

| Divide Ratio = 1                                 |     |      |     |        |                          |

| At 10 Hz Offset                                  |     | -88  |     | dBc/Hz |                          |

| At 100 Hz Offset                                 |     | -100 |     | dBc/Hz |                          |

| At 1 kHz Offset                                  |     | -109 |     | dBc/Hz |                          |

| At 10 kHz Offset                                 |     | -116 |     | dBc/Hz |                          |

| At 100 kHz Offset                                |     | -135 |     | dBc/Hz |                          |

| At 1 MHz Offset                                  |     | -144 |     | dBc/Hz |                          |

| At 10 MHz Offset                                 |     | -148 |     | dBc/Hz |                          |

| At 100 MHz Offset                                |     | -149 |     | dBc/Hz |                          |

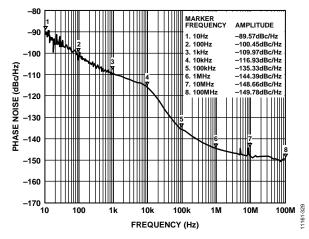

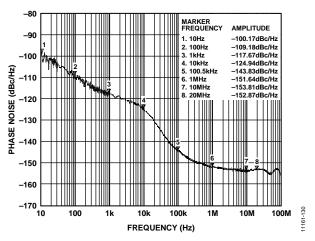

| CLK-TO-HSTL OR LVDS or CMOS ADDITIVE PHASE NOISE |     |      |     |        |                          |

| CLK = 625 MHz, OUTx = 125 MHz                    |     |      |     |        | Input slew rate > 1 V/ns |

| Divide Ratio = 5                                 |     |      |     |        |                          |

| At 10 Hz Offset                                  |     | -114 |     | dBc/Hz |                          |

| At 100 Hz Offset                                 |     | -125 |     | dBc/Hz |                          |

| At 1 kHz Offset                                  |     | -133 |     | dBc/Hz |                          |

| At 10 kHz Offset                                 |     | -141 |     | dBc/Hz |                          |

| At 100 kHz Offset                                |     | -159 |     | dBc/Hz |                          |

| At 1 MHz Offset                                  |     | -162 |     | dBc/Hz |                          |

| At 10 MHz Offset                                 |     | -163 |     | dBc/Hz |                          |

| At 20 MHz Offset                                 |     | -163 |     | dBc/Hz |                          |

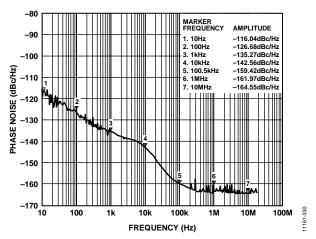

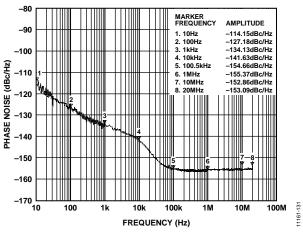

| CLK-TO-HSTL OR LVDS ADDITIVE PHASE NOISE         |     |      |     |        |                          |

| CLK = 491.52 MHz, OUTx = 491.52 MHz              |     |      |     |        | Input slew rate > 1 V/ns |

| Divide Ratio = 1                                 |     |      |     |        |                          |

| At 10 Hz Offset                                  |     | -100 |     | dBc/Hz |                          |

| At 100 Hz Offset                                 |     | -111 |     | dBc/Hz |                          |

| At 1 kHz Offset                                  |     | -120 |     | dBc/Hz |                          |

| At 10 kHz Offset                                 |     | -127 |     | dBc/Hz |                          |

| At 100 kHz Offset                                |     | -146 |     | dBc/Hz |                          |

| At 1 MHz Offset                                  |     | -153 |     | dBc/Hz |                          |

| At 10 MHz Offset                                 |     | -153 |     | dBc/Hz |                          |

| At 20 MHz Offset                                 |     | -153 |     | dBc/Hz |                          |

### **CLOCK OUTPUT ADDITIVE TIME JITTER**

#### Table 9.

| Parameter                              | Min Typ | Max | Unit   | Test Conditions/Comments |

|----------------------------------------|---------|-----|--------|--------------------------|

| LVDS OUTPUT ADDITIVE TIME JITTER       |         |     |        |                          |

| CLK = 622.08 MHz, Outputs = 622.08 MHz | 41      |     | fs rms | BW = 12  kHz to  20  MHz |

|                                        | 70      |     | fs rms | BW = 20  kHz to  80  MHz |

|                                        | 69      |     | fs rms | BW = 50  kHz to  80  MHz |

| CLK = 622.08 MHz, Outputs = 155.52 MHz | 93      |     | fs rms | BW = 12  kHz to  20  MHz |

|                                        | 144     |     | fs rms | BW = 20  kHz to  80  MHz |

|                                        | 142     |     | fs rms | BW = 50  kHz to  80  MHz |

| CLK = 125 MHz, Outputs = 125 MHz       | 105     |     | fs rms | BW = 12  kHz to  20  MHz |

|                                        | 209     |     | fs rms | BW = 20  kHz to  80  MHz |

|                                        | 206     |     | fs rms | BW = 50  kHz to  80  MHz |

| CLK = 400 MHz, Outputs = 50 MHz        | 184     |     | fs rms | BW = 12  kHz to  20  MHz |

| HSTL OUTPUT ADDITIVE TIME JITTER       |         |     |        |                          |

| CLK = 622.08 MHz, Outputs = 622.08 MHz | 41      |     | fs rms | BW = 12  kHz to  20  MHz |

|                                        | 56      |     | fs rms | BW = 100 Hz to 20 MHz    |

|                                        | 72      |     | fs rms | BW = 20  kHz to  80  MHz |

|                                        | 70      |     | fs rms | BW = 50  kHz to  80  MHz |

| CLK = 622.08 MHz, Outputs = 155.52 MHz | 76      |     | fs rms | BW = 12  kHz to  20  MHz |

|                                        | 87      |     | fs rms | BW = 100 Hz to 20 MHz    |

|                                        | 158     |     | fs rms | BW = 20  kHz to  80  MHz |

|                                        | 156     |     | fs rms | BW = 50  kHz to  80  MHz |

| CMOS OUTPUT ADDITIVE TIME JITTER       |         |     |        |                          |

| CLK = 100 MHz, Outputs = 100 MHz       | 91      |     | fs rms | BW = 12  kHz to  20  MHz |

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 10.

| Parameter                           | Rating                |

|-------------------------------------|-----------------------|

| Supply Voltage (VDD)                | 3.6 V                 |

| Maximum Digital Input Voltage       | –0.5 V to VDD + 0.5 V |

| CLK and CLK                         | –0.5 V to VDD + 0.5 V |

| Maximum Digital Output Voltage      | –0.5 V to VDD + 0.5 V |

| Storage Temperature Range           | –65°C to +150°C       |

| Operating Temperature Range         | –40°C to +85°C        |

| Lead Temperature (Soldering 10 sec) | 300°C                 |

| Junction Temperature                | 150°C                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

The following equation determines the junction temperature on the application PCB:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_J$  is the junction temperature (°C).

$T_{CASE}$  is the case temperature (°C) measured by the customer at the top center of the package.

$\Psi_{JT}$  is the value as indicated in Table 11.

$P_D$  is the power dissipation.

Values of  $\theta_{JA}$  are provided for package comparison and PCB design considerations.  $\theta_{JA}$  can be used for a first-order approximation of  $T_J$  by the following equation:

$$T_J = T_A + (\theta_{JA} \times P_D)$$

where  $T_A$  is the ambient temperature (°C).

Values of  $\theta_{JC}$  are provided for package comparison and PCB design considerations when an external heat sink is required.

Values of  $\theta_{I^B}$  are provided for package comparison and PCB design considerations.

### THERMAL CHARACTERISTICS

Thermal characteristics established using JEDEC51-7 and JEDEC51-5 2S2P test boards.

| Symbol           | Thermal Characteristic<br>(JEDEC51-7 and JEDEC51-5 2S2P<br>Test Boards <sup>1</sup> )           | Value <sup>2</sup> | Unit |

|------------------|-------------------------------------------------------------------------------------------------|--------------------|------|

| ALθ              | Junction-to-ambient thermal<br>resistance per JEDEC JESD51-2 (still<br>air)                     | 43.5               | °C/W |

| θјма             | Junction-to-ambient thermal<br>resistance, 1.0 m/sec airflow per<br>JEDEC JESD51-6 (moving air) | 40                 | °C/W |

| θ <sub>JMA</sub> | Junction-to-ambient thermal<br>resistance, 2.5 m/sec airflow per<br>JEDEC JESD51-6 (moving air) | 38.5               | °C/W |

| $\theta_{^{JB}}$ | Junction-to-board thermal<br>resistance per JEDEC JESD51-8 (still<br>air)                       | 16.2               | °C/W |

| θ」с              | Junction-to-case thermal resistance<br>(die-to-heat sink) per MIL-STD-883,<br>Method 1012.1     | 7.1                | °C/W |

| Ψ <sub>JT</sub>  | Junction-to-top-of-package<br>characterization parameter per<br>JEDEC JESD51-2 (still air)      | 0.33               | °C/W |

#### Table 11. Thermal Characteristics, 24-Lead LFCSP

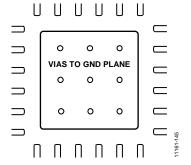

<sup>1</sup> The exposed pad on the bottom of the package must be soldered to ground (VSS) to achieve the specified thermal performance.

<sup>2</sup> Results are from simulations. The PCB is a JEDEC multilayer type. Thermal performance for actual applications requires careful inspection of the conditions in the application to determine if they are similar to those assumed in these calculations.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

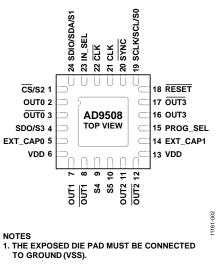

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 12. Pin Function Descriptions

| Pin No. | Mnemonic      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | <u>CS</u> /S2 | Chip Select/Pin Programming. Multipurpose pin. This pin is controlled by the PROG_SEL pin. Chip Select (CS) is an active logic low CMOS input used in the SPI operation mode. When programming a device via SPI mode, CS must be held low. In systems where more than one AD9508 is present, this pin enables individual programming of each AD9508. In pin programming mode, this pin becomes S2. In this mode, S2 is hard wired with a resistor to either VDD or ground. The resistor value and resistor biasing determine the output divider value for the outputs on Pin 11 and Pin 12. See the Pin Strapping to Program on Power-Up section for more details. |

| 2       | OUT0          | LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3       | OUT0          | Complementary LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4       | SDO/S3        | Serial Data Output/Pin Programming. Multipurpose pin. This pin is controlled by the PROG_SEL pin.<br>SDO is configured as an output to read back the internal register settings in SPI mode operation. In pin<br>programming mode, this pin becomes S3, which is hard wired with a resistor to either VDD or ground.<br>The resistor value and resistor biasing determine the output divider value for the outputs on Pin 16 and<br>Pin 17. See the Pin Strapping to Program on Power-Up section for more details.                                                                                                                                                 |

| 5       | EXT_CAP0      | Node for External Decoupling Capacitor for LDO. Tie this pin to a 0.47 $\mu$ F capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6       | VDD           | Power Supply (2.5 V or 3.3 V Operation).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7       | OUT1          | LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8       | OUT1          | Complementary LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9       | S4            | Pin Programming. Use this pin in pin programming mode only. The PROG_SEL pin determines which programming mode is used. In pin programming mode, S4 is hardwired with a resistor to either VDD or ground. The resistor value and resistor biasing determine the output logic levels used for the outputs on Pin 2, Pin 3, Pin 7, and Pin 8. See the Pin Strapping to Program on Power-Up section for more details.                                                                                                                                                                                                                                                 |

| 10      | S5            | Pin Programming. Use this pin in pin programming mode only. The PROG_SEL pin determines which programming mode is used. In pin programming mode, S5 is hardwired with a resistor to either VDD or ground. The resistor value and resistor biasing determine the output logic levels used for the outputs on Pin 11, Pin 12, Pin 16, and Pin 17. See the Pin Strapping to Program on Power-Up section for more details.                                                                                                                                                                                                                                             |

| 11      | OUT2          | LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12      | OUT2          | Complementary LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13      | VDD           | Power Supply (2.5 V or 3.3 V Operation).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14      | EXT_CAP1      | Node for External Decoupling Capacitor for LDO. Tie this pin to a 0.47 µF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15      | PROG_SEL      | Three-State CMOS Input. Pin 15 selects the type of device programming interface to be used (SPI, I <sup>2</sup> C, or pin programming).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16      | OUT3          | LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17      | OUT3          | Complementary LVDS/HSTL Differential Output or Single-Ended CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# **Data Sheet**

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | RESET       | CMOS Input. Device Reset. When this active low pin is asserted, the internal register settings enter their default state after the RESET is released. Note that RESET also serves as a power-down of the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |             | while an active low signal is applied to the pin. The $\overrightarrow{RESET}$ pin has an internal 24 k $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19      | SCLK/SCL/S0 | Serial Programming Clock/Data Clock/Programming Pin. Multipurpose pin controlled by the PROG_SEL pin used for serial programming clock (SCLK) in SPI mode or data clock (SCL) for serial programming in I <sup>2</sup> C Mode. The PROG_SEL pin determines which programming mode is used. In pin programming mode, this pin becomes S0. In this mode, S0 is hardwired with a resistor to either VDD or ground. The resistor value and resistor biasing determine the output divider values for the outputs on Pin 2 and Pin 3. See the Pin Strapping to Program on Power-Up section for more details.                                                                                                                                                                                                                                                       |

| 20      | SYNC        | Clock Synchronization. When this pin is active low, the output drivers are held static and then synchronized on a low-to-high transition of this pin. The SYNC pin has an internal 24 k $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

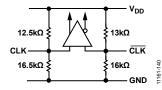

| 21      | CLK         | Differential Clock Input or Single-Ended CMOS Input. Whether this pin serves as the differential clock input or the single-ended CMOS input depends on the logic state of the IN_SEL pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

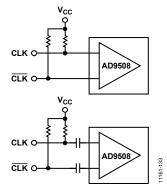

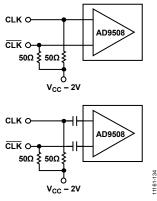

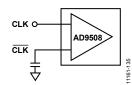

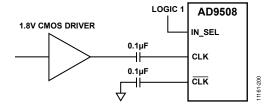

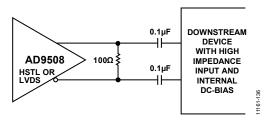

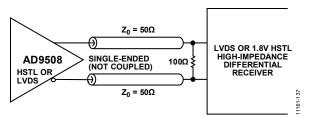

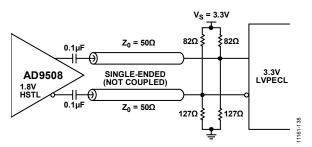

| 22      | CLK         | Complementary Differential Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |