OL2381 Highly integrated single-chip sub 1 GHz RF transceiver Rev. 1 – 30 November 2011 Product data sheet

## 1. General description

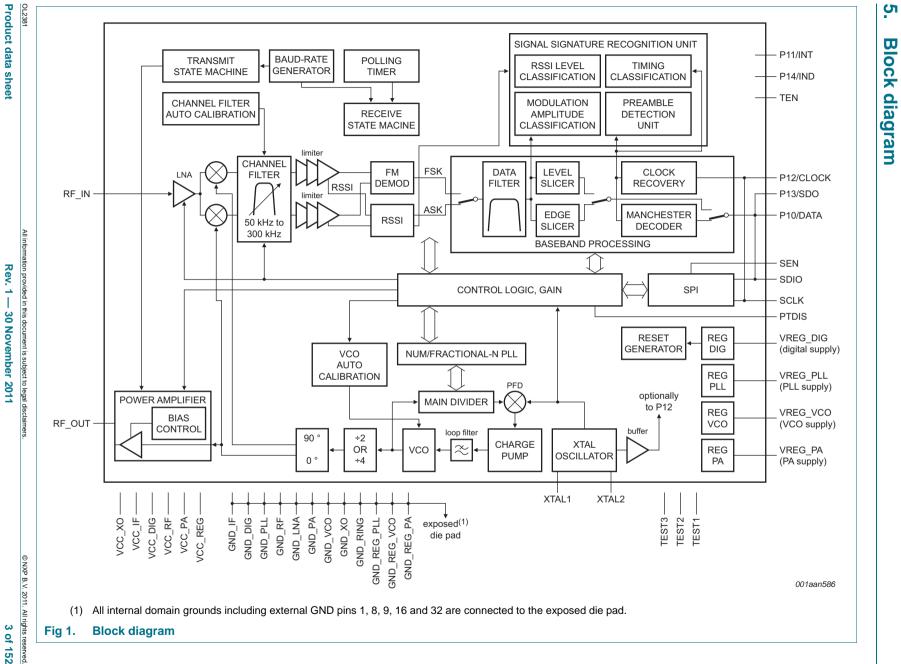

A highly integrated single-chip transceiver solution, the OL2381 is ideally suited to telemetry applications operating in the ISM/SRD bands. The small form factor, low power consumption and wide supply voltage range make this device suitable for use in battery powered, handheld devices and their counter parts.

The device utilizes a fully integrated, programmable fractional-N PLL (including loop filter) to control the Local Oscillator (LO), thus supporting multi-channel operation and frequency hopping schemes. This feature also allows programmable frequency steps for crystal (XTAL) drift compensation.

The device can employ ASK, FSK or GFSK type modulation. The ASK modulation characteristics are fully programmable by varying the power amplifier output power in accordance with the TX data. The FSK modulation utilizes the fractional-N PLL capability to precisely modulate the LO frequency with the TX data (in loop modulation). Relaxed narrow band applications can utilize an on-chip GFSK type modulation to improve the spectral occupancy.

The device is based on a low IF direct conversion receiver architecture, with on-chip IF filtering and programmable channel bandwidth. After filtering and amplification the quadrature signals are digitized, demodulated and processed in the digital domain.

Baseband processing of the received signal comprises a demodulator, a data-slicer and clock recovery followed by a Manchester decoder. Automated signal signature recognition units are available to allow simple, fast and reliable data reception.

The device is controlled via a three-wire serial interface (SPI) with data input and output, data clock and interface enable. The interface can be configured to a full SPI interface with separate data and clock pins. Additional pins are available to access internal signals in real-time.

## 2. Features and benefits

- Highly integrated solution for the 315/434/868/915 MHz band

- Very few external components required

- Complies with ETSI EN300-220/FCC part 15 standards

- Near zero-IF RX architecture

- On-chip channel filtering with automatic calibration supported to provide stable cut-off frequencies and filter roll-off

- Multi-channel TX and RX operation by fully integrated fractional-N PLL with on-chip loop filter

- Automatic VCO sub-band selection and calibration to reduce PLL loop bandwidth variation

- Programmable ASK/FSK modulation with Manchester codec

- Programmable transmitter output power (-20 dBm to +10 dBm), stabilized with onboard PA regulator

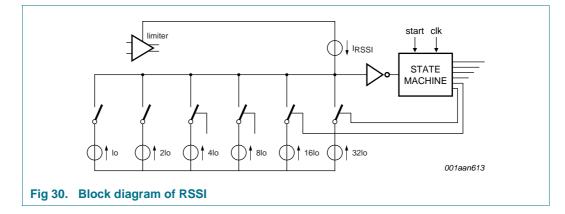

- Digital RSSI with a configurable threshold

- Onboard Signal Signature Recognition Unit (SSRU) with Preamble Pattern Recognition (PPR)

- Configurable RX polling timer with 2 % absolute accuracy

- Level Sensitive Data (LSD) slicer with self-adjusting threshold

- Low power consumption (RX 16 mA, TX 13 mA at 6 dBm), with ultra Low 0.5 μA standby current and configurable polling timer

- Single lithium cell operation (2.1 V). Operation up to 3.6 V fully supported

- 32-Pin HVQFN32 Pb-free package

## 3. Applications

- Smart metering (wireless M-bus)

- Home and building security and automation (KNX-RF)

- Remote control devices

- After-market Remote Keyless Entry (RKE)

- Wireless medical applications

- Wireless sensor network

## 4. Ordering information

#### Table 1. Ordering information

| Type number | Package |                                                                                                                  |          |  |  |

|-------------|---------|------------------------------------------------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                                                                      | Version  |  |  |

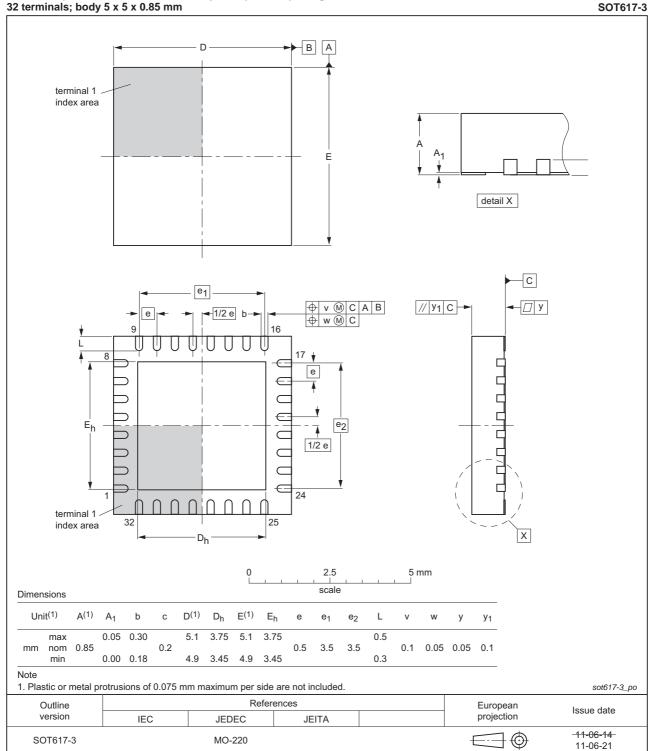

| OL2381AHN   | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 $\times$ 5 $\times$ 0.85 mm | SOT617-3 |  |  |

**OL2381**

-30 November 2011

3 of 152

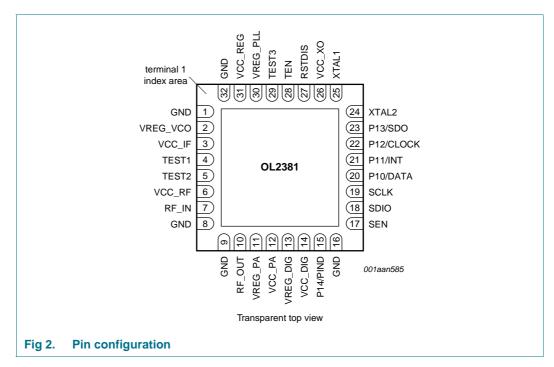

# 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

| Symbol   | Pin | Туре | Reset<br>state | Description                                                                  |

|----------|-----|------|----------------|------------------------------------------------------------------------------|

| GND      | 1   | -    | -              | ground; use exposed heatsink as ground reference                             |

| VREG_VCO | 2   | А    | Z              | VCO regulator output voltage to decoupling capacitor                         |

| VCC_IF   | 3   | А    | А              | IF section power supply                                                      |

| TEST1    | 4   | А    | Z              | RX test I output                                                             |

| TEST2    | 5   | А    | Z              | RX test Q output                                                             |

| VCC_RF   | 6   | А    | А              | LNA power supply                                                             |

| RF_IN    | 7   | А    | А              | RX RF signal input                                                           |

| GND      | 8   | -    | -              | ground; use exposed heatsink as ground reference                             |

| GND      | 9   | -    | -              | ground; use exposed heatsink as ground reference                             |

| RF_OUT   | 10  | А    | Z              | TX RF signal output                                                          |

| VREG_PA  | 11  | A    | Z              | power amplifier regulator output voltage to decoupling capacitor             |

| VCC_PA   | 12  | А    | А              | power amplifier power supply                                                 |

| VREG_DIG | 13  | А    | А              | digital regulator output voltage to decoupling capacitor                     |

| VCC_DIG  | 14  | А    | А              | digital module supply voltage                                                |

| P14/PIND | 15  | DO   | Z              | digital output port with increased drive capability for PIN<br>diode control |

| Table 2. Pi        | n des | criptior | ncontinued                  | 1                                                                                                                            |

|--------------------|-------|----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Symbol             | Pin   | Туре     | Reset<br>state              | Description                                                                                                                  |

| GND                | 16    | -        | -                           | ground; use exposed heatsink as ground reference                                                                             |

| SEN                | 17    | DI       | DI                          | serial interface enable                                                                                                      |

| SDIO               | 18    | DIO      | DI                          | serial interface input/output                                                                                                |

| SCLK               | 19    | DIO      | DI                          | serial interface clock                                                                                                       |

| P10/DATA           | 20    | DleO     | Z                           | digital output port, TX data input, RX data output, data output of debug interface                                           |

| P11/INT            | 21    | DO       | POR,<br>interrupt<br>output | digital output port, interrupt output, several status indicators, reference clock output, frame indicator of debug interface |

| P12/CLOCK          | 22    | DO       | 1 MHz<br>reference<br>clock | digital output port, TX/reference clock out, RX data clock, clock of debug interface                                         |

| P13/SDO            | 23    | DO       | Z                           | digital output port, status indicators, serial interface data output                                                         |

| XTAL2              | 24    | А        | А                           | crystal reference clock frequency input                                                                                      |

| XTAL1              | 25    | А        | А                           | crystal connection                                                                                                           |

| VCC_XO             | 26    | А        | А                           | crystal oscillator supply voltage                                                                                            |

| RSTDIS             | 27    | DI       | DI                          | reset disable signal                                                                                                         |

| TEN                | 28    | DI       | DI                          | test enable input                                                                                                            |

| TEST3              | 29    | А        | Z                           | PLL test output                                                                                                              |

| VREG_PLL           | 30    | А        | Z                           | PLL regulator output voltage to decoupling capacitor                                                                         |

| VCC_REG            | 31    | А        | А                           | PLL, VCO regulators power supply                                                                                             |

| GND                | 32    | -        | -                           | ground; use exposed heatsink as ground reference                                                                             |

| exposed die<br>pad | -     | A        | GND                         | ground connection                                                                                                            |

[1] A = analog.

DI = digital input.

DO = digital output with enable signal.

DIO = digital input without enable signal and output with enable signal.

DIeO = digital input and output both with enable signal.

## 7. Functional description

#### 7.1 General architecture description

The OL2381 transceiver is designed for use in both complex base-stations, when paired with powerful microcontrollers, and low component-count remote units with low pin-count microcontrollers. The IC features unique configuration possibilities via external pin-level configuration or SFR bit manipulation. Several automatic sequences are implemented to ease device operation, all of which can be manually influenced or overridden by control-bits.

#### 7.1.1 Power management

The device contains a configurable power-on reset block. The device control registers are reset as the external voltage rises to ensure that the device state is in Standby mode. This is implemented by ensuring that all blocks are off except the SPI and the digital regulator. Note that the digital regulator is operating in clamp mode at this time.

#### 7.1.2 XTAL oscillator

The main time-reference is derived from an amplitude-controlled XTAL oscillator. This 16 MHz reference is used as a reference clock for the PLL and as a timing reference for various analog calibration purposes.

#### 7.1.3 Polling timer

Several base-station applications require a low-power polling timer for periodic device wakeup. This feature is essential to enable listening in pre-programmed time-windows when the OL2381 is used in RX mode applications. Internal configuration and trimming registers allow the setting of a wide range of different timer intervals while achieving an average timing accuracy of 2 %.

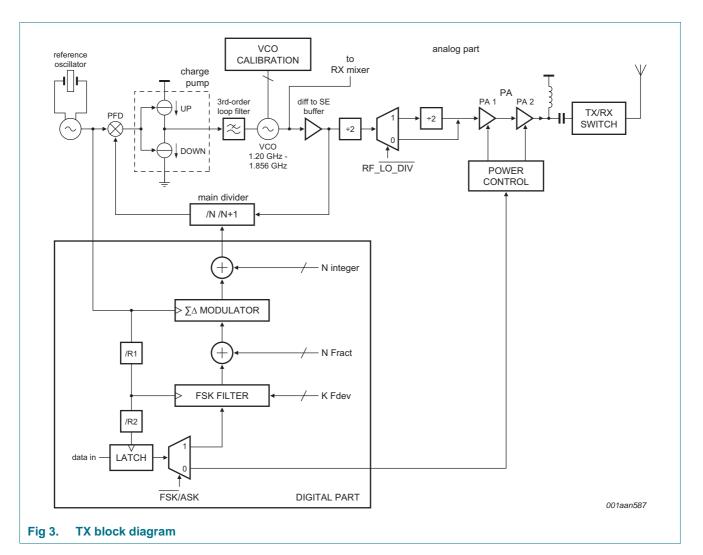

#### 7.1.4 TX block

The TX section is able to operate within all ISM bands: 315 MHz, 434 MHz, 868 MHz and 916 MHz. The device provides a high degree of flexibility and is capable of ASK/FSK modulation, output power control and on-chip baud-rate generation with data rates up to 112 kchip/s. The device features multi-channel operation and enables carrier frequency adjustment and compensation of XTAL frequency offsets due to its high resolution fractional-N PLL architecture. The TX block features a high degree of integration, employing an on-chip VCO and PLL loop filter.

### **NXP Semiconductors**

#### Highly integrated single-chip sub 1 GHz RF transceiver

OL2381

#### 7.1.5 VCO calibration

On-chip calibration is available to reduce the VCO input voltage range and thus reduce the PLL loop bandwidth variation. The variation in system parameters such as locking time and LO phase noise can therefore be maintained within a tight window.

Calibration is performed by selecting the proper VCO sub-band according to the desired channel frequency. VCO sub-band selection and the PLL start-up sequence can be triggered by command and are supported by an automatic flow sequence. This flow can be overridden if required. Note that if the incorrect sub-band is chosen the VCO calibration is unable to tune to the desired frequency.

#### 7.1.6 TX command

TX parameters (frequency, modulation, output power etc) can be predefined to enable fast and simple entry into TX mode (PA switched on).

#### 7.1.7 RX block

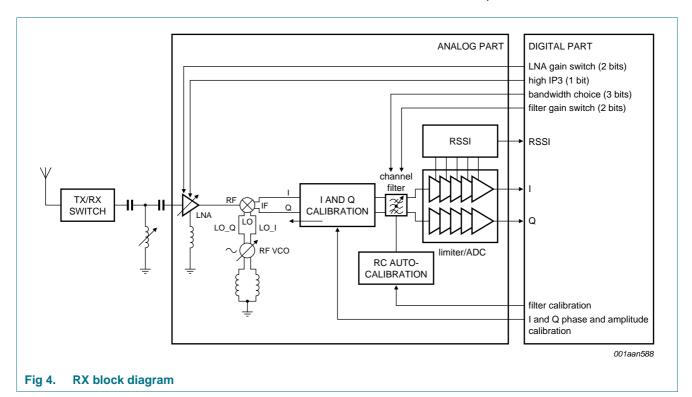

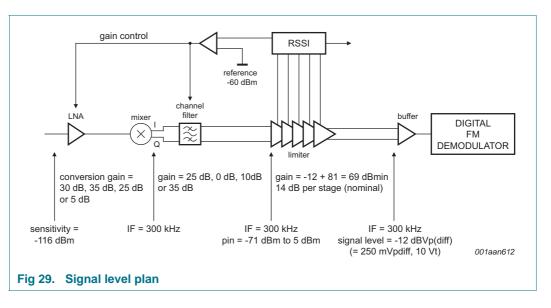

The OL2381's RX path consists of a broadband resistive-feedback LNA, a mixer (mixing down the input signal to an IF of 300 kHz), a channel-filter, a limiter, an RSSI stage (AM demodulation) and a base-band signal processing block used for FM and AM data and clock recovery. The LNA, limiter and channel-filter gain settings can be configured via control bits. The channel filter bandwidth can also be adapted.

#### 7.1.8 Channel filter auto-calibration

Channel bandwidth accuracy requirements vary between applications. The modulation bandwidth changes with different bit rates. Bit rates can be 0.5 kbit/s to 112 kchip/s and the IF channel filter bandwidth must be set accordingly in the range 50 kHz to 300 kHz.

Channel bandwidth auto-calibration is implemented to maintain constant performance. This ensures stable cut-off frequencies and filter roll-off over process and temperature variations. This calibration is included in the RX command.

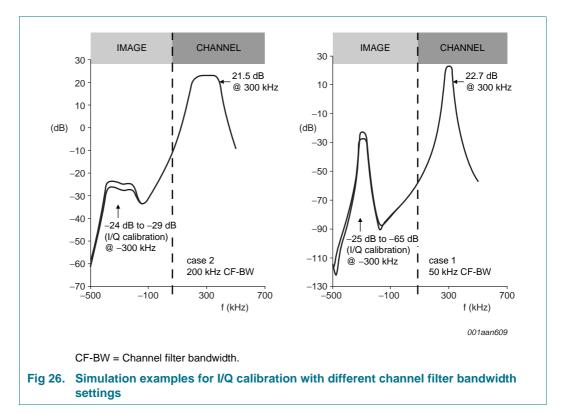

#### 7.1.9 I/Q calibration

I/Q calibration can be implemented to improve the channel image rejection for certain applications. This calibration improves amplitude mismatch and phase quadrature between I and Q signals.

Both parameters can be trimmed by injecting an external RF signal operating in the image channel. The RSSI can then be used to determine the optimum settings to have the minimal remaining signal. This calibration is required for each frequency band.

The I/Q calibration settings are made available to -, and must be stored by, an external microcontroller.

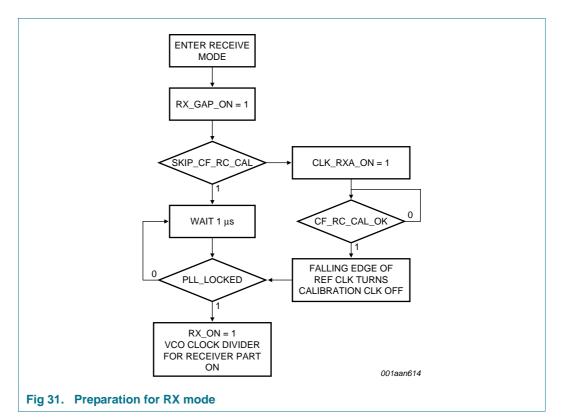

#### 7.1.10 Receive command

The predefined set of RX parameters (center frequency, modulation, etc.) enables Receive mode (receiver and LO buffers switched on) to be entered quickly after receiving the RX command. Several methods of signal signature recognition are implemented. These modes of semi-automatic signal processing can be pre-selected by the RX command.

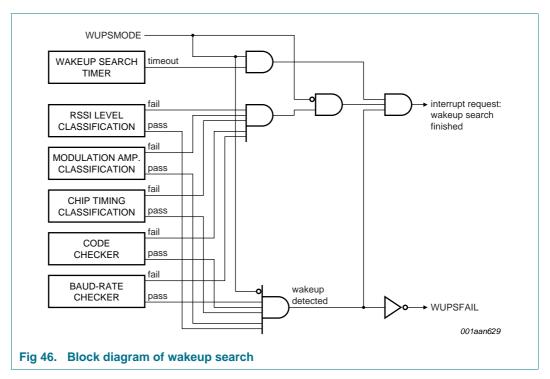

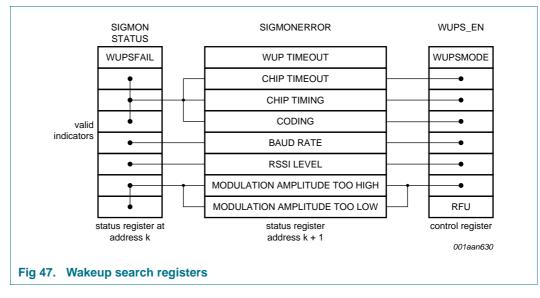

#### 7.1.11 Signal signature recognition unit

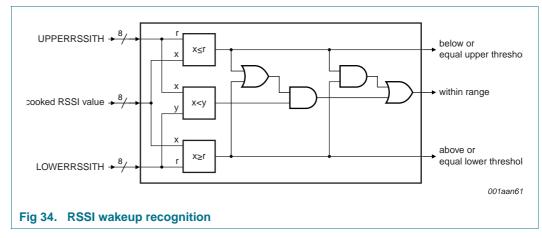

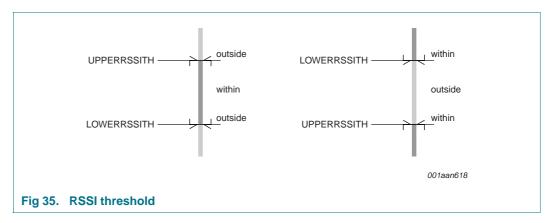

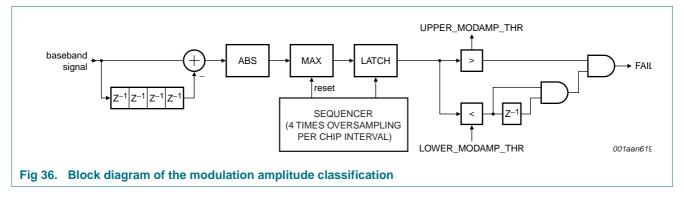

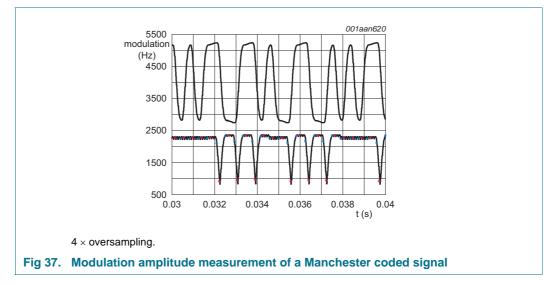

Several signal recognition units are implemented to provide fast and accurate signal detection. Signal signatures such as signal level (RSSI), modulation depth or baud-rate and coding can be automatically detected as wakeup criteria during the wakeup search phase.

#### 7.1.12 Preamble detection

A configurable 1-bit to 32-bit pattern recognition unit can be implemented to aid power saving and avoid unintended wakeup due to ambient noise.

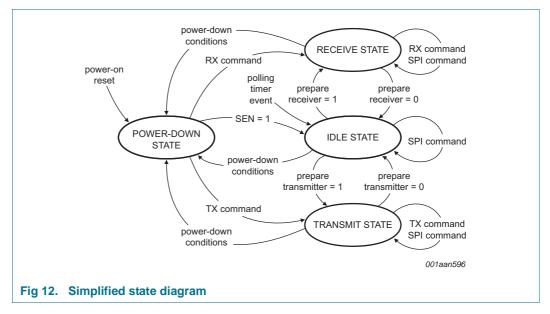

#### 7.2 General operation

The OL2381 is a state machine-based transceiver to be used in conjunction with a microcontroller. Study this datasheet carefully to help choose the appropriate OL2381 configuration for a specific application. The interface to the microcontroller must be defined first, see Section 7.3. Next, the correct basic settings must be identified. The operational frequency band must be chosen, all relevant registers must be programmed for TX and RX modes (exact setting of desired frequency, modulation, modulation depth, IF bandwidth, baseband filtering, etc). It is strongly recommended to study every aspect of this datasheet in detail and to verify correct device operation by measuring available debug-signals. The optimum operation and the highest device performance is achieved by fine-tuning and verification of all device settings. Use the automatic operating sequences after determining the optimum device configuration. Generally, the first operation is to bring the device from standby to power-up state, which is the precondition for any operation. This can be done manually, triggered by the external microcontroller, or automatically by the built-in polling timer. In this device mode, the XTAL oscillator is operational. SFR register bits (configuration data) can be changed. This mode can be left by issuing TX or RX commands. To save power and operating time the commands can be prepared by the 'prepare TX' or 'prepare RX' commands.

#### 7.3 Interface description

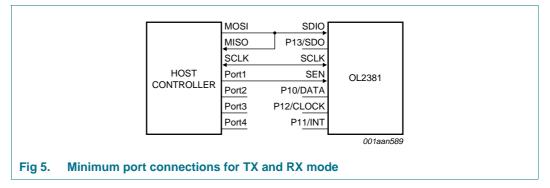

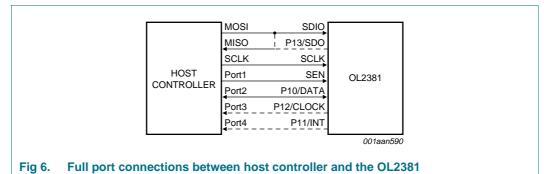

#### 7.3.1 Port connections

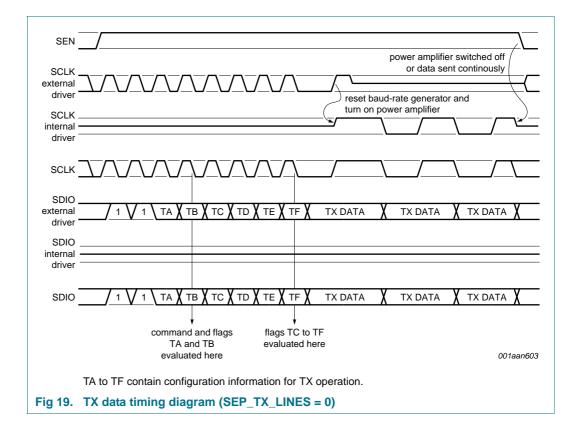

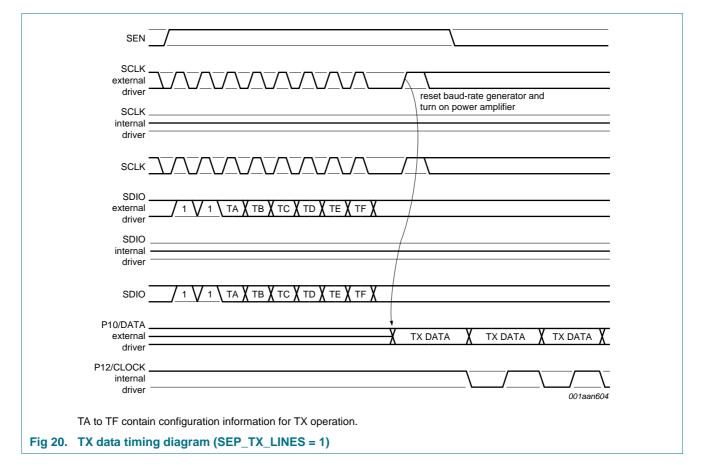

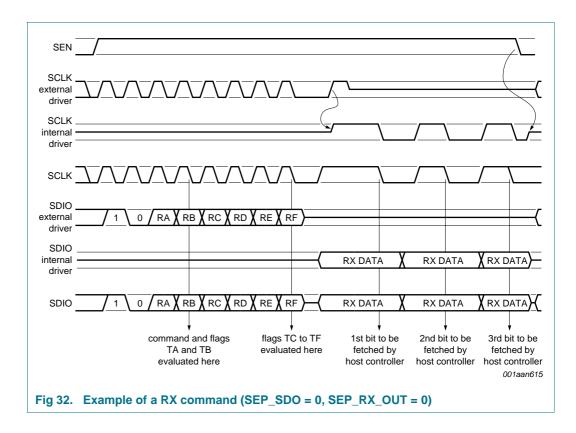

The minimum connection between a host controller and the OL2381 comprises three SPI lines: SDIO, SCLK and SEN. SPI communication and TX/RX data transfer can be achieved by multiplexing the SPI data and clock lines. The host controller's SPI must be set in slave mode after the RX/TX command is sent, the SCKL then shifts the out/in data via the host controller's SPI.

The device also supports full four-line SPI mode, the line SDIO serving as data input and P13/SDO as data output.

Alternatively, the device can be configured for separate data inputs and outputs. The lines SDIO, SCLK and, if selected, P13/SDO can be reserved for SPI command handling. In this case, TX and RX data is handled by the port pin P10/DATA, the clock is carried by port P12/CLOCK. The OL2381's remaining ports can be used for additional status information.

#### 7.4 Special ports

#### 7.4.1 TEN

The test enable input (pin TEN) must always be connected to GND. This pin is only required for a factory test and has no user-operable functionality.

#### 7.4.2 TEST1, TEST2 and TEST3

Test pins for internal analog test-signals. In the application, these pins must be left open.

#### 7.4.3 **RSTDIS**

The status of pin RSTDIS defines the polling timer state enable bit after power on. When the pin is LOW, the device is initialized with the polling timer enable bit set to 1.

#### 7.5 General purpose ports

The device features five general purpose ports: P10 to P14, with selectable dedicated user functions; see <u>Section 7.8.3 "Reset and power mode register" on page 16</u>. The port function is controlled by bits P1xCx. The width of these control bits for every port depends on the number of selectable signals.

All general purpose ports, except P11/INT and P12/CLOCK, are in 3-state after power-on reset. Port P11/INT is initialized as an output driving the active-LOW POR interrupt. Note that this interrupt is non-maskable.

Port P12/CLOCK is initialized to provide a 1 MHz reference clock as the default output.

#### 7.5.1 P10/DATA

Priority of functions:

- Output signal of receiver debug interface

- RX data output, if bit SEP\_RX\_OUT is logic 1 and the receiver is activated

or

• TX data input when bit SEP\_TX\_LINES is logic 1 and the transmitter is activated

If register PORTCON2 bit SEP\_TX\_LINES is set and P12C[2:0] = 010b, the port delivers the TX clock as specified through register TXCON. This clock is activated after the TX command's ninth SCLK pulse and it runs until the power amplifier is turned off. This clock indicates the TX timing and informs the controller when the device samples the input data from the P10/DATA line.

If register PORTCON2 bit SEP\_RX\_OUT is set and if P12C[2:0] = 010b, the port delivers the RX clock associated with the data provided at P10/DATA. This clock is activated after the RX DATA command's ninth SCLK pulse. If the RX command is a PRDA, this clock is activated after successful preamble detection. In both cases the clock continues as long as the receiver state machine is in its DATA state. This clock is recovered from the RX signal timing and informs the controller when it can sample the data delivered at the P10/DATA line.

Note that in contrast to P10/DATA, where setting bit SEP\_TX\_LINES or bit SEP\_RX\_OUT overrules the normal port function, this is not the case for P12/CLOCK. The clock is only output if selected when P12C[2:0] = 010b.

Bit P10INV inverts output data, including RX data. If an inversion of TX data is desired, register TXCON's bit INV\_TX\_DATA must be used.

#### 7.5.2 P11 and P12

P11 and P12 together with P10, form the serial interface when the receiver debug mode is activated; see <u>Section 7.41 "RX debug interface" on page 85</u>.

#### 7.5.3 P14

P14 can be used to control an external circuit, such as a TX/RX switch or an LNA.

#### 7.6 Serial configuration interface description

#### 7.6.1 General SPI information

The chip is configured via a three or 4 wire serial interface consisting of an 8-bit shift register and  $80 \times 8$ -bit registers holding the configuration data.

Data can be exchanged with multiple 8-bit frames (auto-incrementing) or in portions of 8 bits (1 byte), which provides an advantage when using a hardware SPI-interface. Data in the shift register is loaded into the addressed register on the last edge of SCLK within the last bit of the transferred byte.

#### 7.6.2 SEN

A logic LOW applied to pin SEN disables the SPI interface. The internal state machine halts and every activity on pins SDIO and SCLK is ignored.

If the device is in Power-down mode, a positive edge on pin SEN activates the device. The crystal oscillator is always on, unless the device is in Power-down mode. The watchdog is cleared with a HIGH level on pin SEN; see <u>Section 7.11 "Watchdog" on page 25</u>.

After the TX command, pin SEN has an additional function: At the falling edge of pin SEN the level on pin SDIO is latched and frozen.

#### 7.6.3 SCLK

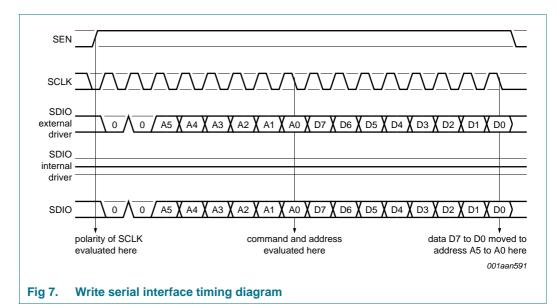

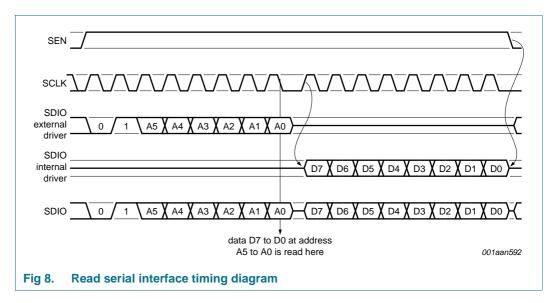

SCLK is the clock pin for the serial interface. Every edge of SCLK shifts data into or gets data from the SPI register-set. The second clock edge (SCLK) is used for data capturing. SDIO direction switching between input and output is accomplished with the first clock edge of the ninth bit. An additional clock edge is necessary at the start of a TX or RX command.

The clock polarity for an SPI command can be selected; see Section 7.6.5.

If desired, pin SCLK can carry the baud-rate clock during a TX command and the recovered RX clock during a RX command.

#### 7.6.4 SDIO

SDIO is the serial interface's bidirectional data input/output pin. Data in or data out operation is adapted automatically during SPI communication sequences.

If desired, pin SDIO can be used to input data if a TX command is executed or for RX data if a RX command is active.

#### 7.6.5 General SFR access information

If SCLK is HIGH at the rising edge of SEN, the data is transferred with the rising edge of SCLK; see <u>Figure 7</u> and <u>Figure 8</u>. If SCLK is LOW at the rising edge of SEN, the data is transferred at the falling edge of SCLK.

For continuity, all figures and examples in this data sheet assume SEN is LOW at the rising edge of SCLK, unless otherwise stated. The first edge of SCLK is referred to as the rising edge and the second as the falling edge.

#### 7.7 Write and read access to SFR

#### 7.7.1 Write access to SFR

#### 7.7.2 Read access to SFR

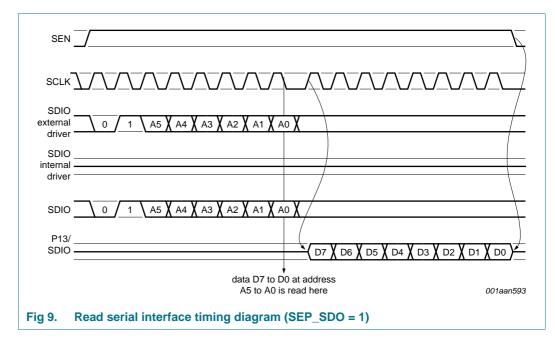

#### 7.7.3 Separation of SDI and SDO line

A four-wire SPI interface can be implemented using pin SDIO for MOSI and pin P13/SDO for MISO. Timing and output control of pin SDO is the same as for the internal SDIO driver.

#### 7.7.4 Read access to SFR with separate SDO line

#### 7.7.5 Read and write access to SFR with auto-increment function

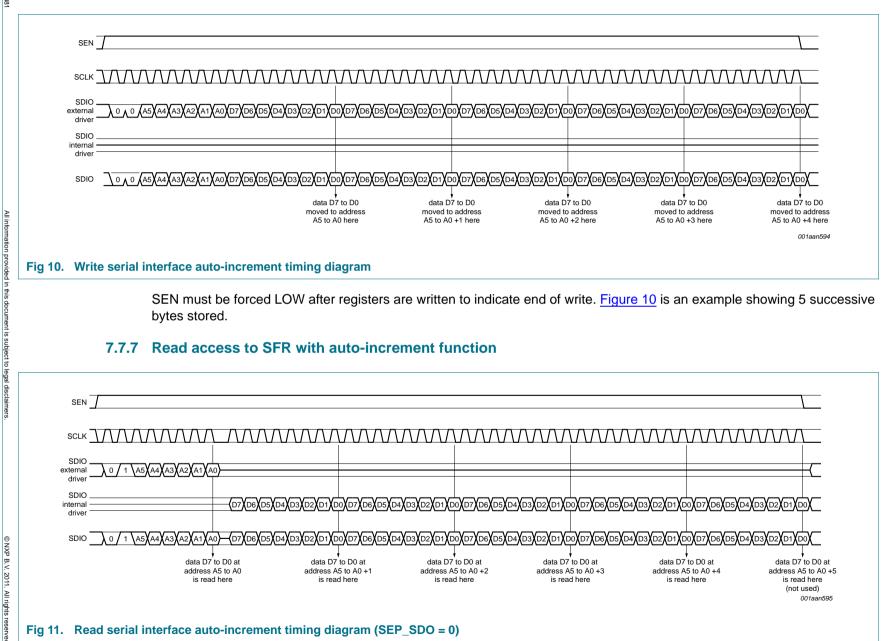

If the SPI clock (SCLK) is still applied after the first 8 data bits are transferred, the auto-increment function automatically increments the address by one for the following 8 data bits. This enables data to be written to a continuous range of bytes without having to set the address for every single data-byte. The auto-increment function is terminated on the falling edge of SEN.

If the address reaches the end of the address range (3Fh) an additional increment causes the address to start at 00h again. This wrap around is accomplished in the current address bank. The auto-increment function has no influence on the bank selection.

Highly integrated single-chip sub

GHz

**RF** transceiver

.2381

#### 7.7.6 Write access to SFR with auto-increment function

OL2381 Product data sheet

Rev. \_ 5 30 November 2011 lega

All rights

SEN must be forced LOW after registers are read to indicate end of read. Figure 11 is an example showing 5 successive bytes read.

#### 7.8 Device mode description

#### 7.8.1 Automatic start-up procedures

The device features the following automatic start-up procedures for easy device handling and configuration:

- Power-on and crystal oscillator start-up

- PLL and VCO start-up including calibration

- Preparation for TX mode

- Preparation for RX mode

- VCO auto-calibration at every center frequency change

#### 7.8.2 General description

The automatic start-up procedures are implemented to aid the quick and easy transition between operational states. Most procedures are controlled by changing bits in the PWRMODE register. Certain configurations can be directly entered by the TX or RX commands.

#### 7.8.3 Reset and power mode register

The PWRMODE register acts as the device's 'main power on/off/standby switch'. Setting the RESET bit of this register brings the device into the reset condition equal to the power-on reset state. This power-down state is also reached automatically at first power-on (battery insertion). If this bit is set with a write command, the effect on all registers with a reset condition is a 'hard-reset'. If, with the same SPI write command, other bits are simultaneously written to the PWRMODE register, they are changed automatically to the power-on reset state; see <u>Section 8.2.1.10 "General power mode register PWRMODE" on page 100</u>.

#### 7.8.3.1 First power-on reset

The non-maskable interrupt flag IF\_POR is set when the initial power-on reset takes place (battery insertion).

#### 7.8.3.2 Power-down

Setting bit PD brings the device into low current consumption standby mode. All analog receiver and transmitter circuitry including the crystal oscillator are turned off and all dynamic digital activity is stopped. Only the SPI and the polling timer, if enabled, are active. Bit PD is also under automatic device control and is set under the following conditions:

- power-on reset or setting bit RESET (setting bit RESET overrides all others)

- the watchdog timer times out

#### 7.8.3.3 Device mode states

Three important static device internal enable signals are decoded from DEV\_MODE: PLLEN, TXEN and RXEN.

- PLLEN is set whenever the DEV\_MODE is not logic 00

- RXEN is set only if DEV\_MODE is logic 10

- TXEN is set only if DEV\_MODE is logic 11

An important implication of this is that a TX operation is immediately aborted if the active mode is switched to anything except TX mode, for example, switching the device into RX mode immediately shuts down the power amplifier without smoothly ramping down the RF power.

Conversely, entering TX mode immediately aborts any RX operation.

DEV\_MODE bits can be either set directly by writing the PWRMODE register or by sending a RX or a TX command, where a RX command sets DEV\_MODE to logic 10 and a TX command sets DEV\_MODE to logic 11.

Setting bit RESET or setting bit PD (power-down) resets DEV\_MODE to logic 00, where only the crystal oscillator is (potentially) enabled.

An alternative to setting the device mode can be to send a TX command and delay the '9th edge'. This sets the frequency and initiates the device as if in TX mode. The PA is then switched on at the TX command's 9th edge.

#### 7.8.4 Flow description

The following actions are performed if the device leaves power-down state and enters active state. The internal control signals of these states are explained in more detail in later sections.

Power-down state indicator is cleared.

#### 7.8.4.1 Digital regulator start-up

The digital voltage regulator is turned on whenever the device leaves the power-down state.

#### 7.8.4.2 XTAL oscillator start-up

The crystal oscillator or the buffer for the external clock is turned on depending on the states of CLOCKCON register bits XODIS and EXT\_CLK\_BUF\_EN.

Bit XO\_RDY is logic 1 once the crystal oscillator has settled. The device waits for several clock periods until the clock output's frequency and duty cycle have fully settled to within the required specification. The end of this waiting period is indicated by bit REFCLK\_RDY changing to logic 1. This enables the master clock gate at the root of the clock distribution tree and if applicable, the reference clock for the digital section is enabled. A polling timer recalibration is also initiated at this point.

#### 7.8.4.3 PLL start-up

This sequence is controlled by the internal control signal PLLEN. The voltage regulators for the PLL and VCO (REG\_VCO\_ON, REG\_PLL\_ON) are turned on.

Wait until the voltage regulators have settled. This sequence ends, if LO\_PWR\_RDY = 1.

#### 7.8.4.4 Turn on VCO

The phase frequency detector (PFD\_ON), prescaler (PRESC\_ON), clock for the PLL (CLK\_PLL\_ON) and PLL lock detection are turned on with the next clock cycle.

#### 7.8.4.5 Perform VCO calibration

This sequence is complete once the PLL is locked (LO\_RDY is set). A manual VCO calibration immediately stops any TX or RX command.

#### 7.8.4.6 Preparation for TX mode

This mechanism is invoked by issuing device mode logic 11 (prepare for TX) or by sending a TX command.

The voltage regulator for the power amplifier (bit REG\_PA\_ON) and the VCO clock divider for transmitter path (bit TXON) are enabled.

This sequence ends if the power amplifier's regulator started properly (brown-out detection not active).

#### 7.8.4.7 Preparation for RX mode

This mechanism is invoked by issuing device mode logic 10 (prepare for RX) or by sending a RX command.

The bandgap reference circuit for the receiver section (bit RX\_GAP\_ON), VCO clock divider for the receiver section (bit PLL\_LOCK), reference clock for the RX path (bit CLK\_RXA\_ON), and the analog section of receiver (bit RXA\_ON) are enabled.

#### 7.8.4.8 Perform channel filter calibration

The channel filter calibration is performed every time the device enters RX mode. This sequence ends if the channel filter calibration ends.

#### 7.8.5 Changing device modes

Intermediate device modes may be required in an operation sequence e.g. start digital regulator and XTAL to initialize/change SFR contents or to re-trim the polling timer. This can be carried out by changing the corresponding registers. However, the direct

commands may be more useful if the only operation required is the entering of TX or RX mode. The corresponding sequences start automatically and operation enabled after all internal settling times are met.

#### 7.8.6 Interrupts

TheOL2381 can generate various interrupts which can be enabled by the IEN register and read from the IFLAG register; see <u>Section 8.2.1.11 "Interrupt enable register IEN" on page</u> <u>101</u>. The IFLAG register is always cleared after it is read. Certain pins can also be configured to present these interrupts; see <u>Section 7.3 "Interface description" on page 9</u>.

#### 7.9 Power supply and reset

Each main functional block is equipped with its own dedicated supply voltage pin. Therefore, several supply pins are available on the package and all must be connected. Note that all ground connections of these functional blocks are bonded to the exposed die pad of the package (metal plate underneath the die). Some blocks are supplied via dedicated integrated low-dropout voltage-regulators. Note that for all regulators the output voltage is available both internally and externally on a pin for connection of a decoupling capacitor. The following blocks have regulated supplies.

| Table 3. | BIOCKS with regulated supplies |                 |

|----------|--------------------------------|-----------------|

| Block    | Regulator supply pin           | Pin to decouple |

| PLL      | VCC_REG                        | VREG_PLL        |

| VCO      | VCC_REG                        | VREG_VCO        |

| PA       | VCC_PA                         | VREG_PA         |

| digital  | VCC_DIG                        | VREG_DIG        |

|          |                                |                 |

#### Table 3. Blocks with regulated supplies

#### 7.9.1 Voltage regulators operation

All regulators are operated automatically by selecting the corresponding device modes. The device modes are set by DEV\_MODE[1:0] in register PWRMODE; for details see Section 7.8.3 "Reset and power mode register" on page 16.

The regulators can also be independently controlled by the control bits located inside the TEST registers. Individual operation of the voltage regulators can be necessary for debug or measurement purposes. The following paragraphs describe each individual regulator and its purpose.

#### 7.9.2 Digital regulator

Before the device can be operated, the digital regulator must be switched on. In standby state (power-down state) the digital regulator is bypassed and supplies the digital section with a low supply voltage to guarantee data retention in the configuration registers. If the digital regulator is switched on, the voltage reaches its stabilized value of approximately 1.8 V. The digital regulator can be activated or deactivated by bit REG\_DIG\_DIS in TEST1 register. Clearing the bit enables the regulator, depending on the selected device mode. Setting the bit always disables the regulator.

#### 7.9.3 PLL regulator

To start any PLL operation the PLL regulator must be switched on. This happens automatically with operation of bit REG\_PLL\_ON in the TEST2 register.

DL2381

**Remark:** this bit only starts the PLL regulator, all PLL functional blocks are enabled individually by separate control-bits.

#### 7.9.4 VCO regulator

For stability and immunity reasons the VCO is supplied via an independent voltage regulator. This regulator can be manually controlled via bit REG\_VCO\_ON in the TEST2 register.

**Remark:** this bit only starts the VCO regulator. VCO operation is enabled individually by a separate control-bit.

#### 7.9.5 PA regulator

This regulator is enabled if PA operation is desired. This can be manually controlled by setting bit REG\_PA\_ON.

**Remark:** this bit only starts the PA regulator. TX operation must be enabled by setting the corresponding command on the SPI interface.

#### 7.9.6 Device reset

A device reset occurs whenever the supply voltage is applied on the VCC pins (battery insertion). The device utilizes two power-on detection mechanisms, one digital and one analog. These reset circuits constantly monitor the supply voltage. Setting bit RESET in the PWRMODE register performs the same operation by software. This is equivalent to a power-on reset. If bit RESET is set via a command, it is cleared automatically when SPI signal SEN goes LOW after the next write register command.

#### 7.10 Main control and timing blocks

#### 7.10.1 Crystal oscillator

#### 7.10.1.1 Circuit description

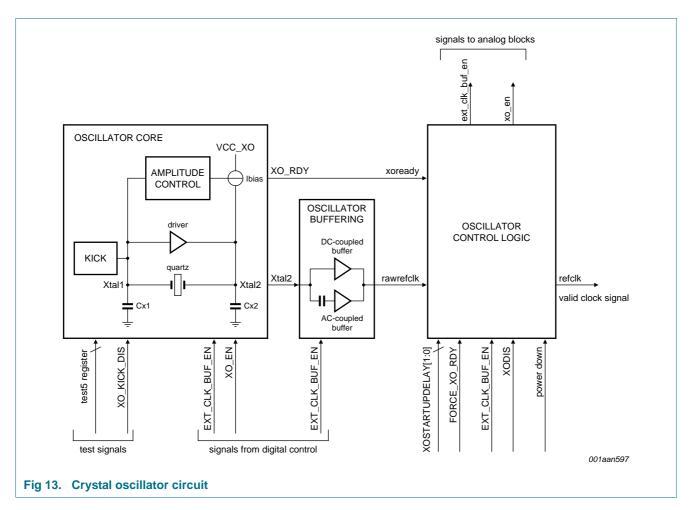

The crystal oscillator is the source of the reference clock for the PLL, the digital section and the mixed signal blocks in the receiver chain. The crystal oscillator circuit diagram is shown in Figure 13.

OL2381 Product data sheet

### **NXP Semiconductors**

# **OL2381**

Highly integrated single-chip sub 1 GHz RF transceiver

The crystal oscillator consists of three main blocks: the oscillator core, the oscillator buffer and the oscillator control logic.

The oscillator core is a low power quartz based Pierce oscillator. The oscillation frequency is defined by the quartz and the tuning capacitors CX1 and CX2. The driver's low capacitance has negligible impact on the frequency value. The oscillator core is supplied by pin VCC\_XO.

When the oscillation starts and the amplitude successfully detected, the amplitude control releases the signal XO\_RDY to the oscillator control logic for validation. This signal indicates that the amplitude control loop has entered regulation mode and not that the oscillator has settled. An extra delay is still needed to ensure the frequency accuracy; see Table 116 "XOSTARTUPDELAY bit functions" on page 124.

After start-up, the amplitude control avoids clipping and excessive driving power in the crystal unit.

The oscillator control logic validates the oscillator signal and provide configuration facilities. The oscillator control logic is supplied by the digital regulator to the level VREG\_DIG.

The oscillator buffer consists of two amplifiers connected in parallel: one low-noise AC-coupled amplifier for crystal operation and one high-input voltage DC-coupled amplifier for testing purposes only. The buffer plays the role of level-shifter for the signals in PLL and digital supply domains. The buffer circuitry is supplied by the PLL and digital regulators accordingly.

Alternatively, an external clock signal can be applied at pin XTAL2; see the external clock buffer description in <u>Section 7.10.2</u> "Oscillator control and control bits" on page 23. The applied signal must comply with the logic levels in the digital core (0 V for LOW and 1.8 V for HIGH). With the OL2381 properly configured, the DC-coupled amplifier replaces the low-noise AC-coupled amplifier. This provides the possibility to skip the internal oscillator's start-up sequence and also allows the customer to stop the clock sequence for test purposes.

**Remark:** The use of an external clock signal requires special care in the hardware configuration. The oscillator core circuitry connected to pin XTAL2 cannot withstand levels higher than 2.8 V. Therefore, the use of this test mode with supply voltages higher than 2.8 V requires a hardware modification for pin VCC\_XO. The recommended solution is to connect pin VCC\_XO to pin VREG\_DIG. In that configuration the circuit's integrity is ensured but the digital noise needs to be considered.

The crystal oscillator is always active either in oscillator mode or in external clock buffer mode when the device is not in Power-down state.

OL2381

22 of 152

**NXP Semiconductors**

Highly integrated single-chip sub 1 GHz RF transceiver

2381

#### 7.10.2 Oscillator control and control bits

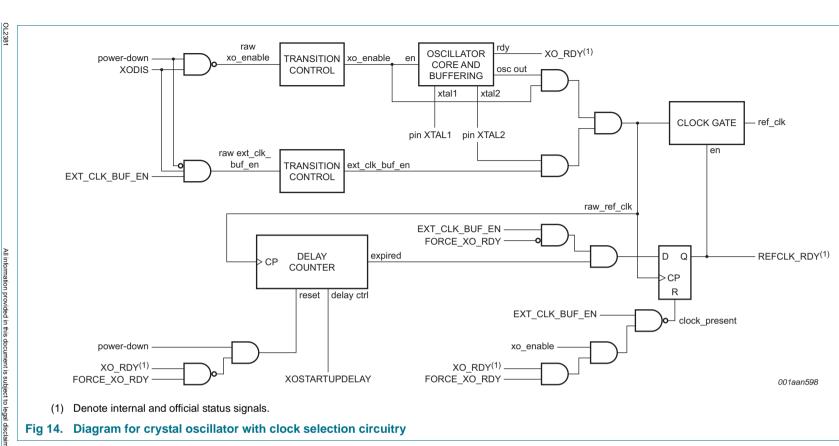

The oscillator control logic is described in <u>Figure 14</u>. Upper case signal names denote control bits in the OL2381's register set. Upper case signal names labeled '(1)' denote (internal and 'official') status signals. Lower case signal names denote internal signals.

The enable logic is visible at the top left corner for both modes: the crystal oscillator mode and the external clock buffer mode. The crystal oscillator is turned on when both, power-down and XODIS, are false. The transition control ensures that no glitches can be generated when turning the oscillator on and off. The external clock buffer is turned on when the device is not in power-down mode and both control bits, XODIS and EXT\_CLK\_BUF\_EN are set; see <u>Section 8.2.1.15 "Clock</u> <u>connection register CLOCKCON" on page 103</u>. As a consequence, putting the device in power-down mode disables all clock activity, and turning the crystal oscillator on has priority over turning the external clock buffer on.

# Rev. 1 — 30 November 2011

Product data

i sheet

If the crystal oscillator is turned on (XO\_ENABLE becomes true) and a crystal is connected to the oscillator, the raw clock becomes available after the oscillation reaches a significant amplitude, which is then signaled with the internal XO\_RDY status signal. This internal status signal can be routed to pin P12/CLOCK for observation. While the crystal oscillator is disabled, it is ensured that the clock from this clock source is held at the zero level.

If the external clock buffer is activated (bit EXT\_CLK\_BUF\_EN is true) the signal connected to pin XTAL2 is taken as the clock source. While the external clock buffer is disabled, it is ensured that the clock from this clock source is held at the zero level.

Since only one clock source can deliver a clock at a given time they can be easily merged. The clock is only fed into the circuit when the clock gate is enabled. The following paragraphs explain the conditions for enabling this clock gate separately for each clock source.

When using the crystal oscillator, the delay counter, in Figure 14, is held in reset state during Power-down mode or if both, the internal status signal XO\_RDY and the expert control bit FORCE\_XO\_RDY, are false. If the oscillator signals XO\_RDY after start-up (or if the FORCE\_XO\_RDY is set), the delay counter is released from reset, which lets it count the raw clock pulses from the oscillator. Note that counting will not occur if the oscillation amplitude is too low or if the clock pulses are too 'thin' (duty cycle near 0 % or near 100 %). Therefore it is ensured that the delay counting will not start before the raw clock has a usable shape. After a programmable count (Table 116 on page 124) is reached, the counter stops and signals the end of the delay.

The digital oscillator start-up delay can be controlled by bits XOSTARTUPDELAY[1:0] in register EXPERT1.

After the delay counter's end status reaches the REFCLK\_RDY flip-flop, (shown at the lower right corner of Figure 14), it is sampled by the raw clock, now stabilized, and this declares the reference clock ready. This also enables the clock gate which passes the clock on to the circuit starting with the following clock pulse. The REFCLK\_RDY status flip-flop is immediately reset when the raw clock is no longer present, which happens when the crystal oscillator is turned off or bit XO\_RDY is false due to any reason which may have stopped the oscillation.

Note that special care is needed when non-recommended crystals are used. The use of non-recommended crystals and resonators may have a negative impact on the start-up behavior, on the frequency stability and on the PLL noise performance.

The oscillation amplitude is always large enough for recommended crystals so the amplitude control can properly detect that the start-up and noise generated by the AC-coupled buffering is appropriate for PLL operation.

If the crystal is replaced by a resonator with a low Q factor, the resulting amplitude may not be large enough for the XO\_RDY status to be properly detected, although the generated clock may still be usable. To use the OL2381 under such conditions, the XO\_RDY status must be overridden by using the expert control bit FORCE\_XO\_RDY. Note that the delay counting mechanism will not start counting before the raw clock reaches a certain quality.

OL2381

24 of 152

If the external clock buffer is used, it is assumed that the clock source, which is connected to pin XTAL2, provides a stable clock with a duty cycle close to 50 % at the time when bit EXT\_CLK\_BUF\_EN is set. Therefore the delay counter is not needed in this case. But even without the delay counter, the circuit provides a well-controlled startup sequence, which is enforced by the REFCLK\_RDY flip-flop and the clock gate, so that no glitches are generated when the clock buffer is turned on or off. Note that not using the delay counter in this normal case requires the FORCE\_XO\_RDY expert control bit to be in the cleared state.

However, if bit FORCE\_XO\_RDY is set when using the external clock buffer, the delay mechanism is activated. This is how the delay counter is tested in the production test but it may also help to overcome start-up problems in the external clock source. The XO\_RDY, REFCLK\_RDY signals can be observed for oscillator testing via the test buffer. The resulting clock can be probed at pin CLOCK.

#### 7.11 Watchdog

The device features a watchdog timer to recover from situations when activation is not desired. The watchdog timer runs with the reference clock and it is activated, if the device is not in Power-down mode.

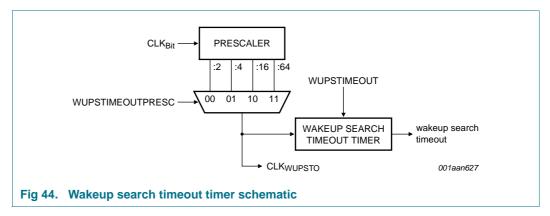

The watchdog is cleared and temporarily stopped under the following circumstances:

- Pin SEN is HIGH

- A terminating wakeup search is executed, i.e. either a pessimistic wakeup search is activated (bit WUPSMODE = 0) or the timer for the wakeup search is activated during an optimistic wakeup search (bit WUPSMODE = 1 and bits WUPSTIMEOUT not equal to 0).

- A terminating preamble detection is executed, i.e. the timeout for the preamble must be activated (bit EN\_PREADET\_TIMEOUT = 1 and bits WUPSTIMEOUT not equal to 0).

Bit EN\_PREADET\_TIMEOUT can be found in register SIGMON1; see <u>Section 8.2.2.2</u> "Signal monitoring control register SIGMON1" on page 115. Bit WUPSMODE can be found in register SIGMON0; see <u>Section 8.2.2.1</u> "Signal monitoring register SIGMON0" on page 114. Bits WUPSTIMEOUT can be found in register WUPSTO; see <u>Section 8.2.2.4</u> "Register WUPSTO" on page 116.

The watchdog timeout can be adjusted according to Equation 1.

$$watchdog timeout = \frac{{}_{2}15 + WUPSTIMEOUT}{CLK_{REF}}$$

(1)

where:

$CLK_{REF} = 16 MHz$

watchdogtimeout = desired watchdog timeout

It is not possible to turn off the watchdog completely. The watchdog can be disabled for an arbitrary period only if pin SEN is set HIGH.

#### 7.12 Polling and wakeup timer

The device features a low power oscillator, which can be used to generate wakeup events. A polling timer overflow always generates an interrupt request. Moreover, if selected, the device can be automatically released from the Power-down state and it can enter the RX state.

The low power oscillator has a nominal period of 40  $\mu$ s and a tolerance of  $\pm$  50 % over the entire temperature and supply voltage range and over process-dependent device spread.

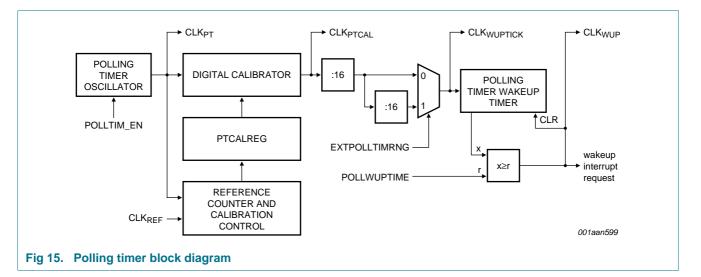

The polling timer employs a digital calibration with a modulo counter. The crystal oscillator clock  $CLK_{REF}$  is used as a reference clock for the calibration. The calibration procedure measures one period of the polling timer clock  $CLK_{PT}$  and determines the appropriate calibration value for the modulo counter. The output clock  $CLK_{PTCAL}$  has a nominal period of 62.5  $\mu$ s.

The polling timer can be turned on and off with bit POLLTIM\_EN in the PWRMODE register. The state of this bit after a master reset is determined by the level on pin RSTDIS.

Note that due to the absence of the reference clock it is not possible to trim the polling timer directly after a master reset. The calibration register PTCALREG is set to its nominal value after a master reset.

After exiting Power-down mode, the polling timer calibration is triggered automatically if the crystal oscillator starts properly. It is also possible to trigger a manual calibration by setting bit MANUALPTCAL. Setting this bit generates a short pulse, which starts the calibration routine. Reading bit MANUALPTCAL always yields zero. The manual calibration is only executed if the polling timer and the crystal oscillator are running otherwise the request is ignored. Setting bit MANUALPTCAL at the same time as POLLTIM\_EN is not supported. The calibration is only performed after the polling timer oscillator settles.

The value in the calibration register is consistent under all circumstances. This must also be the case if a running calibration is interrupted. Direct read or write access to register PTCALREG is not supported.

)| 2381

(2)

The polling timer wakeup time can be set with the 8-bit control register POLLWUPTIME. The wakeup time calculates to:

$$T_{WUP} = (POLLWUPTIME + 1) \times T_{WUPTICK}$$

The achievable resolution and wakeup times can be selected in two different ranges, a normal and an extended polling timer range according to the setting of bit EXTPOLLTIMRNG in the CLOCKCON register.

It is possible to change the register POLLWUPTIME while the polling timer is running. If the new value is greater than the polling timer counter's current content, the running period is not interrupted and the newly set wakeup time is seamlessly adjusted. This mechanism allows the setting of a new wakeup time with respect to the last wakeup event. If the newly set value in register POLLWUPTIME is smaller than the polling timer counter's current content, the counter is reset immediately.

The digital calibration is implemented so that the accuracy of wakeup times greater than 10 ms is better than 1 %. This allows an overall timing error of less than 2 % for the given range.

#### 7.12.1 Actions at polling timer wakeup

Register POLLACTION defines which action the device carries out after a polling timer event; see <u>Section 8.2.1.14 "Polling action register POLLACTION" on page 102</u>.

POLL\_MODE[1:0] defines the device's operating mode after a polling timer event.

RX\_GAIN[1:0] means the same as the RX flags RE and RF (gain step/switch selection bits). The RX\_CMD bit means the same as RX flag RC. It allows a choice between a WUPS (0) and a PRDA command (1). RX\_FREQ[1:0] means the same as RX flags RA and RB (frequency selection).

The last bit in the POLLACTION register, SET\_RX\_FLAGS, defines whether the RX flag register's current content is used for the automatically initiated RX command (if 0) or whether the RX flags RA, RB, RC, RE and RF flags are overwritten with the contents of the RX\_FREQ, RX\_CMD and RX\_GAIN bit settings of this register, respectively, before the command is actually launched (if 1). If the flags are overwritten, RX flag RD is set to logic 1 to make the sub-command either a WUPS or a PRDA command; see <u>Section</u> 7.32.2 "Receive command" on page 55 for more information.

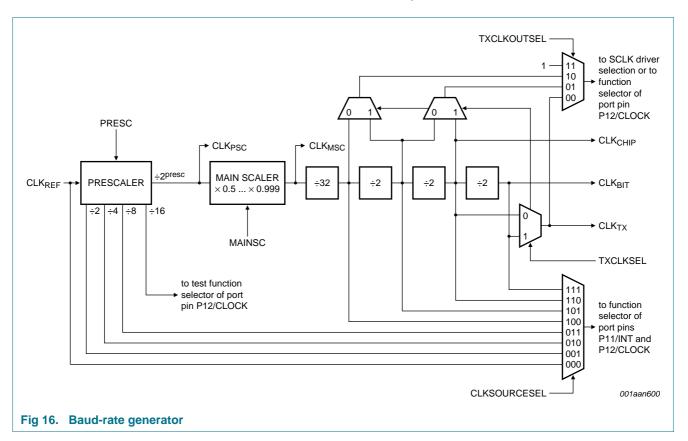

#### 7.13 RX and TX baud-rate generator

The baud-rate generator generates the nominal, unsynchronized chip clock according to Equation 3.

$$b \, aud \, rate = \frac{16 \, MHz}{2^{PRESC}} \times \frac{2^{11} + MAINSC}{2^{12}} \times \frac{1}{128} \tag{3}$$

where PRESC is an exponent in the range from 0 to 7, and  $2^{11}$  + MAINSC is the mantissa in the range 2048 to 4095. The resulting baud-rate clock can jitter by one prescaler clock cycle CLK<sub>PSC</sub>.

The mainscaler MAINSCL lower bits can be found in register TIMING0.

All information provided in this document is subject to legal disclaimers.

The MAINSCH and the PRESC bits can be found in register TIMING1; see <u>Section</u> 8.2.1.5 "Timing register TIMING1" on page 95.

The divide-by-128 divider is used as a 'clock' for several other blocks to measure the sub-timing within one chip interval.

This baud-rate generator is used as the time reference for a synchronized TX operation and as a time reference for the clock-recovery in RX mode.

Calculation of clock in TX mode is shown in Equation 4.

$$CLK_{TX} = \frac{CLK_{REF}}{2^{PRESC}} \times \frac{2^{11} + MAINSC}{2^{12}} \times \frac{1}{128} \times \frac{1}{2^{TXCLKSEL}}$$

(4)

where  $CLK_{REF} = 16$  MHz.

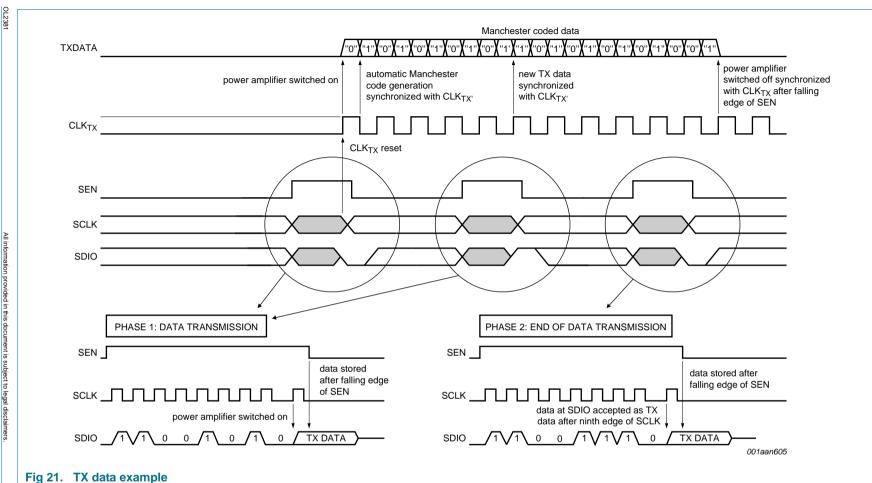

Bit TXCLKSEL can be selected whether the chip clock  $CLK_{CHIP}$  or the bit clock  $CLK_{BIT}$  is used as the TX clock. If automatic Manchester generation is required, the bit clock must be selected.

Bits CLKSOURCESEL are in register CLOCKCON; see <u>Section 8.2.1.15 "Clock</u> connection register CLOCKCON" on page 103.

Bit TXCLKSEL is in register TXCON; see <u>Section 8.2.1.23</u> "Transmitter control register TXCON" on page 107.

#### 7.13.1 Clock recovery for RX mode

The clock-recovery for RX mode is dependent on the baud rate accuracy. If the absolute correct baud rate cannot be selected, choose the next available integer value. The clock recovery is able to cope with a 1 % tolerance to be able to operate correctly with standard XTAL cutting and temperature inaccuracies. The clock recovery is implemented as a digital phase control loop with a fixed operating frequency determined by the baud-rate generator setting. The baud-rate generator's mainscaler clock acts as the reference clock for the clock-recovery PLL (128 times the actual chip clock). The clock recovery PLL is programmable with regards to its settling speed. The settling of the clock-recovery speed can be set to reach its final state within 3, 7, 15 or 31 chips. If the clock-recovery is locked to the bit-stream the actual possible phase-error is proportional to the selected settling speed setting. Highest settling speed (settling within 3 chips) produces the smallest actual phase error due to fast regulation; slowest speed (settling within 31 chips), allows for the largest phase error due to the slowest regulation time constant; see Table 103 "CLOCK\_RECOV\_TC bit functions" on page 118.

Note that the decoding of NRZ signals with long constant bit-periods is directly influenced by the accuracy of the selected baud rate. Proper coding can significantly improve sensitivity and the BER of NRZ decoding.

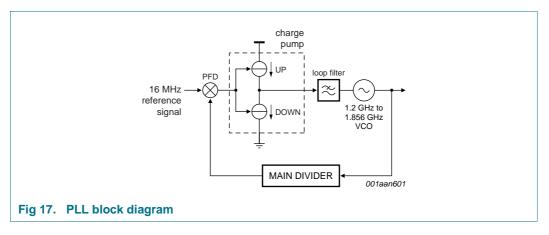

#### 7.14 Phase-locked loop

A complete on-chip PLL is available to provide an RF carrier in both RX and TX modes. The PLL is a 4th-order fractional-N PLL. The PLL analog section is described in <u>Section 7.14.1</u> and the PLL digital section is described in <u>Section 7.14.7</u>.

#### 7.14.1 PLL building blocks

All PLL building blocks except bit VCO\_BAND in register LOCON and the charge pump reference current (PLL\_ICP[4:0]) settings are automatically configured and operated by selecting the corresponding device modes. The following paragraphs describe the function of the internal control signals. These control signals can be influenced, if desired, by operating control bits located in the EXPERTn and TESTn registers.

#### 7.14.2 PLL and VCO regulators

To operate the whole PLL, both regulators must be switched on; see <u>Section 7.9.3 "PLL</u> regulator" on page 19.

#### 7.14.3 General PLL operation

The following blocks are enabled after switching on the regulators so that the entire PLL is operational: VCO (VCO\_ON), phase-detector (PFD\_ON), prescaler (PRESC\_ON) and reference clock buffer (CLK\_PLL\_ON), depending on the selected mode of operation (RX or TX mode, selected via device mode or command); eventually RX\_ON must be also set. If this bit is set to logic 1, the RX LO dividers are activated.

#### 7.14.4 Charge pump

This block delivers the charge to the loop filter. The polarity and amount of charge are proportional to the phase error reported by the phase detector.

The peak current of this charge pump is automatically adjusted. It can be overridden by PLL\_ICP[4:0] in register EXPERT0; see <u>Section 8.2.4.1 "Register EXPERT0" on page</u> <u>124</u>. The charge pump peak current is a function of the icp control bits: icp[0] \* 15  $\mu$ A + icp[1] \* 30  $\mu$ A + icp[2] \* 60  $\mu$ A + icp[3] \* 120  $\mu$ A + icp[4] \* 240  $\mu$ A.

This means that a value from 15  $\mu$ A up to 465  $\mu$ A can be selected. The purpose of this programmability is to compensate for gain variation in other blocks, especially RF VCO, and to keep a constant PLL loop bandwidth. The recommend value is to set PLL\_ICP to 2.

#### 7.14.5 RF VCO

The very low phase-noise on-chip RF oscillator is based on an LC oscillator.

A capacitor bank is integrated to center the resonant frequency of the LC tank on the desired RF frequency. The VCO auto-calibration routine automatically trims the VCO to the correct sub-band. Whenever a different frequency setting is used for TX or RX operation, the VCO auto-calibration is carried out automatically. Automatic trimming can be blocked by setting bit SKIP\_VCO\_CAL in the LOCON register except during the PLL start-up; see <u>Section 8.2.1.3</u> "Local oscillator control register LOCON" on page 95. The trimming (sub-band selection) can be manually modified by control bits VCO\_SUBBAND[5:0] in register VCOCON; see <u>Section 8.2.1.2</u> "VCO control register <u>VCOCON" on page 94</u>. Frequency sub-band setting 0 corresponds to the maximum frequency, and 3Fh to the minimum frequency.

Note that this RF VCO is running at twice (868 MHz and 928 MHz bands) or four times (313 MHz and 434 MHz bands) the chosen frequency bands.

Setting bit VCO\_BAND selects the VCO's appropriate operating mode. This bit must be set to logic 1 at RF frequency bands below 400 MHz, or set to logic 0 for all other bands.

#### 7.14.6 PLL loop bandwidth setting

It is recommended that the PLL loop bandwidth is set to just above 150 kHz (-3 dB closed loop bandwidth) as this gives the best trade off between noise behavior and locking time. The loop bandwidth can be set by PLL\_ICP[4:0] to the recommended value ICP = 2.

#### 7.14.7 Delta-sigma modulator for fractional-N synthesis

The operating frequency is set by the content of frequency control registers FC0 to FC3, which each have a width of 20 bits. The 'active' frequency control register is selected directly by the TX or RX command; see <u>Section 8.2.1.1 "Frequency control registers" on page 93</u>.

**DL2381**

#### 7.14.7.1 PLL operating frequency f0

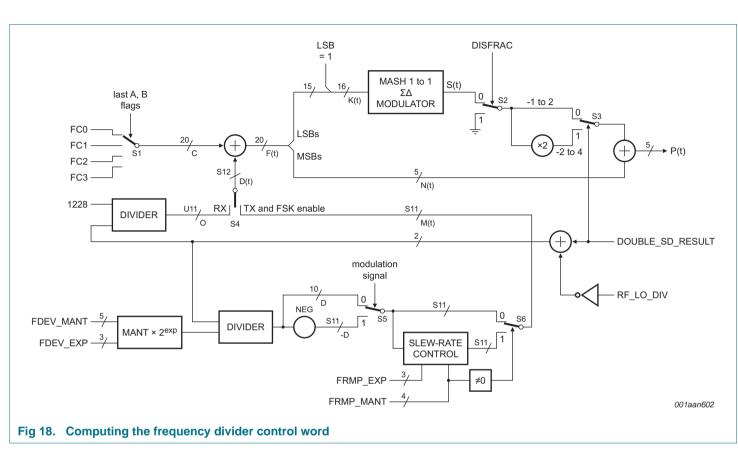

In Figure 18, the integer (Nt) is forwarded directly to the adder which produces the relevant control word (Pt) for the PLL. The remaining fractional values cannot be handled by the frequency divider directly and are therefore converted into a pseudo-random sequence of integers. This conversion is implemented by the sigma delta modulator. It produces numbers in the range from -1 to +2, whose average over time equals the given fractional part.

The spectral purity of the resulting RF signal is highly dependent on the randomness of the sequence generated by the fractional part. If this contained short repetitive patterns unwanted spurious signals may occur in the RF spectrum. To guarantee the produced sequences are always of maximal length, we append a constant 1-bit to the given fractional part, which resolves the issue. The weight of this 16th bit is 1/216 = 1/65536, which is very low. It creates a tiny frequency offset which can be taken into account when calculating the center frequency control value FCx for a given center frequency.

When the fractional part approaches 0 or 1 the low frequency noise components in the pseudo-random sequence become more dominant and can no longer be sufficiently suppressed by the PLL's transfer function. The visible effect is an increase of the phase noise in the RF output near the carrier. To counteract this effect, the OL2381 uses bit DOUBLE\_SD\_RESULT (Double Sigma Delta Result). If this bit is set, the fractional contribution to the PLL control word is doubled. So when the frequency control value F(t) is increased linearly, each RF output frequency is produced twice; once with a fractional value that is closer to zero or one (between 0 and 1 / 4 or between 3 / 4 and 1) and a second time with a fractional value which is closer to the mid-value 1 / 2 (between 1 / 4 and 3 / 4). The latter value produces a good pseudo-random sequence.

The frequency control value's fractional part is processed differently depending on bit DOUBLE\_SD\_RESULT, and the center frequency changes accordingly. Therefore the formulae, which convert between a given Frequency Control (FC) value and the RF center frequency, change with the state of bit DOUBLE\_SD\_RESULT.

In normal mode the expression is straightforward as shown in Equation 5.

$$f_{RF} = f_{ref} \times \left( 64 + 2 \times \frac{2 \times FCx + I}{65536} \right) \times \frac{1}{2 + 2 \times \text{RF}\_\text{LO}\_\text{DIV}}$$

(5)

- The expression's left side shows the reference frequency. The output frequency varies proportionally with the reference.

- The parenthesized expression (64 + 2 ×...) is the characteristics of the PLL frequency divider.

- The right term in the parenthesized expression accounts for the number interpretation of C and F(t) and the constant 1 LSB, which is added to guarantee maximum length sequences from the sigma-delta modulator

- The fraction at the right is the output division ratio, which is either 1 / 2 or 1 / 4, depending on the setting of bit RF\_LO\_DIV.

After simplifying the expression further we get the results shown in Equation 6.

$$f_{RF} = f_{ref} \times \left(32 + \frac{2 \times FCx + I}{65536}\right) \times \frac{1}{I + \text{RF}\_\text{LO}\_\text{DIV}}$$

(6)

For the inverse we solve the above expression for FCx and then we round the result to the nearest integer number as shown in Equation 7.

$$FCx = round\left\{ \begin{cases} f_{RF} \\ f_{ref} \end{cases} \times (1 + \text{RF}_{LO}_{DIV}) - 32 \end{cases} \times 32768 - 0.5 \end{cases}$$

(7)

Using the floor function this becomes as shown in Equation 8.

$$FCx = \left\lfloor \left\{ \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}\_\text{LO}\_\text{DIV}) - 32 \right\} \times 32768 \right\rfloor$$

(8)

**Remark:** Equation 8 is an important equation.

OL2381

If bit DOUBLE\_SD\_RESULT is set, the integer part and the fractional part of the center frequency setting must be considered separately. In this case the expression for the output frequency is shown in Equation 9.

$$f_{RF} = f_{ref} \times \left\{ 64 + 2 \times \left( FCx[19:15] + 2 \times \frac{2 \times FCx[14:0] + I}{65536} \right) \right\} \times \frac{I}{2 + 2 \times \text{RF}\_\text{LO}\_\text{DIV}}$$

(9)

In the inner parenthesized expression the integer part is taken as is, where the term which contains the fractional part has an additional factor of 2. After canceling certain factors of 2 we get result shown in Equation 10.

$$f_{RF} = f_{ref} \times \left\{ 32 + FCx[19:15] + \frac{2 \times FCx[14:0] + 1}{32768} \right\} \times \frac{1}{1 + \text{RF}\_\text{LO}\_\text{DIV}}$$

(10)

The inverse of this function is problematic, because the function for the output frequency is not monotonous. But we know that each output frequency is produced exactly twice and we know also that we want the solution where the average of the sigma-delta output S(t) is closest to 1 / 2. Let us convert Equation 10 such that the integer part of the frequency control value has no factor and the term containing the fractional part of the frequency control value becomes isolated on one side of the equation as shown in Equation 11.

$$\frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - FCx[19:15] = \frac{2 \times FCx[14:0] + 1}{32768} = 2 \times fract$$

(11)

Now we ask for the integer part for which the fractional part becomes a value in the range from 0.25 to 0.75, which is equivalent to twice the fractional part, and lies between 0.5 and 1.5 as shown in Equation 12 and Equation 13.

$$\frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - FCx[19:15] \ge 0.5$$

(12)

$$\frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - FCx[19:15] < 1.5$$

(13)

Now we can isolate the integer part from both inequalities so that the right sides are the same as shown in Equation 14 and Equation 15.

$$FCx[19:15] \le \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - 0.5$$

(14)

$$FCx[19:15]+1 > \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - 0.5$$

(15)

These inequalities can be combined into a single expression to calculate the integer control value for the PLL as shown in Equation 16.

$$FCx[19:15] = \left\lfloor \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32.5 \right\rfloor$$

(16)

**Remark:** Equation 16 is an important equation.

The integer part which we have just found can be entered in Equation 10 and then we can solve for the fractional part. We get the result for the settings after rounding it to the nearest integer number shown in Equation 17.

$$FCx[14:0] = round \left\{ \left\{ \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_LO_DIV) - 32 - FCx[19:15] \right\} \times 16384 - 0.5 \right\}$$

(17)

When using the floor function this becomes as shown in Equation 18.

$$FCx[14:0] = \left[ \begin{cases} f_{RF} \\ f_{ref} \end{cases} \times (1 + \text{RF}_{LO}_{DIV}) - 32 - FCx[19:15] \end{cases} \times 16384 \right]$$

(18)

**Remark:** Equation 18 is an important equation.

From Equation 5 and Equation 10 we can also see which frequency resolution can be achieved in which mode. If bit DOUBLE\_SD\_RESULT is set to logic 0, we have Equation 19.

$$f_{RF, res(0)} = f_{ref} \times 2 \times \frac{2}{65536} \times \frac{1}{2 + 2 \times \text{RF}_{\text{LO}_{\text{DIV}}}} = \frac{f_{ref}}{32768} \times \frac{1}{1 + \text{RF}_{\text{LO}_{\text{DIV}}}}$$

(19)

If bit DOUBLE\_SD\_RESULT is set to logic 1, the resolution becomes as shown in Equation 20.

$$f_{RF, res(1)} = f_{ref} \times 2 \times \frac{2}{65536} \times \frac{1}{2 + 2 \times \text{RF}_{\text{LO}_{\text{DIV}}}} = \frac{f_{ref}}{16384} \times \frac{1}{1 + \text{RF}_{\text{LO}_{\text{DIV}}}}$$

(20)

Taking bit DOUBLE\_SD\_RESULT into the formula, <u>Equation 19</u> and <u>Equation 20</u> can be combined into

$$f_{RF,res} = \frac{f_{ref}}{32768} \times \frac{1 + \text{DOUBLE}_SD_RESULT}{1 + \text{RF}_L\text{O}_D\text{IV}}$$

(21)

**Remark:** Equation 21 is an important equation.

#### 7.14.8 RX frequency offset

Because the OL2381 receiver implements a superheterodyne architecture with an intermediate frequency of 300 kHz, the local oscillator is automatically tuned to 300 kHz above the wanted RX center frequency in RX mode. This RX frequency offset is independent of the RF\_LO\_DIV and DOUBLE\_SD\_RESULT settings.

This is accomplished by adding an offset value O to the center frequency setting C; see Figure 18 "Computing the frequency divider control word" on page 31. This offset value is automatically adjusted so that it matches the LO frequency resolution, which changes with the settings of bits RF\_LO\_DIV and DOUBLE\_SD\_RESULT.

Table 70 "RX frequency offset" on page 107 shows that the resulting RX frequency offset is independent of the RF\_LO\_DIV and DOUBLE\_SD\_RESULT settings. It is always 195 Hz below the nominal IF of 300 kHz, which is accurate enough in all cases.

#### 7.14.9 PLL lock detection

A lock detection circuit is implemented to support the shortest PLL power-on time. The lock-detection circuit monitors the phase and frequency differences of the PLL and the reference clock. If the phase-difference of the two clock signals is settled within a defined window, an internal LOCK\_DETECT signal is triggered. After a specified time, set by bit LOCK\_DET\_TIME[1:0] in register EXPERT1, status bit LO\_RDY is set in register DEVSTATUS. Since the lock detect circuit consumes additional power, it is only enabled during the PLL's start-up phase and whenever a different sub-band setting is applied. The lock detect circuit can be manually controlled by bit LOCK\_DET\_ON in register LOCON; see Section 8.2.1.3 "Local oscillator control register LOCON" on page 95.

#### 7.15 VCO auto-calibration

VCO calibration is performed every time the VCO's center frequency is changed. The following internal sequences are started:

- 1. Start VCO calibration and turn on PLL lock detection. The output of the lock detection must be gated LOW when the calibration is running.

- 2. With the next clock cycle: turn on phase frequency detector (bit PFD\_ON), prescaler (bit PRESC\_ON), clock for PLL (bit CLK\_PLL\_ON) and PLL lock detection.

- Perform VCO calibration (select best possible sub-band for desired frequency setting).

- 4. Check PLL lock detection plus lock detect time.

#### 7.16 TX operation

#### 7.16.1 TX mode

#### 7.16.1.1 Preparation for TX mode

TX mode is initiated by setting the device mode bits DEV\_MODE[1:0] to 11b or by sending a TX command. The necessary VCO, PLL and PA start-up is accomplished by the internal state machine. Completion of the start-up sequence is indicated by bit TX\_RDY in the special function register DEVSTATUS.

#### 7.16.2 TX command

The power amplifier is activated on the first active edge of the TX command's ninth bit. Therefore, the active edge for the power amplifier start-up differs from the active edge of the remaining SPI communication. This must be considered for the data set-up time of the transmitted bit.

Predefined configurations can be chosen for the TX sequence. The configuration bits are described in Table 4.

| ТА               | ТВ          | TC                                               | TD                                   | TE                        | TF                      |

|------------------|-------------|--------------------------------------------------|--------------------------------------|---------------------------|-------------------------|

| TX frequency sel | ection bits | data and power<br>amplifier<br>synchronization b | power amplifier<br>control bit<br>it | Manchester generation bit | amplitude selection bit |

#### Table 4. TX command bits

#### **NXP Semiconductors**

# **OL2381**

#### Highly integrated single-chip sub 1 GHz RF transceiver

| Table 5. | TX command packet |    |    |    |    |    |    |  |

|----------|-------------------|----|----|----|----|----|----|--|

| D0       | D1                | D2 | D3 | D4 | D5 | D6 | D7 |  |

| 1        | 1                 | TA | ТВ | TC | TD | TE | TF |  |

#### Table 6. Control of TX data (bits TC, TE)[1]

| тс | TE | Effect                                                                                                                   |

|----|----|--------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | TX data is unsynchronized (only synchronized to CLK <sub>REF</sub> )                                                     |

| 1  | 0  | TX data is synchronized with the baud-rate clock ( $CLK_{TX}$ )                                                          |

| Х  | 1  | TX data is synchronized and XORed with the baud-rate clock (CLK $_{\text{TX}}$ ), hence Manchester generation is applied |

[1] If bit TE = 1, the value of bit TC is ignored and data is always synchronized with the baud-rate clock. However, bit TC has an effect if bit TD = 1. Therefore, bit TC must be properly set even if TE = 1.

#### Table 7. Power amplifier control and synchronization (bits TC, TD)

| тс | TD | Effect                                                                                                                                   |

|----|----|------------------------------------------------------------------------------------------------------------------------------------------|

| Х  | 0  | power amplifier stays on after falling edge of SEN                                                                                       |

| 0  | 1  | power amplifier turns off on the falling edge of SEN (PA off-ramping supported)                                                          |

| 1  | 1  | power amplifier turns off synchronously with the baud-rate clock ( $CLK_{TX}$ ) after the falling edge of SEN (PA off-ramping supported) |

#### Summary of combined TC, TD and TE bits Table 8.

| тс | TD | TE | Function                                                                                          |

|----|----|----|---------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | unsynchronized TX data and PA stays on                                                            |

| 0  | 0  | 1  | Manchester coded data and PA stays on                                                             |

| 0  | 1  | 0  | unsynchronized TX data and falling edge of SEN turns off PA                                       |

| 0  | 1  | 1  | Manchester coded data and falling edge of SEN turns off PA                                        |

| 1  | 0  | 0  | synchronized TX data and PA stays on.                                                             |

| 1  | 0  | 1  | Manchester coded data and PA stays on                                                             |

| 1  | 1  | 0  | Synchronized TX data and PA turns off synchronously $(CLK_{TX})$ after the falling edge of SEN    |

| 1  | 1  | 1  | Manchester coded data and PA turns off synchronously ( $CLK_{TX}$ ) after the falling edge of SEN |

| -  |    |    |                                                                                                   |

| Table 9. | Amplitude selection (bit TF)                                                    |

|----------|---------------------------------------------------------------------------------|

| Bit TF   | Effect                                                                          |

| 0        | modulation and amplitude/power settings are applied according to register ACON0 |

| 1        | modulation and amplitude/power settings are applied according to register ACON1 |

**Product data sheet**

| Table 10. | Frequency band selection (bit | s TA, TB)               |

|-----------|-------------------------------|-------------------------|

| Bit TA    | Bit TB                        | Selected frequency band |

| 0         | 0                             | FC0L, FC0M, FC0H        |

| 0         | 1                             | FC1L, FC1M, FC1H        |

| 1         | 0                             | FC2L, FC2M, FC2H        |

| 1         | 1                             | FC3L, FC3M, FC3H        |

OL2381 Product data sheet

37 of 152

### Highly integrated single-chip sub 1 GHz RF transceiver

# 7.16.3 Example of synchronized data transmission

### Table 11. Phase 1: data transmission

| D0 | D1 | D2                              | D3                       | D4                                                                                          | D5                                             | D6                                           | D7                                                                       |

|----|----|---------------------------------|--------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------|

| 1  | 1  | 0                               | 0                        | 1                                                                                           | 0                                              | 1                                            | 0                                                                        |

| -  | -  | selection of f<br>configuration | requency<br>register FC0 | synchronizat<br>ion of TX<br>data with<br>positive<br>edge of TX<br>clock CLK <sub>TX</sub> | after falling<br>edge of<br>SEN, TX<br>data is | Manchester code<br>generation is<br>selected | Modulation and<br>amplitude/power<br>settings of<br>ACON0 are<br>applied |

| Table 12. | Phase 2: end data transmission |    |                                      |                                                                                             |                                                                                                               |                                              |                                                                          |

|-----------|--------------------------------|----|--------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------|

| D0        | D1                             | D2 | D3                                   | D4                                                                                          | D5                                                                                                            | D6                                           | D7                                                                       |

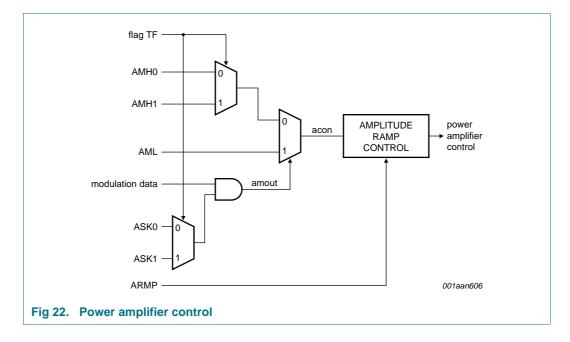

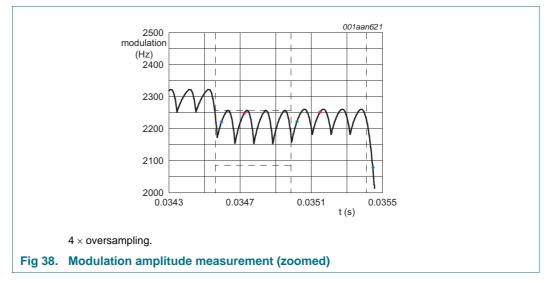

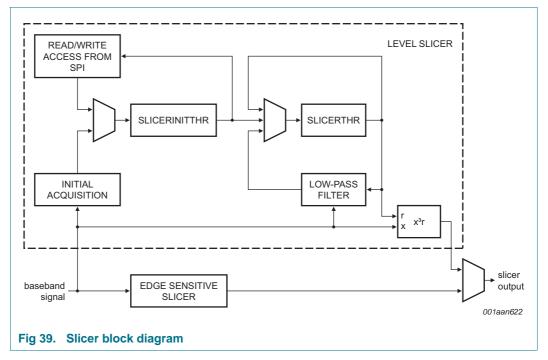

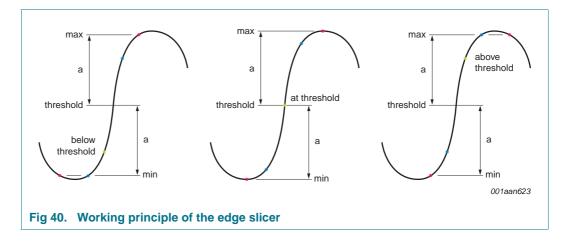

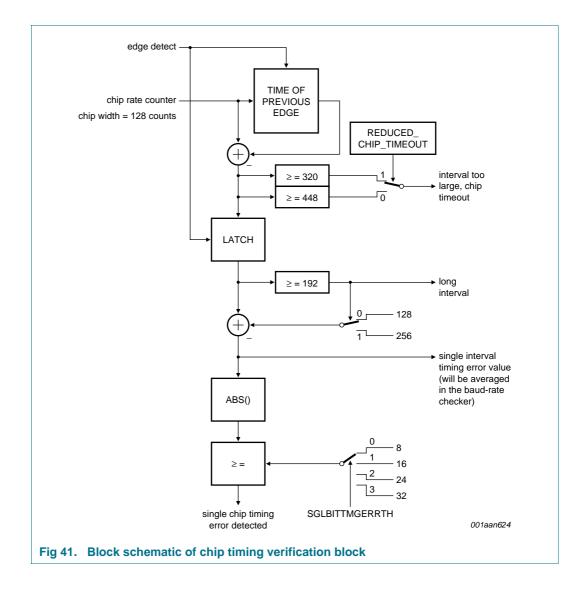

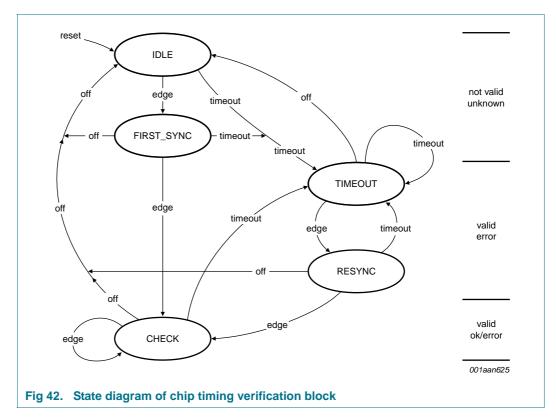

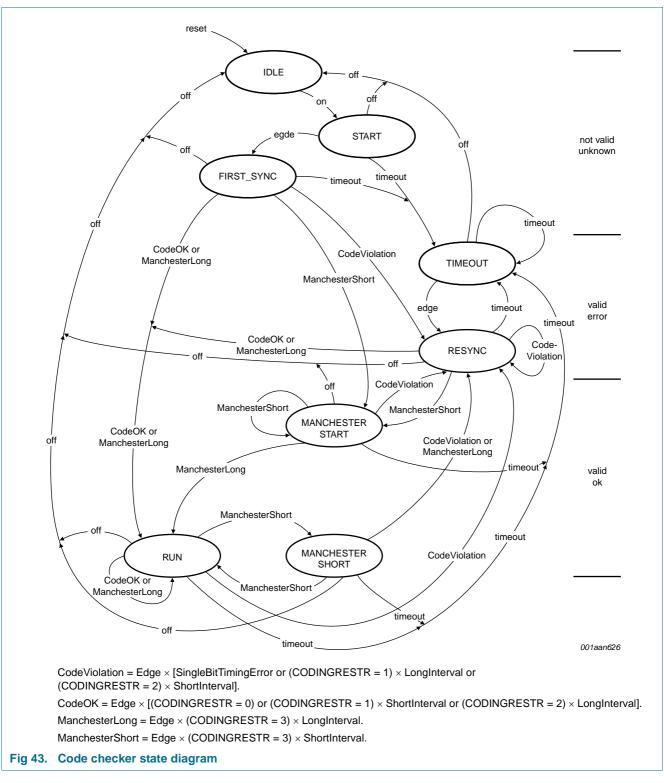

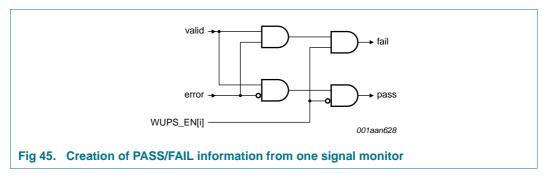

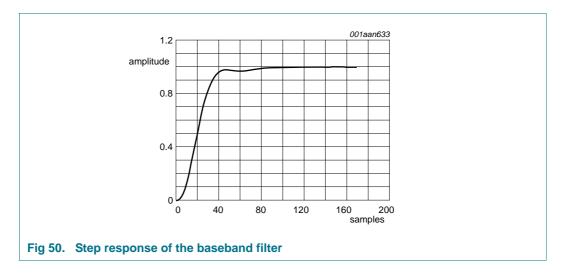

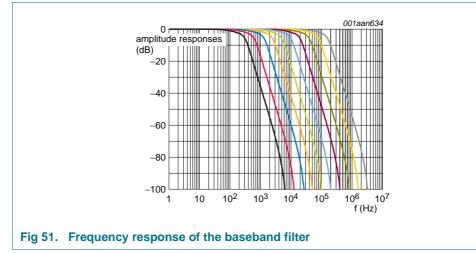

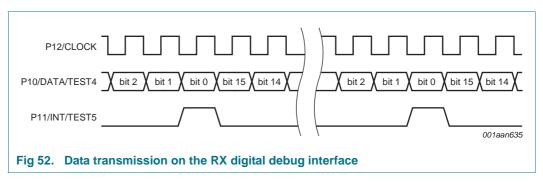

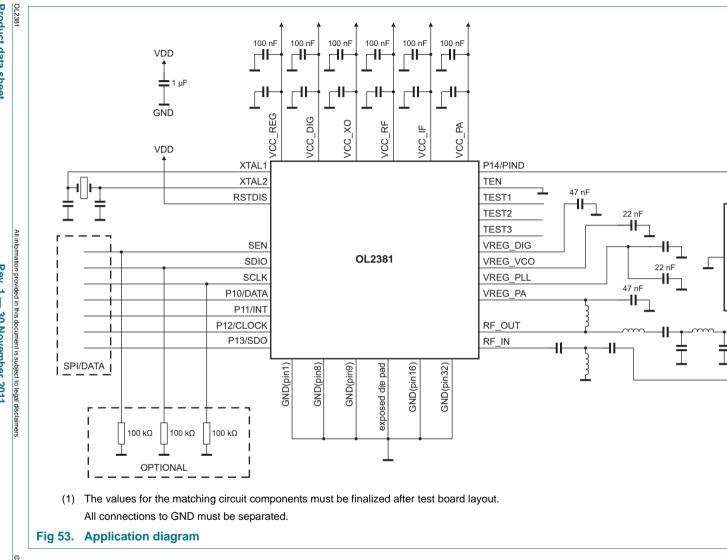

| 1         | 1                              | 0  | 0                                    | 1                                                                                           | 1                                                                                                             | 1                                            | 0                                                                        |