#### HD-6409

#### CMOS Manchester Encoder-Decoder

The HD-6409 Manchester Encoder-Decoder (MED) is a high speed, low power device manufactured using self-aligned silicon gate technology. The device is intended for use in serial data communication, and can be operated in either of two modes. In the converter mode, the MED converts Nonreturn-to-Zero code (NRZ) into Manchester code and decodes Manchester code into Nonreturn-to-Zero code. For serial data communication. Manchester code does not have some of the deficiencies inherent in Nonreturn-to-Zero code. For instance, use of the MED on a serial line eliminates DC components, provides clock recovery, and gives a relatively high degree of noise immunity. Because the MED converts the most commonly used code (NRZ) to Manchester code, the advantages of using Manchester code are easily realized in a serial data link.

In the Repeater mode, the MED accepts Manchester code input and reconstructs it with a recovered clock. This minimizes the effects of noise on a serial data link. A digital phase lock loop generates the recovered clock. A maximum data rate of 1MHz requires only 50mW of power.

Manchester code is used in magnetic tape recording and in fiber optic communication, and generally is used where data accuracy is imperative. Because it frames blocks of data, the HD-6409 easily interfaces to protocol controllers.

#### **Features**

- · Converter or Repeater Mode

- Independent Manchester encoder and decoder operation

- · Static to 1Mbps data rate ensured

- · Low bit error rate

- · Digital PLL clock recovery

- · On-chip oscillator

- · Low operating power: 50mW Typical at +5V

- Pb-Free (RoHS Compliant)

### **Related Literature**

For a full list of related documents, visit our website:

• HD-6409 device page

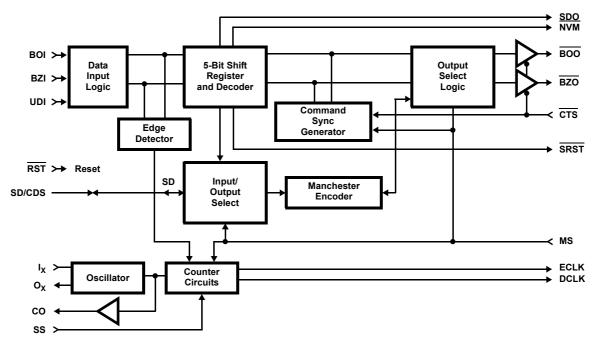

Figure 1. Block Diagram

HD-6409 1. Overview

### 1. Overview

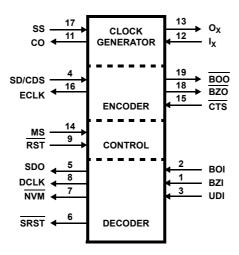

# 1.1 Logic Symbol

## 1.2 Ordering Information

| Part Number<br>(1Mbps) ( <u>Notes 2, 3</u> )   | Part Marking | Temp. Range<br>(°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant) | Pkg. Dwg. # |

|------------------------------------------------|--------------|---------------------|--------------------------------------------|-----------------------------|-------------|

| HD3-6409-9Z (No longer available or supported) | HD3-6409-9Z  | -40 to +85          | -                                          | 20 Ld PDIP                  | E20.3       |

| HD9P6409-9Z                                    | HD9P6409-9Z  | -40 to +85          | -                                          | 20 Ld SOIC                  | M20.3       |

| HD9P6409-9Z96                                  | HD9P6409-9Z  | -40 to +85          | 1k                                         | 20 Ld SOIC                  | M20.3       |

#### Notes:

- 1. See TB347 for details on reel specifications.

- These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations).

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC

J-STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the <u>HD-6409</u> device page. For more information about MSL, see <u>TB363</u>.

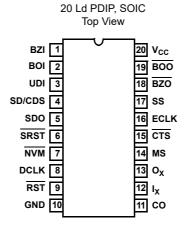

## 1.3 Pin Configuration

HD-6409 1. Overview

# 1.4 Pin Descriptions

| Pin<br>Number | Туре | Symbol         | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|------|----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | I    | BZI            | Bipolar Zero Input                  | Used in conjunction with Pin 2, Bipolar One Input (BOI), to input Manchester II encoded data to the decoder, BZI and BOI are logical complements. When using Pin 3, Unipolar Data Input (UDI) for data input, BZI must be held high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2             | I    | BOI            | Bipolar One Input                   | Used in conjunction with Pin 1, Bipolar Zero Input (BZI), to input Manchester II encoded data to the decoder, BOI and BZI are logical complements. When using Pin 3, Unipolar Data Input (UDI) for data input, BOI must be held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3             | I    | UDI            | Unipolar Data Input                 | An alternate to bipolar input (BZI, BOI), Unipolar Data Input (UDI) inputs Manchester II encoded data to the decoder. When using Pin 1 (BZI) and Pin 2 (BOI) for data input, UDI must be held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

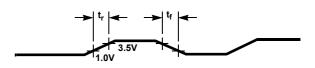

| 4             | I/O  | SD/CDS         | Serial<br>Data/Command Data<br>Sync | In the converter mode, SD/CDS is an input that receives serial NRZ data. NRZ data is accepted synchronously on the falling edge of encoder clock output (ECLK). In the repeater mode, SD/CDS is an output indicating the status of last valid sync pattern received. A high indicates a command sync and a low indicates a data sync pattern.                                                                                                                                                                                                                                                                                                                                                                                               |

| 5             | 0    | SDO            | Serial Data Out                     | The decoded serial NRZ data is transmitted out synchronously with the decoder clock (DCLK). SDO is forced low when $\overline{RST}$ is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6             | 0    | SRST           | Serial Reset                        | In the converter mode, SRST follows RST. In the repeater mode, when RST goes low, SRST goes low and remains low after RST goes high. SRST goes high only when RST is high, the reset bit is zero, and a valid synchronization sequence is received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7             | 0    | NVM            | Nonvalid Manchester                 | A low on NVM indicates that the decoder has received invalid Manchester data and present data on Serial Data Out (SDO) is invalid. A high indicates that the sync pulse and data were valid and SDO is valid. NVM is set low by a low on RST, and remains low after RST goes high until valid sync pulse followed by two valid Manchester bits is received.                                                                                                                                                                                                                                                                                                                                                                                 |

| 8             | 0    | DCLK           | Decoder Clock                       | The decoder clock is a 1X clock recovered from BZI and BOI, or UDI to synchronously output received NRZ data (SDO).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9             | I    | RST            | Reset                               | In the converter mode, a low on $\overline{RST}$ forces SDO, DCLK, $\overline{NVM}$ , and $\overline{SRST}$ low. A high on $\overline{RST}$ enables SDO and DCLK, and forces $\overline{SRST}$ high. $\overline{NVM}$ remains low after $\overline{RST}$ goes high until a valid sync pulse followed by two Manchester bits is received, after which it goes high. In the repeater mode, $\overline{RST}$ has the same effect on SDO, DCLK, and $\overline{NVM}$ as in the converter mode. When $\overline{RST}$ goes $\overline{ISMST}$ goes low and remains low after $\overline{RST}$ goes high. $\overline{SRST}$ goes high only when $\overline{RST}$ is high, the reset bit is zero and a valid synchronization sequence is received. |

| 10            | I    | GND            | Ground                              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11            | 0    | Co             | Clock Output                        | Buffered output of clock input I <sub>X</sub> . Can be used as a clock signal for other peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12            | I    | I <sub>X</sub> | Clock Input                         | $I_X$ is the input for an external clock or, if the internal oscillator is used, $I_X$ and $O_X$ are used for the connection of the crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13            | 0    | O <sub>X</sub> | Clock Drive                         | If the internal oscillator is used, $O_X$ and $I_X$ are used for the connection of the crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14            | I    | MS             | Mode Select                         | MS must be held low for operation in the converter mode, and high for operation in the repeater mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15            | I    | CTS            | Clear to Send                       | In the converter mode, a high disables the encoder, forcing outputs $\overline{BOO}$ , $\overline{BZO}$ high and ECLK low. A high to low transition of $\overline{CTS}$ initiates transmission of a Command sync pulse. A low on $\overline{CTS}$ enables $\overline{BOO}$ , $\overline{BZO}$ , and ECLK. In the repeater mode, the function of $\overline{CTS}$ is identical to that of the converter mode with the exception that a transition of $\overline{CTS}$ does not initiate a synchronization sequence.                                                                                                                                                                                                                          |

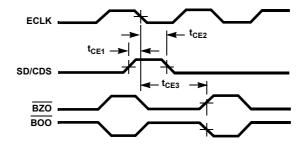

| 16            | 0    | ECLK           | Encoder Clock                       | In the converter mode, ECLK is a 1X clock output that receives serial NRZ data to SD/CDS. In the repeater mode, ECLK is a 2X clock which is recovered from BZI and BOI data by the digital phase locked loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17            | I    | SS             | Speed Select                        | A logic high on SS sets the data rate at 1/32 times the clock frequency while a low sets the data rate at 1/16 times the clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

HD-6409 1. Overview

| Pin<br>Number | Туре | Symbol          | Name                | Description                                                                                                               |

|---------------|------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|

| 18            | 0    | BZO             | Bipolar Zero Output | BZO and its logical complement BOO are the Manchester data outputs of the encoder.                                        |

| 19            | 0    | BOO             | Bipolar One Out     | The inactive state for these outputs is in the high state.                                                                |

| 20            | I    | V <sub>CC</sub> | V <sub>CC</sub>     | $V_{CC}$ is the +5V power supply pin. A 0.1µF decoupling capacitor from $V_{CC}$ (Pin 20) to GND (Pin 10) is recommended. |

Note: (I) Input(O) Output

# 2. Specifications

# 2.1 Absolute Maximum Ratings

| Parameter                    | Minimum   | Maximum   | Unit |

|------------------------------|-----------|-----------|------|

| Supply Voltage               |           | +7.0      | V    |

| Input, Output or I/O Voltage | GND - 0.5 | VCC + 0.5 | V    |

| ESD Classification           | Class 1   |           |      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

### 2.2 Thermal Information

| Thermal Resistance (Typical, Note 4) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |  |

|--------------------------------------|------------------------|------------------------|--|

| PDIP Package                         | 75                     | N/A                    |  |

| SOIC Package                         | 100                    | N/A                    |  |

#### Notes:

4.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u>.

| Parameter                       | Minimum          | Maximum | Unit |  |

|---------------------------------|------------------|---------|------|--|

| Storage Temperature Range       | -65              | +150    | °C   |  |

| Maximum Junction Temperature    |                  |         |      |  |

| Ceramic Package                 |                  | +175    | °C   |  |

| Plastic Package                 |                  | +150    | °C   |  |

| Pb-Free Reflow Profile (Note 5) | see <u>TB493</u> |         |      |  |

#### Note:

# 2.3 Operating Conditions

| Parameter                                    | Minimum | Maximum                            | Unit |

|----------------------------------------------|---------|------------------------------------|------|

| Operating Temperature Range                  | -40     | +85                                | °C   |

| Operating Voltage Range                      | +4.5    | +5.5                               | V    |

| Input Rise and Fall Times                    |         | 50                                 | ns   |

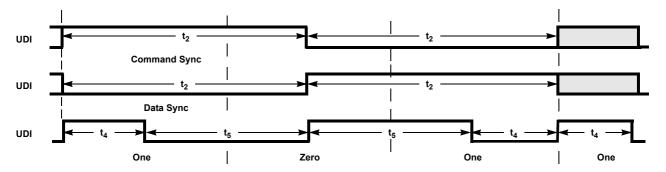

| Sync. Transition Span (t <sub>2</sub> )      |         | 1.5 Typical, ( <u>Notes 6, 7</u> ) | DBP  |

| Short Data Transition Span (t <sub>4</sub> ) |         | 0.5 Typical, ( <u>Notes 6, 7</u> ) | DBP  |

| Long Data Transition Span (t <sub>5</sub> )  |         | 1.0 Typical, ( <u>Notes 6, 7</u> ) | DBP  |

| Zero Crossing Tolerance (t <sub>CD5</sub> )  |         | ( <u>Note 8</u> )                  |      |

#### Notes:

- 6. DBP-Data Bit Period, Clock Rate = 16X, one DBP = 16 Clock Cycles; Clock Rate = 32X, one DBP = 32 Clock Cycles.

- The input conditions specified are nominal values, the actual input waveforms transition spans may vary by ±2 I<sub>X</sub> clock cycles (16X mode) or ±6 I<sub>X</sub> clock cycles (32X mode).

- 8. The maximum zero crossing tolerance is ±2 I<sub>X</sub> clock cycles (16X mode) or ±6 I<sub>X</sub> clock cycles (32 mode) from the nominal.

### 2.4 Die Characteristics

| Parameter   | Value |

|-------------|-------|

| Gate Counts | 250   |

<sup>5.</sup> Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

# 2.5 DC Electrical Specifications

$V_{CC}$  = 5.0V ± 10%,  $T_A$  = -40°C to +85°C

| Parameter                                        | Symbol            | Test Conditions (Note 9)                                                                               | Min<br>( <u>Note 11</u> ) | Max<br>( <u>Note 11</u> ) | Unit |

|--------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------|

| Logical "1" Input Voltage                        | V <sub>IH</sub>   | V <sub>CC</sub> = 4.5V                                                                                 | 70% V <sub>CC</sub>       | -                         | ٧    |

| Logical "0" Input Voltage                        | V <sub>IL</sub>   | V <sub>CC</sub> = 4.5V                                                                                 | -                         | 20% V <sub>CC</sub>       | V    |

| Logic "1" Input Voltage (Reset)                  | V <sub>IHR</sub>  | V <sub>CC</sub> = 5.5V                                                                                 | V <sub>CC</sub> -0.5      | -                         | ٧    |

| Logic "0" Input Voltage (Reset)                  | $V_{ILR}$         | V <sub>CC</sub> = 4.5V                                                                                 | -                         | GND +0.5                  | V    |

| Logical "1" Input Voltage (Clock)                | V <sub>IHC</sub>  | V <sub>CC</sub> = 5.5V                                                                                 | V <sub>CC</sub> -0.5      | -                         | ٧    |

| Logical "0" Input Voltage (Clock)                | V <sub>ILC</sub>  | V <sub>CC</sub> = 4.5V                                                                                 | -                         | GND +0.5                  | ٧    |

| Input Leakage Current (Except I <sub>X</sub> )   | I <sub>I</sub>    | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.5V                                       | -1.0                      | +1.0                      | μΑ   |

| Input Leakage Current (I <sub>X</sub> )          | I <sub>I</sub>    | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.5V                                       | -20                       | +20                       | μA   |

| I/O Leakage Current                              | I <sub>O</sub>    | V <sub>OUT</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.5V                                      | -10                       | +10                       | μΑ   |

| Output HIGH Voltage (All Except O <sub>X</sub> ) | V <sub>OH</sub>   | I <sub>OH</sub> = -2.0mA, V <sub>CC</sub> = 4.5V ( <u>Note 10</u> )                                    | V <sub>CC</sub> -0.4      | -                         | V    |

| Output LOW Voltage (All Except O <sub>X</sub> )  | V <sub>OL</sub>   | I <sub>OL</sub> = +2.0mA, V <sub>CC</sub> = 4.5V ( <u>Note 10</u> )                                    | -                         | 0.4                       | ٧    |

| Standby Power Supply Current                     | I <sub>CCSB</sub> | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.5V,<br>Outputs Open                      | -                         | 100                       | μΑ   |

| Operating Power Supply Current                   | I <sub>CCOP</sub> | f = 16.0MHz, V <sub>IN</sub> = V <sub>CC</sub> or GND<br>V <sub>CC</sub> = 5.5V, C <sub>L</sub> = 50pF | -                         | 18.0                      | mA   |

| Functional Test                                  | F <sub>T</sub>    | ( <u>Note 9</u> )                                                                                      | -                         | -                         | -    |

#### Notes:

- 9. Tested as follows: f = 16MHz,  $V_{IH}$  = 70%  $V_{CC}$ ,  $V_{IL}$  = 20%  $V_{CC}$ ,  $V_{OH} \ge V_{CC}/2$ , and  $V_{OL} \le V_{CC}/2$ ,  $V_{CC}$  = 4.5V and 5.5V.

- 10. Interchanging of force and sense conditions is permitted.

- 11. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

## 2.6 Capacitance

$T_A = +25$ °C, Frequency = 1MHz.

| Parameter          | Symbol           | Test Conditions                               | Тур | Unit |

|--------------------|------------------|-----------------------------------------------|-----|------|

| Input Capacitance  | C <sub>IN</sub>  | All measurements are referenced to device GND | 10  | pF   |

| Output Capacitance | C <sub>OUT</sub> |                                               | 12  | pF   |

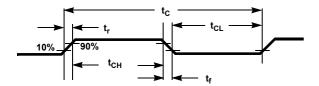

# 2.7 AC Electrical Specifications

$V_{CC}$  = 5.0V ±10%,  $T_A$  = -40°C to +85°C

| Parameter              | Symbol           | Test Conditions<br>(Note 12) | Min<br>( <u>Note 11</u> ) | Max<br>( <u>Note 11</u> ) | Unit |

|------------------------|------------------|------------------------------|---------------------------|---------------------------|------|

| Clock Frequency        | f <sub>C</sub>   |                              | -                         | 16                        | MHz  |

| Clock Period           | t <sub>C</sub>   |                              | 1/f <sub>C</sub>          | -                         | sec  |

| Bipolar Pulse Width    | t <sub>1</sub>   |                              | t <sub>C</sub> +10        | -                         | ns   |

| One-Zero Overlap       | t <sub>3</sub>   |                              | -                         | t <sub>C</sub> -10        | ns   |

| Clock High Time        | t <sub>CH</sub>  | f = 16.0MHz                  | 20                        | -                         | ns   |

| Clock Low Time         | t <sub>CL</sub>  | f = 16.0MHz                  | 20                        | -                         | ns   |

| Serial Data Setup Time | t <sub>CE1</sub> |                              | 120                       | -                         | ns   |

| Serial Data Hold Time  | t <sub>CE2</sub> |                              | 0                         | -                         | ns   |

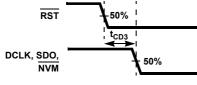

| DCLK to SDO, NVM       | t <sub>CD2</sub> |                              | -                         | 40                        | ns   |

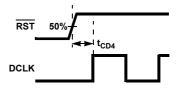

| ECLK to BZO            | t <sub>R2</sub>  |                              | -                         | 40                        | ns   |

### $V_{CC}$ = 5.0V ±10%, $T_A$ = -40°C to +85°C (Continued)

| Parameter                           | Symbol           | Test Conditions<br>( <u>Note 12</u> )             | Min<br>( <u>Note 11</u> ) | Max<br>( <u>Note 11</u> ) | Unit |

|-------------------------------------|------------------|---------------------------------------------------|---------------------------|---------------------------|------|

| Output Rise Time (All except Clock) | t <sub>r</sub>   | From 1.0V to 3.5V, C <sub>L</sub> = 50pF, Note 13 | -                         | 50                        | ns   |

| Output Fall Time (All except Clock) | t <sub>f</sub>   | From 3.5V to 1.0V, C <sub>L</sub> = 50pF, Note 13 | -                         | 50                        | ns   |

| Clock Output Rise Time              | t <sub>r</sub>   | From 1.0V to 3.5V, C <sub>L</sub> = 20pF, Note 13 | -                         | 11                        | ns   |

| Clock Output Fall Time              | t <sub>f</sub>   | From 3.5V to 1.0V, C <sub>L</sub> = 20pF, Note 13 | -                         | 11                        | ns   |

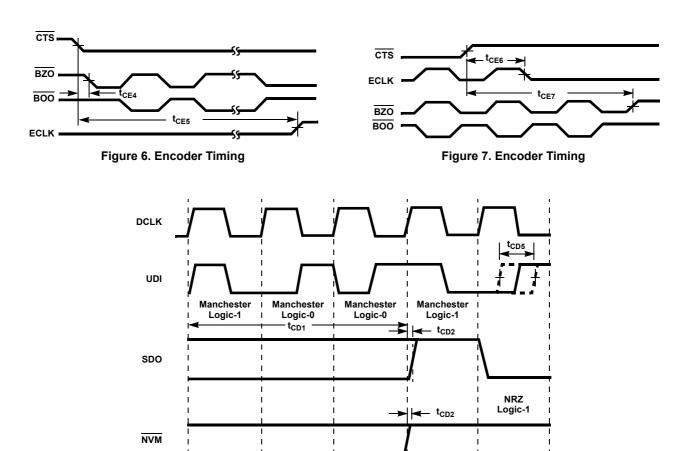

| ECLK to BZO, BOO                    | t <sub>CE3</sub> | Notes 13, 14                                      | 0.5                       | 1.0                       | DBP  |

| CTS Low to BZO, BOO Enabled         | t <sub>CE4</sub> | Notes 13, 14                                      | 0.5                       | 1.5                       | DBP  |

| CTS Low to ECLK Enabled             | t <sub>CE5</sub> | Notes 13, 14                                      | 10.5                      | 11.5                      | DBP  |

| CTS High to ECLK Disabled           | t <sub>CE6</sub> | Notes 13, 14                                      | -                         | 1.0                       | DBP  |

| CTS High to BZO, BOO Disabled       | t <sub>CE7</sub> | Notes 13, 14                                      | 1.5                       | 2.5                       | DBP  |

| UDI to SDO, NVM                     | t <sub>CD1</sub> | Notes 13, 14                                      | 2.5                       | 3.0                       | DBP  |

| RST Low to CDLK, SDO, NVM Low       | t <sub>CD3</sub> | Notes 13, 14                                      | 0.5                       | 1.5                       | DBP  |

| RST High to DCLK, Enabled           | t <sub>CD4</sub> | Notes 13, 14                                      | 0.5                       | 1.5                       | DBP  |

| UDI to BZO, BOO                     | t <sub>R1</sub>  | Notes 13, 14                                      | 0.5                       | 1.0                       | DBP  |

| UDI to SDO, NVM                     | t <sub>R3</sub>  | Notes 13, 14                                      | 2.5                       | 3.0                       | DBP  |

#### Notes:

<sup>12.</sup> AC testing as follows: f = 4.0MHz, V<sub>IH</sub> = 70% V<sub>CC</sub>, V<sub>IL</sub> = 20% V<sub>CC</sub>, Speed Select = 16X, V<sub>OH</sub> ≥ V<sub>CC</sub>/2, V<sub>OL</sub> ≤ V<sub>CC</sub>/2, V<sub>CC</sub> = 4.5V and 5.5V. Input rise and fall times driven at 1ns/V, Output load = 50pF.

<sup>13.</sup> Limits established by characterization and are not production tested.

<sup>14.</sup> DBP-Data Bit Period, Clock Rate = 16X, one DBP = 16 Clock Cycles; Clock Rate = 32X, one DBP = 32 Clock Cycles.

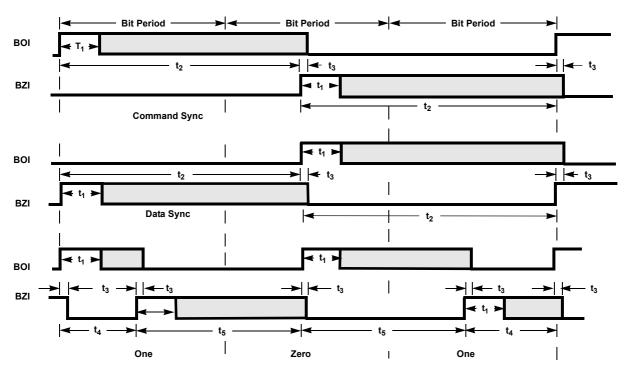

# 2.8 Timing Waveforms

Note: UDI = 0, For Next Diagrams

Note: BOI = 0, BZI = 1 For Next Diagrams

Figure 2.

Figure 3. Clock Timing

Figure 4. Output Waveform

Figure 5. Encoder Timing

Note: Manchester Data-In is not synchronous with Decoder Clock.

Decoder Clock is synchronous with decoded NRZ out of SDO.

15

Figure 8. Decoder Timing

Figure 9. Decoder Timing

Figure 10. Decoder Timing

Figure 11. Repeater Timing

# 2.9 Test Load Circuit

Note: Includes Stray and Jig Capacitance

Figure 12. Test Load Circuit

# 3. Functional Descriptions

### 3.1 Encoder Operation

The encoder uses free running clocks at 1X and 2X the data rate derived from the system clock  $I_X$  for internal timing.  $\overline{CTS}$  controls the encoder outputs, ECLK,  $\overline{BOO}$ , and  $\overline{BZO}$ . A free running 1X ECLK is transmitted out of the encoder to drive the external circuits which supply the NRZ data to the MED at pin SD/CDS.

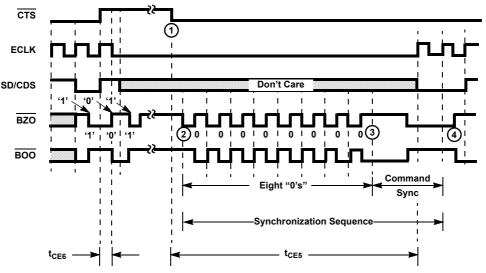

A low on CTS enables encoder outputs ECLK, BOO, and BZO, while a high on CTS forces BZO, BOO high and holds ECLK low. When CTS goes from high to low ①, a synchronization sequence is transmitted out on BOO and BZO. A synchronization sequence consists of eight Manchester "0" bits followed by a command sync pulse. ② A command sync pulse is a 3-bit wide pulse with the first 1 1/2 bits high followed by 1 1/2 bits low. ③ Serial NRZ data is clocked into the encoder at SD/CDS on the high to low transition of ECLK during the command sync pulse. The NRZ data received is encoded into Manchester II data and transmitted out on BOO and BZO following the command sync pulse. ④ Following the synchronization sequence, input data is encoded and transmitted out continuously without parity check or word framing. The length of the data block encoded is defined by CTS. Manchester data out is inverted.

Figure 13. Encoder Operation

### 3.2 Decoder Operation

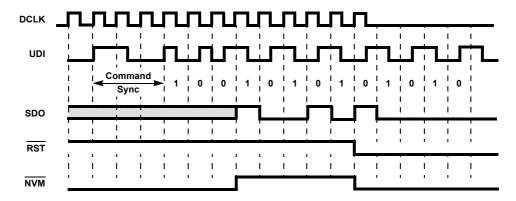

The decoder requires a single clock with a frequency 16X or 32X the desired data rate. The rate is selected on the speed select with SS low producing a 16X clock and high a 32X clock. For long data links the 32X mode should be used as this permits a wider timing jitter margin. The internal operation of the decoder utilizes a free running clock synchronized with incoming data for its clocking.

The Manchester II encoded data can be presented to the decoder in either of two ways. The Bipolar One and Bipolar Zero inputs accept data from differential inputs such as a comparator sensed transfo<u>rmer coupled bus</u>. The Unipolar Data input can only accept noninverted Manchester II encoded data, such as Bipolar One Out through an inverter to Unipolar Data Input. The decoder continuously monitors this data input for valid sync pattern. Note that while the MED encoder section can generate only a command sync pattern, the decoder can recognize either a command or data sync pattern. A data sync is a logically inverted command sync.

There is a 3-bit delay between UDI, BOI, or BZI input and the decoded NRZ data transmitted out of SDO.

Control of the decoder outputs is provided by the  $\overline{RST}$  pin. When  $\overline{RST}$  is low, SDO, DCLK, and  $\overline{NVM}$  are forced low. When  $\overline{RST}$  is high, SDO is transmitted out synchronously with the recovered clock DCLK. The  $\overline{NVM}$  output remains low after a low-to-high transition on  $\overline{RST}$  until a valid sync pattern is received.

The decoded data at SDO is in NRZ format. DCLK is provided so that the decoded bits can be shifted into an external register on every high-to-low transition of this clock. Three bit periods after an invalid Manchester bit is

received on UDI, or BOI, NVM goes low synchronously with the questionable data output on SDO. Note: The decoder does not re-establish proper data decoding until another sync pattern is recognized.

Figure 14. Decoder Operation

## 3.3 Repeater Operation

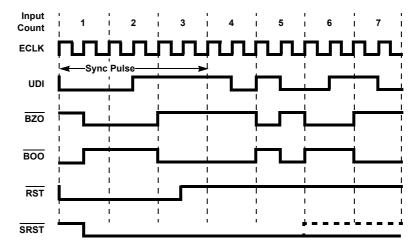

Manchester II data can be presented to the repeater in either of two ways. The inputs Bipolar One In and Bipolar Zero In accept data from differential inputs such as a comparator or sensed transformer coupled bus. The input Unipolar Data In accepts only noninverted Manchester II coded data. The decoder requires a single clock with a frequency 16X or 32X the desired data rate. This clock is selected to 16X with Speed Select low and 32X with Speed Select high. For long data links the 32X mode should be used as this permits a wider timing jitter margin.

The inputs UDI, or BOI, BZI are delayed approximately 1/2 bit period and repeated as outputs  $\overline{BOO}$  and  $\overline{BZO}$ . The 2X ECLK is transmitted out of the repeater synchronously with  $\overline{BOO}$  and  $\overline{BZO}$ .

A low on  $\overline{\text{CTS}}$  enables ECLK,  $\overline{\text{BOO}}$ , and  $\overline{\text{BZO}}$ . In contrast to the converter mode, a transition on CTS does not initiate a synchronization sequence of eight 0's and a command sync. The repeater mode does recognize a command or data sync pulse. SD/CDS is an output which reflects the state of the most recent sync pulse received, with high indicating a command sync and low indicating a data sync.

When RST is low, the outputs SDO, DCLK, and NVM are low, and SRST is set low. SRST remains low after RST goes high and is not reset until a sync pulse and two valid manchester bits are received with the reset bit low. The reset bit is the first data bit after the sync pulse. With RST high, NRZ Data is transmitted out of Serial Data Out synchronously with the 1X DCLK.

Figure 15. Repeater Operation

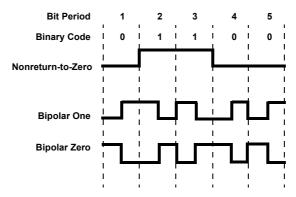

#### 3.4 Manchester Code

Nonreturn-to-Zero (NRZ) code represents the binary values logic-0 and logic-1 with a static level maintained throughout the data cell. In contrast, Manchester code represents data with a level transition in the middle of the data cell. Manchester has bandwidth, error detection, and synchronization advantages over NRZ code.

The Manchester II code Bipolar One and Bipolar Zero shown below are logical complements. The direction of the transition indicates the binary value of data. A logic-0 in Bipolar One is defined as a low-to-high transition in the middle of the data cell, and a logic-1 as a high-to-low mid bit transition, Manchester II is also known as Biphase-L code.

The bandwidth of NRZ is from DC to the clock frequency fc/2, while that of Manchester is from fc/2 to fc. Thus, Manchester can be AC or transformer coupled, which has considerable advantages over DC coupling. Also, the ratio of maximum to minimum frequency of Manchester extends one octave, while the ratio for NRZ is the range of 5 to 10 octaves. It is much easier to design a narrow band than a wideband amp.

Secondly, the mid bit transition in each data cell provides the code with an effective error detection scheme. If noise produces a logic inversion in the data cell such that there is no transition, an error indiction is given, and synchronization must be re-established. This places relatively stringent requirements on the incoming data.

The synchronization advantages of using the HD-6409 and Manchester code are several fold. One is that Manchester is a self clocking code. The clock in serial data communication defines the position of each data cell. Non self clocking codes, as NRZ, often require an extra clock wire or clock track (in magnetic recording). Further, there can be a phase variation between the clock and data track. Crosstalk between the two may be a problem. In Manchester, the serial data stream contains both the clock and the data, with the position of the mid bit transition representing the clock, and the direction of the transition representing data. There is no phase variation between the clock and the data.

A second synchronization advantage is a result of the number of transitions in the data. The decoder resynchronizes on each transition, or at least once every data cell. In contrast, receivers using NRZ, which does not necessarily have transitions, must resynchronize on frame bit transitions, which occur far less often, usually on a character basis. This more frequent resynchronization eliminates the cumulative effect of errors over successive data cells. A final synchronization advantage concerns the HD-6409's sync pulse that initiates synchronization. This 3-bit wide pattern is sufficiently distinct from Manchester data that a false start by the receiver is unlikely.

Figure 16. Manchester Code

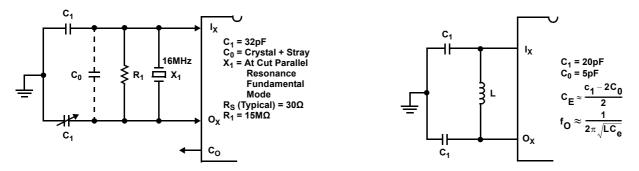

# 3.5 Crystal Oscillator and LC Oscillator Modes

Figure 17. Crystal Oscillator Mode

Figure 18. LC Oscillator Mode

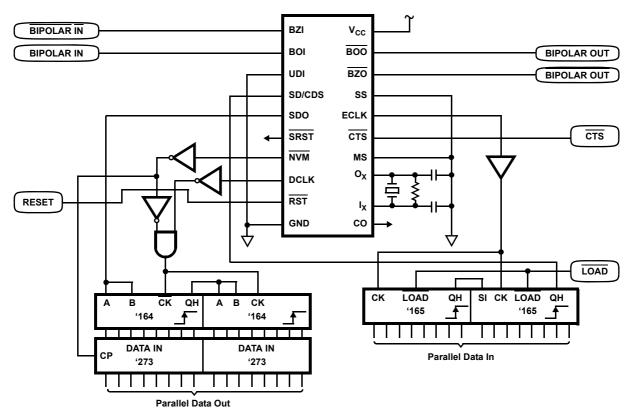

# 3.6 Using the 6409 as a Manchester Encoded UART

Figure 19. Manchester Encoder UART

HD-6409 4. Revision History

# 4. Revision History

| Rev. | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5.00 | Jul.8.19 | Applied new formatting throughout. Updated links throughout. Added Related Literature. Updated Ordering Information table by adding tape and reel information, removing HD3-6409-9, and updating Notes 1 and 3. Removed About Intersil section. Updated Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 4.00 | Oct.1.15 | Added Rev History beginning with Rev 4.  Added About Intersil Verbiage.  Updated Ordering Information on page 1  Updated POD M20.3 to most current version. Revision changes are as follows:  Top View:  Corrected "7.50 BSC" to "7.60/7.40" (no change from rev 2; error was introduced in conversion)  Changed "10.30 BSC" to "10.65/10.00" (no change from rev 2; error was introduced in conversion)  Side View:  Changed "12.80 BSC" to "13.00/12.60" (no change from rev 2; error was introduced in conversion)  Changed "2.65 max" to "2.65/2.35" (no change from rev 2; error was introduced in conversion)  Changed Note 1 from "ANSI Y14.5M-1982." to "ASME Y14.5M-1994"  Updated to new POD format by moving dimensions from table onto drawing and adding land pattern |  |  |  |  |

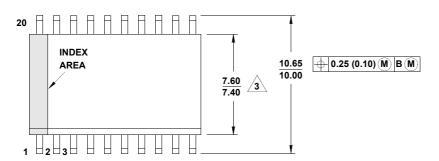

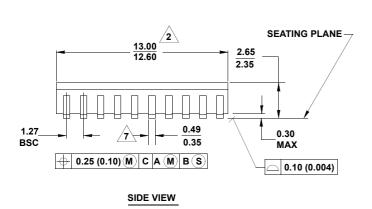

# 5. Package Outline Drawings

For the most recent package outline drawing, see M20.3.

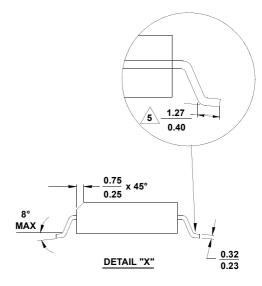

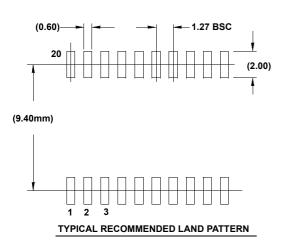

M20.3 20 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE (SOIC) Rev 3, 2/11

TOP VIEW

#### NOTES:

- 1. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 2. Dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 3. Dimension does not include interlead lash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- **5.** Dimension is the length of terminal for soldering to a substrate.

- 6. Terminal numbers are shown for reference only.

- 7. The lead width as measured 0.36mm (0.14 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 8. Controlling dimension: MILLIMETER.

- 9. Dimensions in ( ) for reference only.

- 10. JEDEC reference drawing number: MS-013-AC.

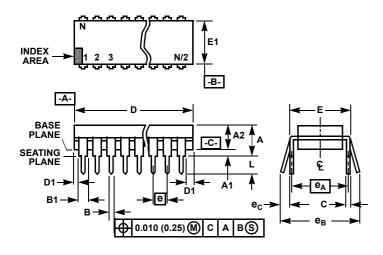

For the most recent package outline drawing, see <u>E20.3</u>.

#### Notes:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and  $\boxed{e_A}$  are measured with the leads constrained to be perpendicular to datum  $\boxed{-C_-}$ .

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained. e<sub>C</sub> must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

# E20.3 (JEDEC MS-001-AD ISSUE D) 20 Lead Dual-In-Line Plastic Package (PDIP)

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α              | -         | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.115     | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045     | 0.070 | 1.55        | 1.77  | 8     |

| С              | 0.008     | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.980     | 1.060 | 24.89       | 26.9  | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| E              | 0.300     | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240     | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100     | BSC   | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.300 BSC |       | 7.62 BSC    |       | 6     |

| e <sub>B</sub> | -         | 0.430 | -           | 10.92 | 7     |

| L              | 0.115     | 0.150 | 2.93        | 3.81  | 4     |

| N              | 20        |       | 20          |       | 9     |

Rev. 0 12/93

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; willtary equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

многоканальный

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9