#### ISL8120IR

Dual/n-Phase Buck PWM Controller with Integrated Driver

FN6763 Rev.2.00 November 11, 2011

The ISL8120IRZEC integrates two voltage-mode synchronous buck PWM controllers to control a dual independent voltage regulator or a 2-phase single output regulator. It has PLL circuits and can output a phase-shift-programmable clock signal for the system to be expanded to 3-, 4-, 6-, 12- phases with desired interleaving phase shift. It also integrates current sharing control for the power module to operate in parallel, which offers high system flexibility.

It has voltage feed forward compensation to maintain a constant loop gain for optimal transient response, especially for applications with a wide input voltage range. Its integrated high speed MOSFET drivers and multi-feature functions provide complete control and protection for a 2/n-phase synchronous buck converter, dual independent regulators, or DDR tracking applications (VDDQ and VTT outputs).

The output voltage of a ISL8120IRZEC-based converter can be precisely regulated to as low as the internal reference voltage 0.6V, with a system accuracy of ±0.9% over industrial temperature and line load variations. Channel 2 can track an external ramp signal for DDR/tracking applications.

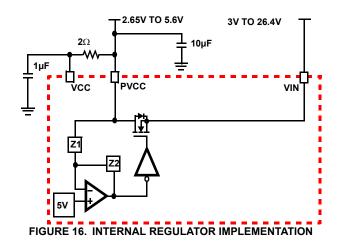

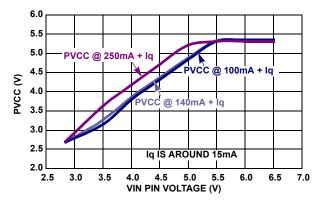

The ISL8120IRZEC integrates an internal linear regulator, which generates VCC from input rail for applications with only one single supply rail. The internal oscillator is adjustable from 150kHz to 1.5MHz, and is able to track an external clock signal for frequency synchronization and phase paralleling applications. The integrated Pre-Biased Digital Soft-Start, Differential Remote Sensing Amplifier, and Programmable Input Voltage POR features enhance the value of ISL8120IRZEC.

The ISL8120IRZEC protects against overcurrent conditions by inhibiting the PWM operation while monitoring the current with  $r_{\rm DS(ON)}$  of the lower MOSFET, DCR of the output inductor, or a precision resistor. It also has a PRE-POR Overvoltage Protection option, which provides some protection to the load device if the upper MOSFET(s) is shorted. See "PRE-POR Overvoltage Protection (PRE-POR-OVP)" on page 24 for details.

The ISL8120IRZEC's Fault Hand Shake feature protects any channel from overloading/stressing due to system faults or phase failure. The undervoltage fault protection features are also designed to prevent a negative transient on the output voltage during falling down. This eliminates the Schottky diode that is used in some systems for protecting the load device from reversed output voltage damage.

#### Features

- Full Traceability Through Assembly and Test by Date/Trace Code Assignment

- Enhanced Process Change Notification per MIL-PRF-38535

- Enhanced Obsolescence Management

- Wide VIN Range Operation: 3V to 22V

- VCC Operation from 3V to 5.60V

- · Fast Transient Response

- 80MHz Bandwidth Error Amplifier

- Voltage-Mode PWM Leading-Edge Modulation Control

- Voltage Feed-Forward

- Dual Channel 5V High Speed 4A MOSFET Gate Drivers

- Internal Bootstrap Diodes

- · Internal Linear Regulator Provides a 5.4V Bias from VIN

- External Soft-Start Ramp Reference Input for DDR/Tracking Applications

- · Excellent Output Voltage Regulation

- 0.6V ±0.6%/±0.9% Internal Reference Over Industrial Temperature

- True Differential Remote Voltage Sensing

- Oscillator Programmable from 150kHz to 1.5MHz

- Frequency Synchronization

- Scale for 1-, 2-, 3-, 4-, 6-, up to 12- Phase with Single Output

- Excellent Phase Current Balancing

- Programmable Phase Shift Between the 2 Phases Controlled by the ISL8120IRZEC and Programmable Phase Shift for Clockout Signal

- Interleaving Operation Results in Minimum Input RMS Current and Minimum Output Ripple Current

- · Fault Hand Shake Capability for High System Reliability

- · Overcurrent Protection

- DCR, r<sub>DS(ON)</sub>, or Precision Resistor Current Sensing

- Independent and Average Phase Current OCP

- · Output Overvoltage and Undervoltage Protections

- Programmable Phase Shift in Dual Mode Operation

- · Digital Soft-Start with Pre-Charged Output Start-up Capability

- · Power-Good Indication

- Dual Independent Channel Enable Inputs with Precision Voltage Monitor and Voltage Feed-Forward Capability

- Programmable Input Voltage POR and its Hysteresis with a Resistor Divider at EN Input

- · Over-Temperature Protection

- · Pre-Power-On-Reset Overvoltage Protection Option

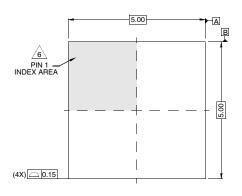

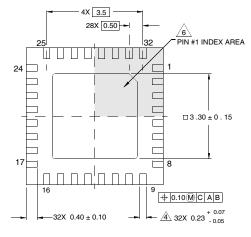

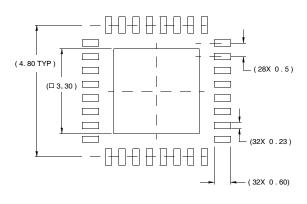

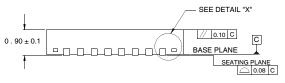

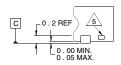

- 32 Ld 5x5 QFN Package Near Chip-Scale Footprint

- Enhanced Thermal Performance for MHz Applications

- Pb-Free (RoHS compliant)

#### **Applications**

- · Power Supply for Datacom/Telecom and POL

- · Paralleling Power Module

- · Wide and Narrow Input Voltage Range Buck Regulators

- · DDR I and II Applications

- · High Current Density Power Supplies

- · Multiple Outputs VRM and VRD

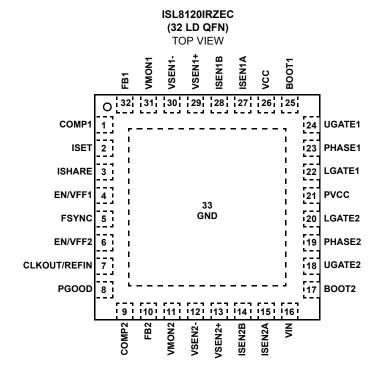

#### **Pinout**

#### Related Literature

Technical Brief TB389 "PCB Land Pattern Design and Surface Mount Guidelines for QFN (MLFP) Packages"

## **Ordering Information**

| PART<br>NUMBER<br>(Note) | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------|-----------------|------------------------|----------------------|----------------|

| ISL8120IRZEC             | ISL8120 IRZ     | -40 to +85             | 32 Ld QFN            | L32.5x5B       |

| ISL8120IRZ-TEC*          | ISL8120 IRZ     | -40 to +85             | 32 Ld QFN            | L32.5x5B       |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

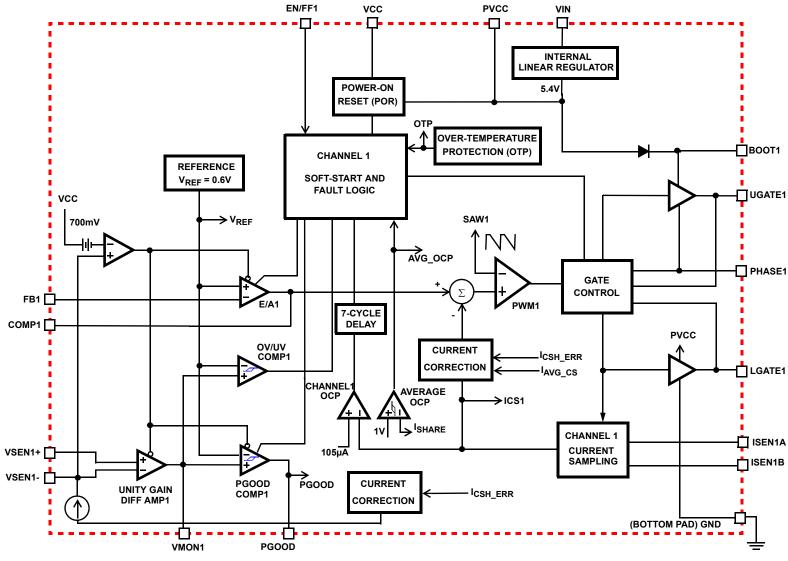

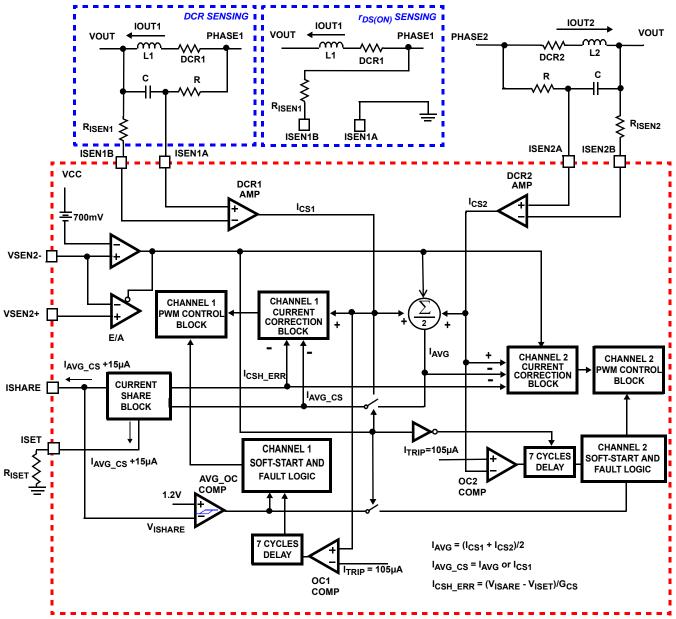

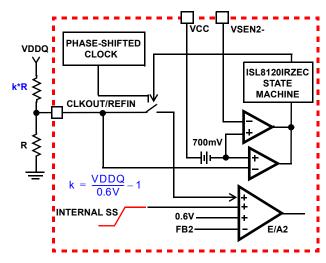

## Block Diagram (1/2)

FIGURE 1. CHANNEL/PHASE 1 (VDDQ)

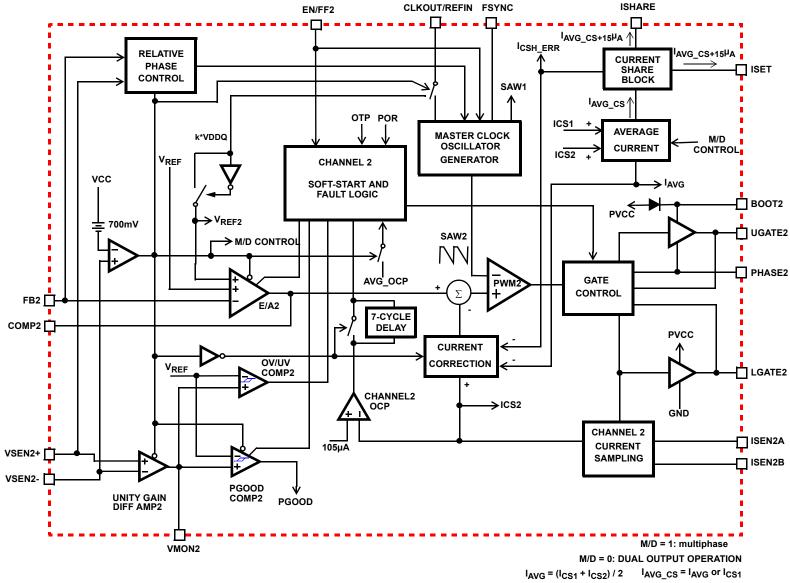

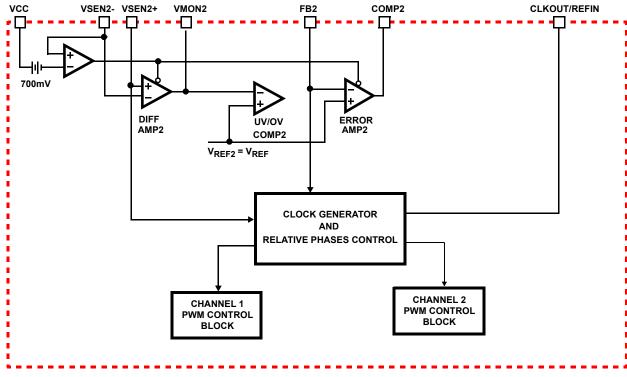

## Block Diagram (2/2)

ICSH ERR = (VISARE - VISET)/GCS

0.6V =k\*VDDQ

FIGURE 2. CHANNEL/PHASE 2 (VTT)

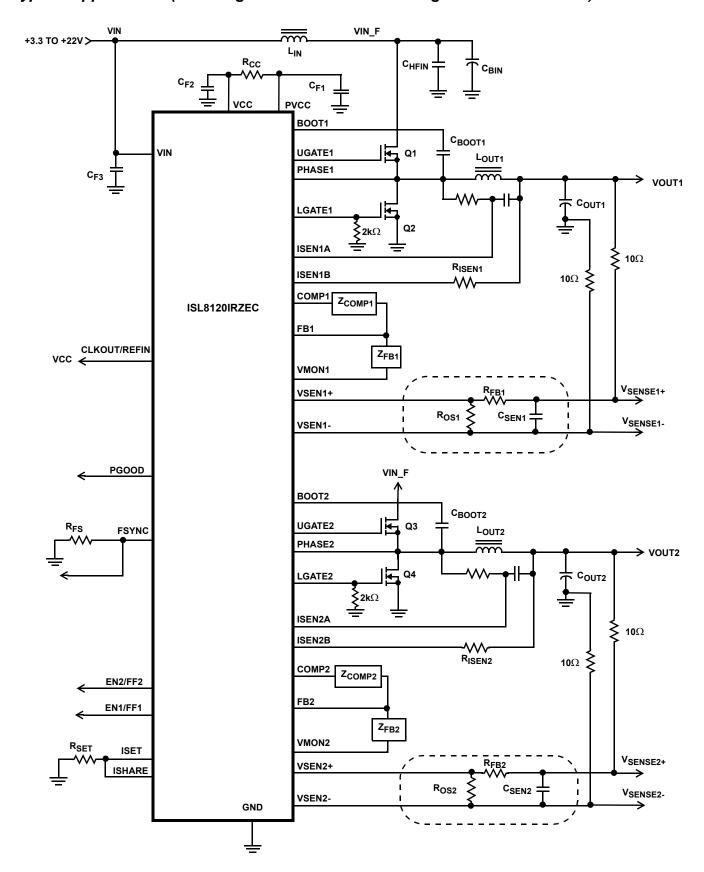

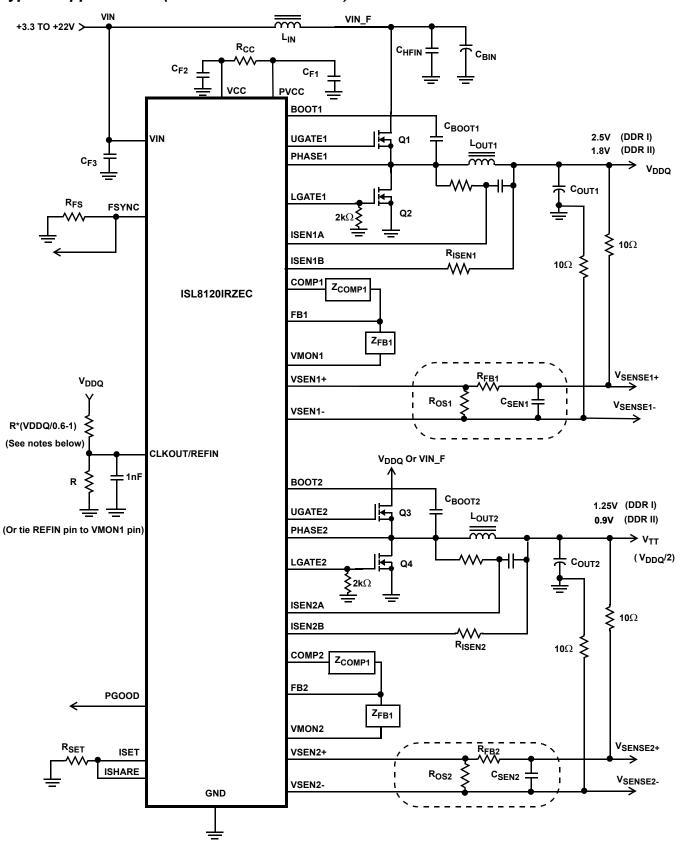

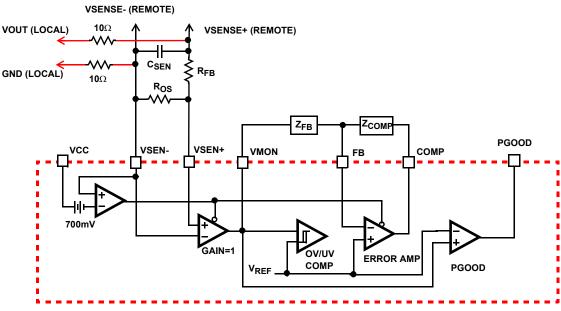

## Typical Application I (Dual Regulators with DCR Sensing and Remote Sense)

## Typical Application II (Double Data Rate I or II)

Note 1: Set the upper resistor to be a little higher than R\*(VDDQ/0.6 - 1) will set the final REFIN voltage (stead state voltage after soft-start) derived from the VDDQ to be a little higher than internal 0.6V reference. In this way, the VTT final voltage will use the internal 0.6V reference after soft-start.

Note 2: Another way to set REFIN voltage is to connect VMON1 directly to REFIN pin.

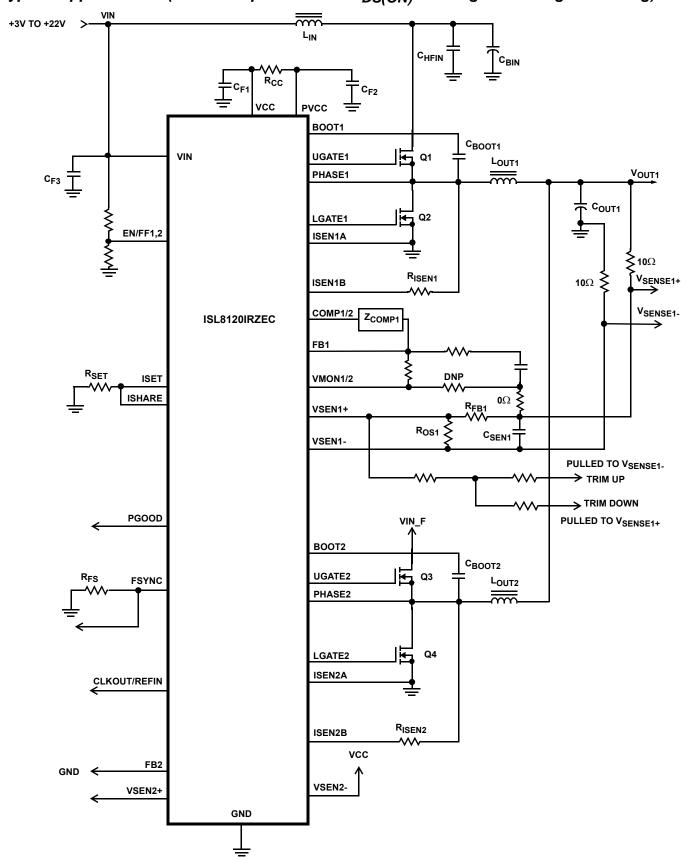

## Typical Application III (2-Phase Operation with $r_{DS(ON)}$ Sensing and Voltage Trimming)

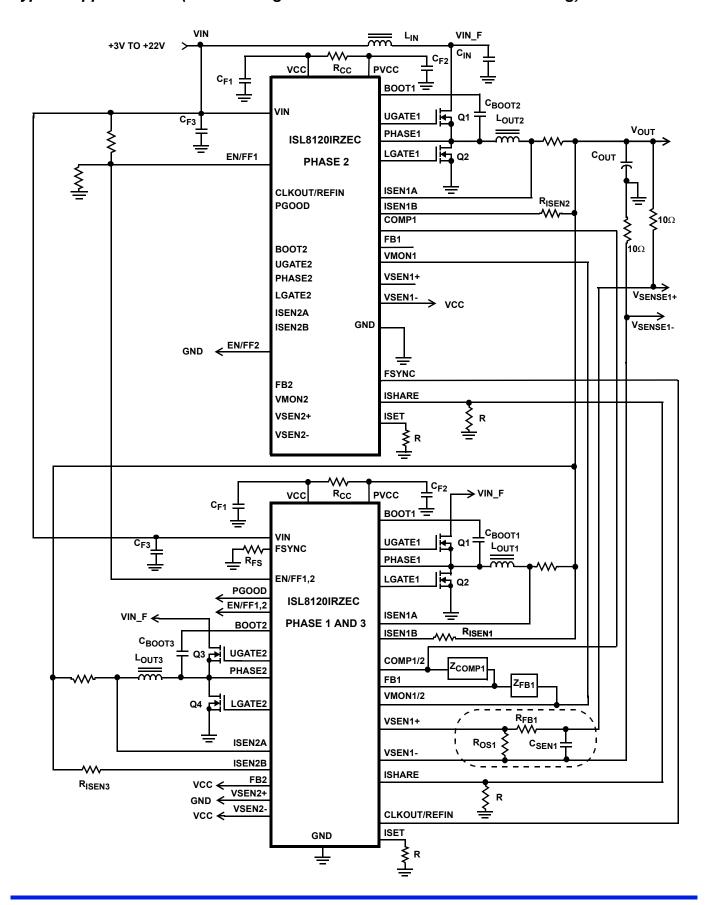

## Typical Application IV (3-Phase Regulator with Precision Resistor Sensing)

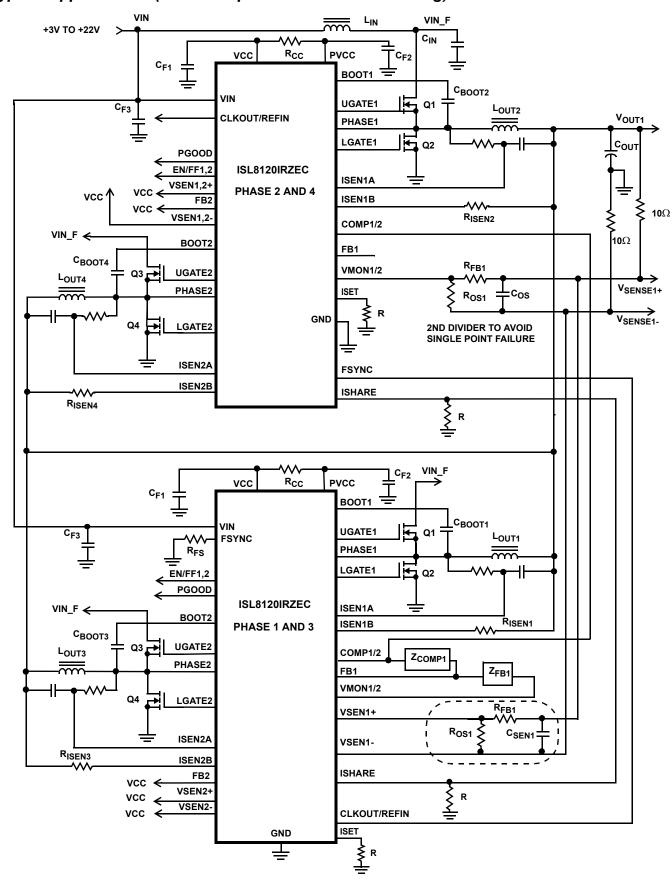

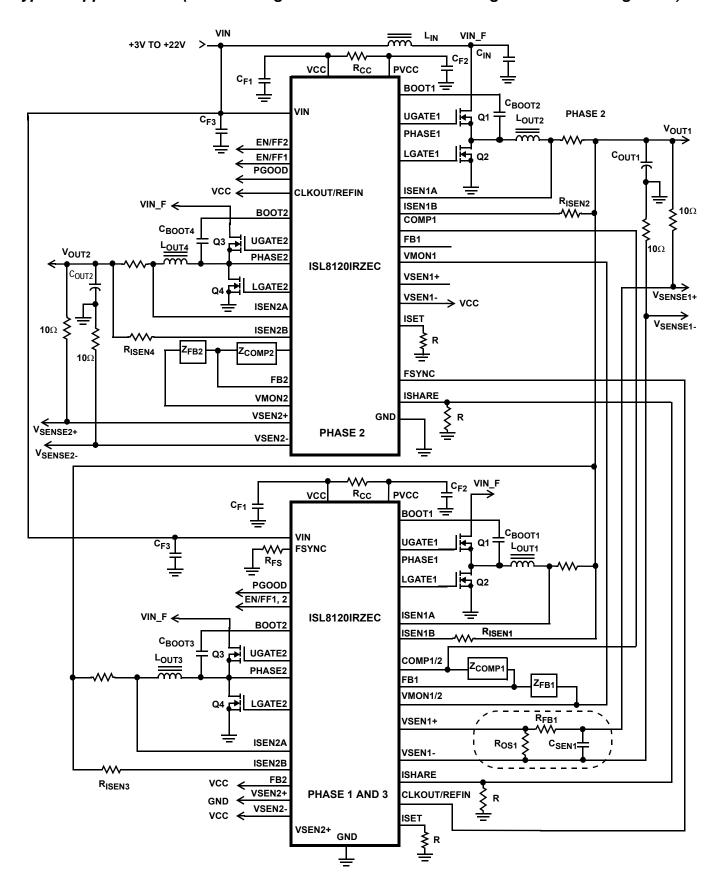

## Typical Application V (4 Phase Operation with DCR Sensing)

## Typical Application VI (3-Phase Regulator with Resistor Sensing and 1 Phase Regulator)

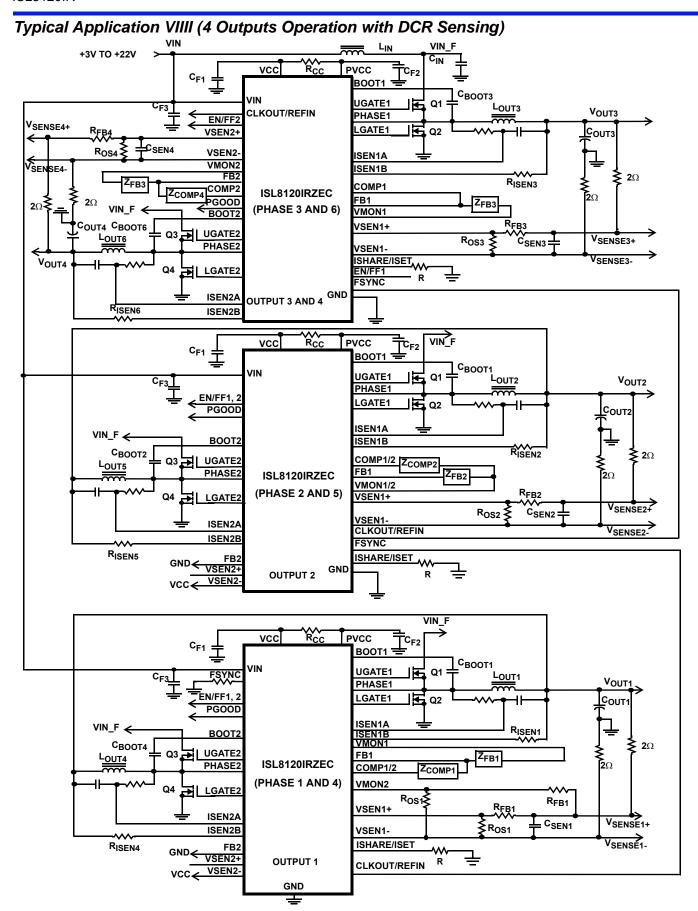

#### Typical Application VII (6 Phase Operation with DCR Sensing) VIN VIN\_F +3V TO +22V CIN C<sub>F1</sub> 章 VCC **PVCC** Своотз UGATE1 Q1 L<sub>OUT</sub>3 CLKOUT/REFIN PHASE1 EN/FF1, 2 **∐** € Q2 LGATE1 PGOOD ISEN1A GND← ISEN1B VSEN2+ ISL8120IRZEC VSEN2-R<sub>ISEN3</sub> COMP1/2 PHASE 3 AND 6 VIN\_F ← BOOT2 FB1 VMON1/2 Своот6\_ UGATE2 LOUT6 VSEN1+ VSEN1- VCC PHASE2 ISET **→** LGATE2 ISEN2A FSYNC ISEN2B **ISHARE GND** R<sub>ISEN6</sub> K<sub>CC</sub> VIN\_F PVCC vcc BOOT1 = $C_{\text{BOOT2}}$ VIN UGATE1 Q1 L<sub>OUT</sub>2 PHASE1 EN/FF1. 2 LGATE1 **₫** Q2 PGOOD ISEN1A VIN\_F ← ISEN1B BOOT2 RISEN2 C<sub>BOOT5</sub> **■** UGATE2 COMP1/2 Q3 L<sub>OUT5</sub> FB1 PHASE2 ISL8120IRZEC VMON1/2 VSEN1+ Q4 → LGATE2 VSEN1- VCC ISEN2A **FSYNC** ISEN2B ISHARE R<sub>ISEN5</sub> PHASE 2 AND 5 GND <del> VSEN2+</del> ISET VCC <del> ✓ VSEN2-</del> **GND** ᆂ VIN\_F Kcc vcc **PVCC** BOOT1 C<sub>BOOT1</sub> VIN UGATE1 Q1 L<sub>OUT</sub>1 V<sub>OUT1</sub> PHASE1 EN/FF1, 2 LGATE1 **€** Q2 COUT **PGOOD** ISEN1A VIN\_F ← R<sub>ISEN1</sub> ISEN1B C<sub>BOOT4</sub> VMON1 10 $\Omega$ UGATE2 Z<sub>FB1</sub> L<sub>OUT4</sub> . 10Ω PHASE2 COMP1/2 Z<sub>COMP1</sub> ISL8120IRZEC VMON2 LGATE2 Q4 **^** R<sub>OS1</sub> R<sub>FB1</sub> R<sub>FB1</sub> VSEN1+ ISEN2A V<sub>SENSE1+</sub> C<sub>SEN1</sub> ≸R<sub>OS1</sub> ISEN2B VSEN1-V<sub>SENSE1</sub> ISHARE RISEN4 FB2 VSEN2+ CLKOUT/REFIN Şĸ PHASE 1 AND 4 VSEN2-ISET GND \_

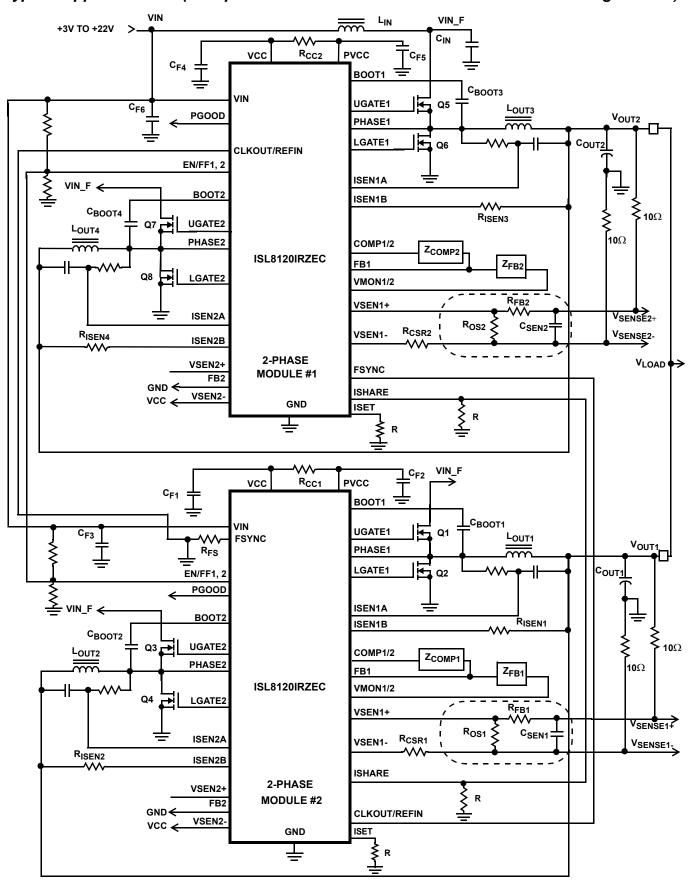

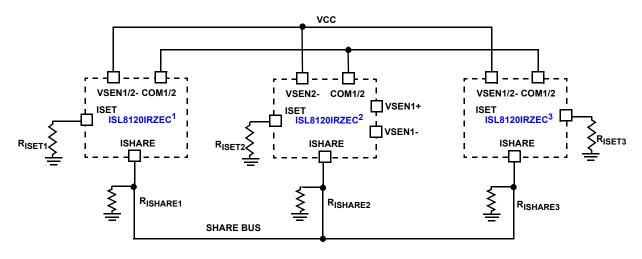

## Typical Application VIII (Multiple Power Modules in Parallel with Current Sharing Control)

#### **Absolute Maximum Ratings**

| Input Voltage, VIN0.3V to +27V                                                       |

|--------------------------------------------------------------------------------------|

| Driver Bias Voltage, PVCC0.3V to +6.5V                                               |

| Signal Bias Voltage, VCC0.3V to +6.5V                                                |

| BOOT/UGATE Voltage, V <sub>BOOT</sub> 0.3V to +36V                                   |

| Phase Voltage, V <sub>PHASE</sub> V <sub>BOOT</sub> - 7V to V <sub>BOOT</sub> + 0.3V |

| BOOT to PHASE Voltage, VBOOT - VPHASE0.3V to VCC +0.3V                               |

| Input, Output or I/O Voltage0.3V to VCC +0.3V                                        |

## **Thermal Information**

| Thermal Resistance (Typical Notes 1, 2) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| 32 Ld QFN Package                       | 32                     | 3.5                    |

| Maximum Junction Temperature            | 55                     | °C to +150°C           |

| Maximum Storage Temperature Range       | 65                     | °C to +150°C           |

| Pb-free Reflow Profile                  |                        | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeF | Reflow.asp             |                        |

#### **Recommended Operating Conditions**

| Input Voltage, VIN                                  | . 3V to 22V |

|-----------------------------------------------------|-------------|

| Driver Bias Voltage, PVCC                           | 3V to 5.6V  |

| Signal Bias Voltage, VCC                            | 3V to 5.6V  |

| Boot to Phase Voltage (Overcharged), VBOOT - VPHASE | <6V         |

| Industrial Ambient Temperature Range40°             | °C to +85°C |

| Maximum Junction Temperature Range                  | +125°C      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features.

- 2. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is the center of the exposed metal pad on the package underside.

- 3. Limits should be considered typical and are not production tested.

### **Electrical Specifications**

Recommended Operating Conditions, Unless Otherwise Noted. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| PARAMETER                                | SYMBOL               | TEST CONDITIONS                                                                                               | MIN  | TYP  | MAX  | UNITS  |

|------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| VCC SUPPLY CURRENT                       |                      |                                                                                                               |      |      | "    | '      |

| Nominal Supply VIN Current               | I <sub>Q_VIN</sub>   | VIN = 20V; VCC = PVCC; No Load;<br>F <sub>SW</sub> = 500kHz                                                   | 11   | 15   | 20   | mA     |

| Nominal Supply VIN Current               | I <sub>Q_VIN</sub>   | VIN=3.3V;VCC = PVCC; No Load;<br>F <sub>SW</sub> = 500kHz                                                     | 8    | 12   | 14   | mA     |

| Shutdown Supply PVCC Current             | I <sub>PVCC</sub>    | EN = 0V, PVCC = 5V                                                                                            | 0.5  | 1    | 1.4  | mA     |

| Shutdown Supply VCC Current              | lvcc                 | EN = 0V, VCC = 3V                                                                                             | 7    | 10   | 12   | mA     |

| INTERNAL LINEAR REGULATOR                |                      |                                                                                                               |      |      |      |        |

| Maximum Current (Note 3)                 | I <sub>PVCC</sub>    | PVCC = 4V to 5.6V                                                                                             |      | 250  |      | mA     |

|                                          |                      | PVCC = 3V to 4V                                                                                               |      | 150  |      | mA     |

| Saturated Equivalent Impedance (Note 3)  | R <sub>LDO</sub>     | P-Channel MOSFET (VIN = 5V)                                                                                   |      | 1    |      | Ω      |

| PVCC Voltage Level                       | PVCC                 | I <sub>PVCC</sub> = 0mA to 250mA                                                                              | 5.1  | 5.4  | 5.6  | V      |

| POWER-ON RESET                           |                      |                                                                                                               |      |      |      |        |

| Rising VCC Threshold                     |                      |                                                                                                               |      | 2.85 | 3    | V      |

| Falling VCC Threshold                    |                      |                                                                                                               |      | 2.65 | 2.75 | V      |

| Rising PVCC Threshold                    |                      |                                                                                                               |      | 2.85 | 3.05 | V      |

| Falling PVCC Threshold                   |                      |                                                                                                               |      | 2.65 | 2.75 | V      |

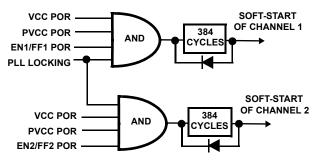

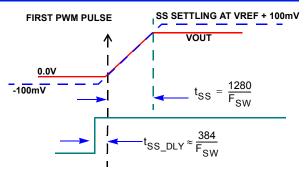

| System Soft-Start Delay (Note 3)         | t <sub>SS_DLY</sub>  | After PLL, VCC, and PVCC PORs, and EN(s) above their thresholds                                               |      | 384  |      | Cycles |

| ENABLE                                   |                      |                                                                                                               |      |      |      |        |

| Turn-On Threshold Voltage                |                      |                                                                                                               | 0.75 | 8.0  | 0.86 | V      |

| Hysteresis Sink Current                  | I <sub>EN_HYS</sub>  |                                                                                                               | 25   | 30   | 35   | μA     |

| Undervoltage Lockout Hysteresis (Note 3) | V <sub>EN_HYS</sub>  | V <sub>EN_RTH</sub> = 10.6V; V <sub>EN_FTH</sub> = 9V<br>R <sub>UP</sub> = 53.6kΩ, R <sub>DOWN</sub> = 5.23kΩ |      | 1.5  |      | V      |

| Sink Current                             | I <sub>EN_SINK</sub> |                                                                                                               |      |      | 15   | mA     |

| Sink Impedance                           | R <sub>EN_SINK</sub> | I <sub>EN_SINK</sub> = 5mA                                                                                    |      |      | 65   | Ω      |

## Electrical Specifications

Recommended Operating Conditions, Unless Otherwise Noted. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. **(Continued)**

| PARAMETER                                                                         | SYMBOL                          | TEST CONDITIONS                                                                                                       | MIN   | TYP       | MAX       | UNITS            |

|-----------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-----------|-----------|------------------|

| OSCILLATOR                                                                        | I.                              |                                                                                                                       |       |           |           |                  |

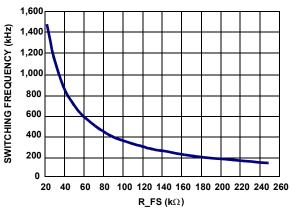

| Oscillator Frequency Range                                                        |                                 |                                                                                                                       | 150   |           | 1500      | kHz              |

| Oscillator Frequency                                                              |                                 | RFS = 100k, Figure 20                                                                                                 | 344   | 377       | 406       | kHz              |

| Total Variation                                                                   |                                 | VCC = 5V; -40°C < T <sub>A</sub> <+85°C                                                                               | -9    |           | +9        | %                |

| Peak-to-Peak Ramp Amplitude                                                       | $\Delta V_{RAMP}$               | VCC = 5V, V <sub>EN</sub> = 0.8V                                                                                      |       | 1         |           | V <sub>P-P</sub> |

| Linear Gain of Ramp Over V <sub>EN</sub>                                          | G <sub>RAMP</sub>               | G <sub>RAMP</sub> = ΔV <sub>RAMP</sub> /V <sub>EN</sub>                                                               |       | 1.25      |           |                  |

| Ramp Peak Voltage                                                                 | V <sub>RAMP_PEAK</sub>          | V <sub>EN</sub> = VCC                                                                                                 |       | VCC - 1.4 |           | V                |

| Peak-to-Peak Ramp Amplitude                                                       | ΔV <sub>RAMP</sub>              | V <sub>EN</sub> = VCC = 5.4V, R <sub>UP</sub> = 2k                                                                    |       | 3         |           | V <sub>P-P</sub> |

| Peak-to-Peak Ramp Amplitude                                                       | $\Delta V_{RAMP}$               | V <sub>EN</sub> = VCC = 3V; R <sub>UP</sub> = 2k                                                                      |       | 0.6       |           | V <sub>P-P</sub> |

| Ramp Amplitude Upon Disable                                                       | $\Delta V_{RAMP}$               | V <sub>EN</sub> = 0V; VCC = 3.5V to 5.5V                                                                              |       | 1         |           | V <sub>P-P</sub> |

| Ramp Amplitude Upon Disable                                                       | $\Delta V_{RAMP}$               | V <sub>EN</sub> = 0V; VCC < 3.4V                                                                                      |       | VCC - 2.4 |           | V <sub>P-P</sub> |

| Ramp DC Offset                                                                    | V <sub>RAMP_OS</sub>            |                                                                                                                       |       | 1         |           | V                |

| FREQUENCY SYNCHRONIZATION AND                                                     |                                 | OOP                                                                                                                   |       |           |           |                  |

| Synchronization Frequency                                                         |                                 | VCC = 5.4V (3V)                                                                                                       | 150   |           | 1500      | kHz              |

| PLL Locking Time                                                                  |                                 | VCC = 5.4V (3V); F <sub>SW</sub> = 400kHz;                                                                            |       | 105       |           | μs               |

| Input Signal Duty Cycle Range (Note 3)                                            |                                 |                                                                                                                       | 10    |           | 90        | %                |

| PWM                                                                               |                                 |                                                                                                                       |       |           |           |                  |

| Minimum PWM OFF Time                                                              | t <sub>MIN_OFF</sub>            |                                                                                                                       | 310   | 345       | 410       | ns               |

| Current Sampling Blanking Time (Note 3)                                           | t <sub>BLANKING</sub>           |                                                                                                                       |       | 175       |           | ns               |

| REFERENCE                                                                         |                                 |                                                                                                                       |       |           |           |                  |

| Channel 1 Reference Voltage (Include                                              | V <sub>REF1</sub>               |                                                                                                                       |       | 0.6       |           | V                |

| Error and Differential Amplifiers' Offsets)                                       |                                 |                                                                                                                       | -0.7  |           | 0.7       | %                |

| Channel 2 Reference Voltage (Include                                              | V <sub>REF2</sub>               |                                                                                                                       |       | 0.6       |           | V                |

| Error and Differential Amplifiers' Offsets)                                       |                                 |                                                                                                                       | -0.75 |           | 0.95      | %                |

| ERROR AMPLIFIER                                                                   |                                 |                                                                                                                       |       |           |           |                  |

| DC Gain (Note 3)                                                                  |                                 | R <sub>L</sub> = 10k, C <sub>L</sub> = 100p, at COMP Pin                                                              |       | 98        |           | dB               |

| Unity Gain-Bandwidth (Note 3)                                                     | UGBW_EA                         | R <sub>L</sub> = 10k, C <sub>L</sub> = 100p, at COMP Pin                                                              |       | 80        |           | MHz              |

| Input Common Mode Range (Note 3)                                                  |                                 |                                                                                                                       | -0.2  |           | VCC - 1.8 | V                |

| Output Voltage Swing                                                              |                                 | VCC = 5V                                                                                                              | 0.85  |           | VCC - 1.0 | V                |

| Slew Rate (Note 3)                                                                | SR_EA                           | R <sub>L</sub> = 10k, C <sub>L</sub> = 100p, at COMP Pin                                                              |       | 20        |           | V/µs             |

| Input Current (Note 3)                                                            | I <sub>FB</sub>                 | Positive direction into the FB pin                                                                                    |       | 100       |           | nA               |

| Output Sink Current                                                               | I <sub>COMP</sub>               |                                                                                                                       |       | 3         |           | mA               |

| Output Source Current                                                             | ICOMP                           |                                                                                                                       |       | 6         |           | mA               |

| Disable Threshold (Note 3)                                                        | V <sub>VSEN</sub> -             |                                                                                                                       |       | VCC - 0.4 |           | V                |

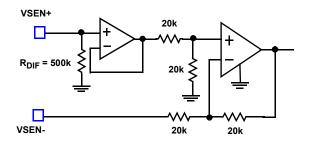

| DIFFERENTIAL AMPLIFIER                                                            | -                               |                                                                                                                       |       |           |           |                  |

| DC Gain (Note 3)                                                                  | UG_DA                           | Unity Gain Amplifier                                                                                                  |       | 0         |           | dB               |

| Unity Gain Bandwidth (Note 3)                                                     | UGBW_DA                         |                                                                                                                       |       | 5         |           | MHz              |

| Negative Input Source Current (Note 3)                                            | I <sub>VSEN</sub> -             |                                                                                                                       |       | 100       |           | nA               |

| Maximum Source Current for Current<br>Sharing (Typical Application VIII) (Note 3) | I <sub>VSEN1</sub> -            | VSEN1- Source Current for Current<br>Sharing when parallel multiple modules<br>each of which has its own voltage loop |       | 350       |           | μΑ               |

| Input Impedance                                                                   | R <sub>VSEN+_to</sub><br>_VSEN- |                                                                                                                       |       | 1         |           | МΩ               |

| Output Voltage Swing (Note 3)                                                     |                                 |                                                                                                                       | 0     |           | VCC - 1.8 | V                |

| Input Common Mode Range (Note 3)                                                  |                                 |                                                                                                                       | -0.2  |           | VCC - 1.8 | V                |

# Electrical Specifications

Recommended Operating Conditions, Unless Otherwise Noted. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. **(Continued)**

| PARAMETER                                   | SYMBOL                  | TEST CONDITIONS                                        | MIN  | TYP       | MAX  | UNITS |

|---------------------------------------------|-------------------------|--------------------------------------------------------|------|-----------|------|-------|

| Disable Threshold (Note3)                   | V <sub>VSEN-</sub>      | V <sub>MON1,2</sub> = Tri-State                        |      | VCC - 0.4 |      | V     |

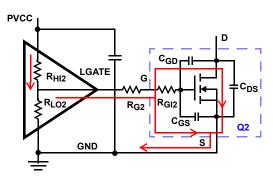

| GATE DRIVERS                                |                         |                                                        | •    | "         |      |       |

| Upper Drive Source Resistance               | R <sub>UGATE</sub>      | 45mA Source Current                                    |      | 1.0       |      | Ω     |

| Upper Drive Sink Resistance                 | R <sub>UGATE</sub>      | 45mA Sink Current                                      |      | 1.0       |      | Ω     |

| Lower Drive Source Resistance               | R <sub>LGATE</sub>      | 45mA Source Current                                    |      | 1.0       |      | Ω     |

| Lower Drive Sink Resistance                 | R <sub>LGATE</sub>      | 45mA Sink Current                                      |      | 0.4       |      | Ω     |

| OVERCURRENT PROTECTION                      |                         |                                                        | •    |           |      |       |

| Channel Overcurrent Limit (Note 3)          | I <sub>SOURCE</sub>     | VCC = 3V to 5.6V                                       |      | 108       |      | μA    |

| Channel Overcurrent Limit                   | I <sub>SOURCE</sub>     | VCC = 5V                                               | 89   | 108       | 122  | μA    |

| Share Pin OC Threshold                      | V <sub>OC_SET</sub>     | VCC = 3V to 5.6V (comparator offset included)          | 1.16 | 1.20      | 1.22 | V     |

| Share Pin OC Hysteresis (Note 3)            | V <sub>OC_SET_HYS</sub> | VCC = 3V to 5.6V (comparator offset included)          |      | 50        |      | mV    |

| CURRENT SHARE                               |                         |                                                        |      | +         |      |       |

| Internal Balance Accuracy (Note 3)          |                         | VCC = 3V and 3.6V, 1% Resistor<br>Sense, 10mV Signal   |      | ±5        |      | %     |

| Internal Balance Accuracy (Note 3)          |                         | VCC = 4.5V and 5.6V, 1% Resistor<br>Sense, 10mV Signal |      | ±5        |      | %     |

| External Current Share Accuracy (Note 3)    |                         | VCC = 3V and 5.6V, 1% Resistor<br>Sense, 10mV Signal   |      | ±5        |      | %     |

| POWER GOOD MONITOR                          | l .                     |                                                        |      |           |      | -1    |

| Undervoltage Falling Trip Point             | V <sub>UVF</sub>        | Percentage Below Reference Point                       | -15  | -13       | -11  | %     |

| Undervoltage Rising Hysteresis              | V <sub>UVR_HYS</sub>    | Percentage Above UV Trip Point                         |      | 4         |      | %     |

| Overvoltage Rising Trip Point               | V <sub>OVR</sub>        | Percentage Above Reference Point                       | 11   | 13        | 15   | %     |

| Overvoltage Falling Hysteresis              | V <sub>OVF_HYS</sub>    | Percentage below OV Trip Point                         |      | 4         |      | %     |

| PGOOD Low Output Voltage                    |                         | I <sub>PGOOD</sub> = 2mA                               |      |           | 0.35 | V     |

| Sinking Impedance                           |                         | I <sub>PGOOD</sub> = 2mA                               |      |           | 70   | Ω     |

| Maximum Sinking Current (Note 3)            |                         | V <sub>PGOOD</sub> < 0.8V                              |      | 10        |      | mA    |

| OVERVOLTAGE PROTECTION                      |                         |                                                        | •    | "         |      |       |

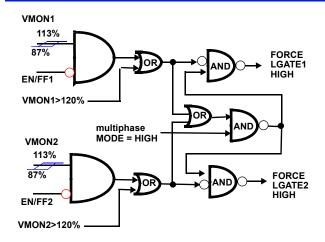

| OV Latching Up Trip Point                   |                         | EN/FF= UGATE = LATCH Low,<br>LGATE = High              | 118  | 120       | 122  | %     |

| OV Non-Latching Up Trip Point (Note 3)      |                         | EN/FF = Low, UGATE = Low,<br>LGATE = High              |      | 113       |      | %     |

| LGATE Release Trip Point                    |                         | EN/FF = Low/HIGH, UGATE = Low,<br>LGATE = Low          |      | 87        |      | %     |

| OVER-TEMPERATURE PROTECTION                 | ı                       |                                                        |      |           |      | 1     |

| Over-Temperature Trip (Note 3)              |                         |                                                        |      | 150       |      | °C    |

| Over-Temperature Release Threshold (Note 3) |                         |                                                        |      | 125       |      | °C    |

#### Functional Pin Description

#### GND (Pin 33, Signal and Power Ground Pad)

All voltage levels are referenced to this pad. This pad provides a return path for the low-side MOSFET drives and internal power circuitries as well as all analog signals. Connect this pad to the circuit ground using the shortest possible path (more than 5 to 6 via to the internal ground plane, placed on the soldering pad are recommended).

#### VIN (Pin 16, Internal Linear Regulator Input)

This pin should be tied directly to the input rail when using the internal linear regulator. It provides power to the internal linear drive circuitry. When used with an external 5V supply, this pin should be tied directly to PVCC. The internal linear device is protected against reverse bias generated by the remaining charge of the decoupling capacitor at PVCC when losing the input rail.

#### VCC (Pin 26, Analog Circuit Bias)

This pin provides power for the analog circuitry. A RC filter is recommended between the connection of this pin to a 3V to 5.6V bias (typically PVCC). R is suggested to be a  $5\Omega$  resistor. And in 3.3V applications, the R could be shorted to allow the low end input in concerns of the VCC falling threshold. The VCC decoupling cap C is strongly recommended to be as large as  $10\mu F$  ceramic capacitor. This pin can be powered either by the internal linear regulator or by an external voltage source.

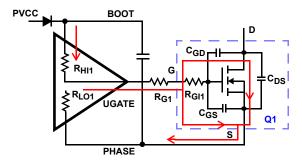

#### BOOT1, 2 (Pins 25, 17)

This pin provides the bootstrap bias for the high-side driver. Internal bootstrap diodes connected to the PVCC pin provide the necessary bootstrap charge. Its typical operational voltage range is 2.5V to 5.6V.

#### UGATE1, 2 (Pin 24, 8)

These pins provide the drive for the high-side devices and should be connected to the MOSFETs' gates.

#### PHASE1, 2 (Pins 23,19)

Connect these pins to the source of the high-side MOSFETs and the drain of the low-side MOSFETs. These pins represent the return path for the high-side gate drives.

#### PVCC (Pin 21, Driver Bias Voltage)

This pin is the output of the internal series linear regulator. It provides the bias for both low-side and high-side drives. Its operational voltage range is 3V to 5.6V. The decoupling ceramic capacitor in the PVCC pin is  $10\mu F$ .

#### LGATE1, 2 (Pins 22, 20)

These pins provide the drive for the low-side devices and should be connected to the MOSFETs' gates.

#### FSYNC (Pin 5)

The oscillator switching frequency is adjusted by placing a resistor  $(R_{FS})$  from this pin to GND. The internal oscillator

will lock to an external frequency source if this pin is connected to a switching square pulse waveform, typically the CLKOUT input signal from another ISL8120IRZEC or an external clock. The internal oscillator synchronizes with the leading edge of the input signal.

#### EN/FF1, 2 (Pins 4, 6)

These are triple function pins. The input voltages to these pins are compared with a precision 0.8V reference and enable their digital soft-starts. By pulling this pin to voltage lower than the threshold, the corresponding channel can be disabled independently. Connecting these pins to input bus through a voltage resistor divider can monitor the input voltage. The undervoltage lockout and its hysteresis levels can be programmed by setting the values of the resistor dividers. The voltages on these pins are also fed into controller to be used to adjust the amplitude of each individual sawtooth independently.

Furthermore, during fault (such as overvoltage, overcurrent, and over-temperature) conditions, these pins (EN/FF\_) are used to communicate the information to other cascaded ICs by pulling low.

#### PGOOD (Pin 8)

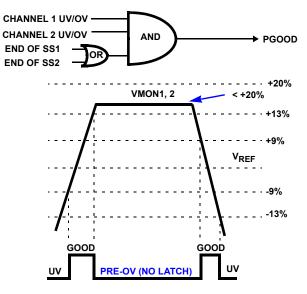

Provides an open drain Power-Good signal when both channels are within 9% of nominal output regulation point with 4% hysteresis (13%/9%) and soft-start is complete. PGOOD monitors the outputs (VMON1/2) of the internal differential amplifiers.

#### ISEN1A, 2A (Pins 27, 15)

These pins are the positive inputs of the current sensing amplifier. Together with ISEN1B,2B, these pins provide r<sub>DS(ON)</sub>, DCR, or precision resistor current sensing.

#### ISEN1B, 2B (Pins 28, 14)

These pins are the negative inputs of the current sensing amplifier. Together with the ISEN1A, 2A pins they provide  $r_{DS(ON)}$ , DCR, or precision resistor current sensing. Refer to "Typical Application III (2-Phase Operation with  $r_{DS(ON)}$  Sensing and Voltage Trimming)" on page 7 for  $r_{DS(ON)}$  sensing set up and "Typical Application V (4 Phase Operation with DCR Sensing)" on page 9 for DCR sensing set-up.

#### ISET (Pin 2)

This pin sources an 15 $\mu$ A offset current plus the average current of both channels in multiphase mode or only Channel 1's current in independent mode. The voltage (V<sub>ISET</sub>) set by an external resistor (R<sub>ISET</sub>) represents the average current level of the local active channel(s). V<sub>ISET</sub> is compared with a 1V threshold for average overcurrent protections. For full-scale current, R<sub>ISET</sub> should be 1V/120 $\mu$ A = 8.33k $\Omega$ . Typically 10k $\Omega$  is used for R<sub>SET</sub>.

#### ISHARE (Pin 3)

This pin is used for current sharing purposes and is configured to current share bus representing all modules' average current. It sources 15µA offset current plus the average current of both channels in multiphase mode or Channel 1's current in independent mode. The share bus (ISHARE pins connected together) voltage (VISHARE) set by an external resistor (RISHARE) represents the average current level of all active channel(s). The ISHARE bus voltage compares with each reference voltage set by each RISET and generates current share error signal for current correction block of each cascaded controller. The share bus impedance RISHARE should be set as RISET/NCTRL (RISET divided by number of active current sharing controllers).

#### CLKOUT/REFIN (Pin 7)

This pin has a dual function depending on the mode in which the chip is operating. It provides clock signal to synchronize with other ISL8120(s) with its VSEN2- pulled within 700mV of VCC for multiphase (3-, 4-, 6-, 8-, 10-, or 12-phase) operation. When the VSEN2- pin is not within 700mV of VCC, ISL8120 is in dual mode (dual independent PWM output). The clockout signal of this pin is not available in this mode, but the ISL8120 can be synchronized to external clock. In dual mode, this pin works as the following two functions:

- An external reference (0.6V target only) can be in place of the Channel 2's internal reference through this pin for DDR/tracking applications (see "Internal Reference and System Accuracy" on page 31).

- The ISL8120IRZEC operates as a dual-PWM controller for two independent regulators with selectable phase degree shift, which is programmed by the voltage level on REFIN (see "DDR and Dual Mode Operation" on page 30).

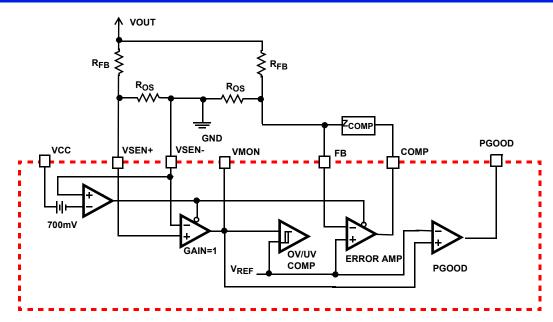

#### FB1, 2 (Pins 32, 10)

These pins are the inverting inputs of the error amplifiers. These pins should be connected to VMON1, 2 with the compensation feedback network. No direct connection between FB and VMON pins is allowed. With VSEN2- pulled within 700mV of VCC, the corresponding error amplifier is disabled and the amplifier's output is high impedance. FB2 is one of the two pins to determine the relative phase relationship between the internal clock of both channels and the CLKOUT signal. See "DDR and Dual Mode Operation" on page 30.

#### COMP1, 2 (Pins 1, 9)

These pins are the error amplifier outputs. They should be connected to FB1, 2 pins through desired compensation networks when both channels are operating independently. When VSEN1-, 2- are pulled within 700mV of VCC, the corresponding error amplifier is disabled and its output (COMP pin) is high impedance. Thus, in multiphase operations, all other SLAVE phases' COMP pins can tie to

the MASTER phase's COMP1 pin (1<sup>st</sup> phase), which modulates each phase's PWM pulse with a single voltage feedback loop. While the error amplifier is not disabled, an independent compensation network is required for each cascaded IC.

#### VSEN1+, 2+ (Pins 29, 13)

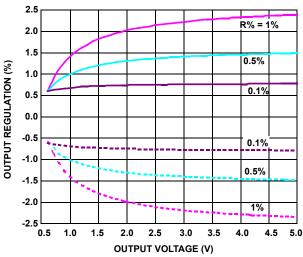

These pins are the positive inputs of the standard unity gain operational amplifier for differential remote sense for the corresponding channel (Channel 1 and 2), and should be connected to the positive rail of the load/processor. These pins can also provide precision output voltage trimming capability by pulling a resistor from this pin to the positive rail of the load (trimming down) or the return (typical VSEN1-2-pins) of the load (trimming up). The typical input impedance of VSEN+ with respect to VSEN- is  $500k\Omega$ . By setting the resistor divider connected from the output voltage to the input of the differential amplifier, the desired output voltage can be programmed. To minimize the system accuracy error introduced by the input impedance of the differential amplifier, a  $100\Omega$  or less resistor is recommended to be used for the lower leg (R<sub>OS</sub>) of the feedback resistor divider.

With VSEN2- pulled within 700mV of VCC, the corresponding error amplifier is disabled and VSEN2+ is one of the two pins to determine the relative phase relationship between the internal clock of both channels and the CLKOUT signal. See "DDR and Dual Mode Operation" on page 30 for details.

#### **VSEN1-, 2- (Pins 30, 12)**

These pins are the negative inputs of standard unity gain operational amplifier for differential remote sense for the corresponding regulator (Channel 1 and 2), and should be connected to the negative rail of the load/processor.

When VSEN1-, 2- are pulled within 700mV of VCC, the corresponding error amplifier and differential amplifier are disabled and their outputs are high impedance. Both VSEN2+ and FB2 input signal levels determine the relative phases between the internal controllers as well as the CLKOUT signal. See "DDR and Dual Mode Operation" on page 30 for details.

When configured as multiple power modules (with independent voltage loop) operating in parallel, in order to implement the current sharing control, a resistor needs to be inserted between VSEN1- pin and output voltage negative sense point (between VSEN1- and lower voltage sense resistor), as shown in the "Typical Application VIII (Multiple Power Modules in Parallel with Current Sharing Control)" on page 12. This introduces a correction voltage for the modules with lower load current to keep the current distribution balanced among modules. The module with the highest load current will automatically become the master module. The recommended value for the VSEN1- resistor is

$100\Omega$  and it should not be large in order to keep the unit gain amplifier input impedance compatibility.

#### VMON1, 2 (Pins 31, 11)

These pins are outputs of the unity gain amplifiers. They are connected internally to the OV/UV/PGOOD comparators. These pins should be connected to the FB1, 2 pins by a standard feedback network when both channels operating independently. When VSEN1-, 2- are pulled within 700mV of VCC, the corresponding differential amplifier is disabled and its output (VMON pin) is high impedance. In such an event, the VMON pin can be used as an additional monitor of the output voltage with a resistor divider to protect the system against single point of failure, which occurs in the system using the same resistor divider for both of the UV/OV comparator and output voltage feedback.

## Modes of Operation

There are 9 typical operation modes depending upon the signal levels on EN1/FF1, EN2/FF2, VSEN2+, VSEN2-, FB2, and CLKOUT/REFIN.

**MODE 1:** The IC is completely disabled when EN1/FF1 and EN2/FF2 are pulled below 0.8V.

MODE 2: With EN1/FF1 pulled low and EN2/FF2 pulled high (Mode 2A), or EN1/FF1 pulled high and EN2/FF2 pulled low (Mode 2B), the ISL8120IRZEC operates as a single phase regulator. the current sourcing out from the ISHARE pin represents the first channel current plus 15µA offset current.

MODE 3: When VSEN2- is used as a negative sense line, both channels' phase shift depends upon the voltage level of CLKOUT/REFIN. When the CLKOUT/REFIN pin is within 29% to 45% of VCC, Channel 2 delays 0° over Channel 1 (Mode 3A); when within 45% to 62% of VCC, 90°delay (Mode 3B); when greater than 62% to VCC, 180° delay (Mode 3C). Refer to the "DDR and Dual Mode Operation" on page 30.

MODE 4: When VSEN2- is used as a negative remote sense line, and CLKOUT/REFIN is connected to a external voltage ramp lower than the internal soft-start ramp and lower than 0.6V, the external ramp signal will replaces Channel 2's internal soft-start ramp to be tracked at start-up, controller operating in DDR mode. The controller will use the lowest voltage among the internal 0.6V reference, the external voltage in CLKOUT/REFIN pin and the soft-start ramp signal. Channel 1 is delayed 60° behind Channel 2. Refer to the "DDR and Dual Mode Operation" on page 30.

MODE 5: With VSEN2- pulled within 700mV of VCC and FB2 pulled to ground, the internal channels are 180° out-of-phase and operate in 2-phase single output mode (5A). The CLKOUT/REFIN pin (rising edge) also signals out clock with 60° phase shift relative to the Channel 1's clock signal (falling edge of PWM) for 6-phase operation with two other ISL8120IRZECs (5B). When the share Pins are not connected to each other for the three ICs in sync, two of which can operate in Mode 5A (3 independent outputs can be generated (Mode 5D)) and Modes 3 and 4 (to generate 4 independent outputs (Mode 5C)) respectively.

**MODE 6:** With VSEN2- pulled within 700mV of VCC, FB2 pulled high and VSEN2+ pulled low, the internal channels (as 1<sup>st</sup> and 3<sup>rd</sup> Phase, respectively) are 240° out-of-phase and operate in 3-phase single output mode, combined with another ISL8120IRZEC at MODE 2B. The CLKOUT/REFIN pin signals out 120° relative phases to the falling edge of Channel 1's clock signal to synchronize with the second ISL8120IRZEC's Channel 1 (as 2<sup>nd</sup> Phase).

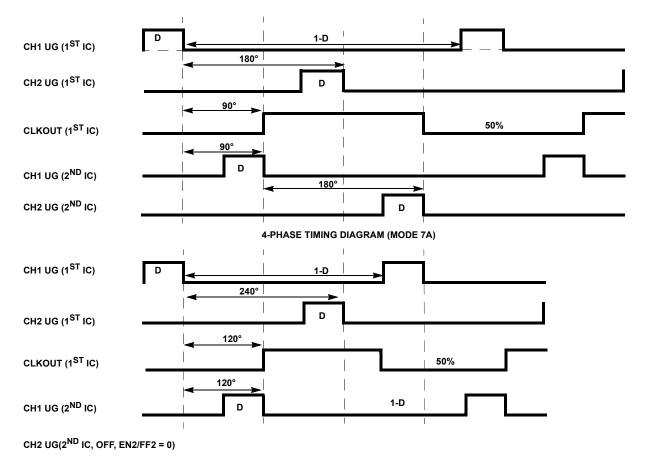

MODE 7: With VSEN2- pulled within 700mV of VCC and FB2 and VSEN2+ pulled high, the internal channels is 180° out-of-phase. The CLKOUT/REFIN pin (rising edge) signals out 90° relative phase to the Channel 1's clock signal (falling edge of PWM) to synchronize with another ISL8120IRZEC, which can operate at Mode 3, 4, 5A, or 7A. A 4-phase single output converter can be constructed with two ISL8120IRZECs operating in Mode 5A or 7A (Mode 7A). If the share bus is not connected between ICs, each IC could generate an independent output (Mode 7B). When the second ISL8120IRZEC operates as two independent regulators (Mode 3) or in DDR mode (Mode 4), then three independent output system is generated (Mode 7C). Both ICs can also be constructed as a 3-phase converter (0°, 90°, and 180°, not a equal phase shift for 3-phase) with a single phase regulator (270°).

**MODE 8**: The output CLKOUT signal allows expansion for 12-phase operation with the cascaded sequencing as shown in Table 1. No external clock is required in this mode for the desired phase shift.

**MODE 9:** With an external clock, the part can be expanded for 5, 7, 8, 9 10 and 11 phase single output operation with the desired phase shift.

TABLE 1.

|      | 1ST IC (I = INPUT; O = OUTPUT; I/O = INPUT AND OUTPUT, Bi-DIRECTION)  MODES OF OPERATION |                    |                         |         |                |                                     |                                                  |                                         |                                            |                                            |                                            |

|------|------------------------------------------------------------------------------------------|--------------------|-------------------------|---------|----------------|-------------------------------------|--------------------------------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| MODE | EN1/<br>FF1<br>(I)                                                                       | EN2/<br>FF2<br>(I) | VSEN2-                  | FB2 (I) | VSEN2<br>+ (I) | CLKOUT/REFIN<br>WRT 1ST<br>(I or O) | ISHARE (I/O) REPRESENTS WHICH CHANNEL(S) CURRENT | 2ND CHANNEL<br>WRT 1ST (O)<br>(Note)    | OPERATION<br>MODE<br>of 2 <sup>ND</sup> IC | OPERATION<br>MODE<br>of 3 <sup>RD</sup> IC | OUTPUT (See<br>Description<br>for Details) |

| 1    | 0                                                                                        | 0                  | -                       | -       | -              | -                                   | -                                                | -                                       | -                                          | -                                          | DISABLED                                   |

| 2A   | 0                                                                                        | 1                  | ACTIVE                  | ACTIVE  | ACTIVE         | -                                   | N/A                                              | VMON1 =<br>VMON2 to Keep<br>PGOOD Valid | -                                          | -                                          | SINGLE<br>PHASE                            |

| 2B   | 1                                                                                        | 0                  | -                       | -       | -              | -                                   | 1 <sup>ST</sup> CHANNEL                          | VMON1 =<br>VMON2 to Keep<br>PGOOD Valid | -                                          | -                                          | SINGLE<br>PHASE                            |

| ЗА   | -                                                                                        | -                  | <vcc -<br="">0.7V</vcc> | ACTIVE  | ACTIVE         | 29% to 45% of<br>VCC (I)            | 1 <sup>ST</sup> CHANNEL                          | 0°                                      | -                                          | -                                          | DUAL<br>REGULATOR                          |

| 3B   | -                                                                                        | -                  | <vcc -<br="">0.7V</vcc> | ACTIVE  | ACTIVE         | 45% to 62% of<br>VCC (I)            | 1 <sup>ST</sup> CHANNEL                          | 90°                                     | -                                          | -                                          | DUAL<br>REGULATOR                          |

| 3C   | -                                                                                        | -                  | <vcc -<br="">0.7V</vcc> | ACTIVE  | ACTIVE         | > 62% of VCC (I)                    | 1 <sup>ST</sup> CHANNEL                          | 180°                                    | -                                          | -                                          | DUAL<br>REGULATOR                          |

| 4    | -                                                                                        | -                  | <vcc-<br>0.7V</vcc-<br> | ACTIVE  | ACTIVE         | < 29% of VCC (I)                    | 1 <sup>ST</sup> CHANNEL                          | -60°                                    | -                                          | -                                          | DDR MODE                                   |

| 5A   | -                                                                                        | -                  | VCC                     | GND     | -              | 60°                                 | BOTH CHANNELS                                    | 180°                                    | -                                          | -                                          | 2-PHASE                                    |

| 5B   | -                                                                                        | -                  | VCC                     | GND     | -              | 60°                                 | BOTH CHANNELS                                    | 180°                                    | 5A                                         | 5A or 7A                                   | 6-PHASE                                    |

| 5C   | 1                                                                                        | -                  | VCC                     | GND     | -              | 60°                                 | BOTH CHANNELS                                    | 180°                                    | 5A                                         | 5A or 7A                                   | 3 OUTPUTs                                  |

| 5D   | -                                                                                        | -                  | VCC                     | GND     | -              | 60°                                 | BOTH CHANNELS                                    | 180°                                    | 5A                                         | 3 or 4                                     | 4 OUTPUTs                                  |

| 6    | -                                                                                        | -                  | VCC                     | VCC     | GND            | 120°                                | BOTH CHANNELS                                    | 240°                                    | 2B                                         | -                                          | 3-PHASE                                    |

| 7A   | -                                                                                        | -                  | VCC                     | VCC     | VCC            | 90°                                 | BOTH CHANNELS                                    | 180°                                    | 5A or 7A                                   | -                                          | 4-PHASE                                    |

| 7B   | 1                                                                                        | -                  | VCC                     | VCC     | VCC            | 90°                                 | BOTH CHANNELS                                    | 180°                                    | 5A or 7A                                   | -                                          | 2 OUTPUTs<br>(1st IC in Mode<br>7A)        |

| 7C   | -                                                                                        | -                  | VCC                     | VCC     | VCC            | 90°                                 | BOTH CHANNELS                                    | 180°                                    | 3, 4                                       | -                                          | 3 OUTPUTs<br>(1st IC in Mode<br>7A)        |

| 8    | 8 Cascaded IC Operation MODEs 5A+5A+7A+5A+5A+5A/7A, No External Clock Required           |                    |                         |         |                |                                     |                                                  | 12-PHASE                                |                                            |                                            |                                            |

| 9    |                                                                                          |                    |                         | Externa | al Clock o     | r External Logic C                  | ircuits Required for I                           | Equal Phase Inter                       | val                                        |                                            | 5, 7, 8, 9, 10,<br>11, or (PHASE<br>>12)   |

NOTE: "2ND CHANNEL WRT 1ST" is referred to as "channel 2 lag channel 1 by the degrees specified by the number in the corresponding table cells". For example, 90° with 2ND CHANNEL WRT 1ST means channel 2 lags channel 1 by 90°; -60° with 2ND CHANNEL WRT 1ST means channel 2 leads channel 1 by 60°.

#### 3-PHASE TIMING DIAGRAM (MODE 6)

FIGURE 3. SIMPLIFIED RELATIVE PHASES CONTROL

#### Functional Description

#### Initialization

Initially, the ISL8120IRZEC Power-On Reset (POR) circuits continually monitor the bias voltages (PVCC and VCC) and the voltage at EN pin. The POR function initiates soft-start operation 384 clock cycles after the EN pin voltage is pulled to be above 0.8V, all input supplies exceed their POR thresholds and the PLL locking time expires, as shown in Figure 4. The enable pin can be used as a voltage monitor and to set desired hysteresis with an internal 30µA sinking current going through an external resistor divider. The sinking current is disengaged after the system is enabled. This feature is especially designed for applications that require higher input rail POR for better undervoltage protection. For example, in 12V applications, R<sub>LIP</sub> = 53.6k and R<sub>DOWN</sub> = 5.23k will set the turn-on threshold (V<sub>FN RTH</sub>) to 10.6V and turn-off threshold (V<sub>EN FTH</sub>) to 9V, with 1.6V hysteresis (V<sub>EN HYS</sub>).

During shutdown or fault conditions, the soft-start is reset quickly while UGATE and LGATE changes states immediately (<100ns) upon the input drops below falling POR.

#### HIGH = ABOVE POR; LOW = BELOW POR

FIGURE 4. SOFT-START INITIALIZATION LOGIC

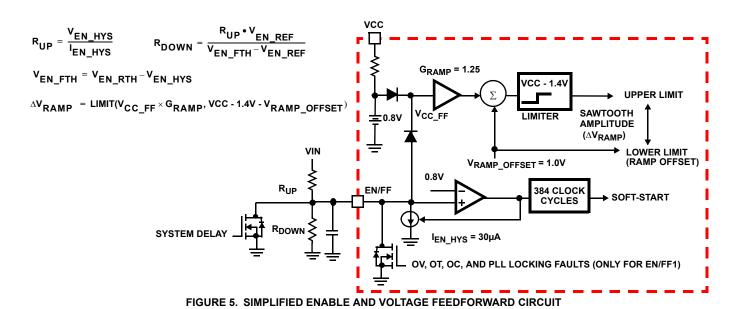

#### Voltage Feed-forward

Other than used as a voltage monitor described in previous section, the voltages applied to the EN/FF pins are also fed to adjust the amplitude of each channel's individual sawtooth. The amplitude of each channel's sawtooth is set to 1.25 times of the corresponding EN/FF voltage upon its enable (above 0.8V). This helps to maintain a constant gain ( $G_{\rm M} = VIN \cdot D_{\rm MAX}/\Delta V_{\rm RAMP}$ ) contributed by the modulator and the input voltage to achieve optimum loop response over a wide input voltage range. The sawtooth ramp offset voltage is 1V (equal to 0.8V\*1.25), and the peak of the sawtooth is limited to VCC - 1.4V. With VCC = 5.4V, the ramp has a maximum peak-to-peak amplitude of VCC - 2.4V (equal to 3V); So the feed-forward voltage effective range is typically 3x as the ramp amplitude ranges from 1V to 3V.

A 384 cycle delay is added after the system reaches its rising POR and prior to the soft-start. The RC timing at the EN/FF pin should be sufficiently small to ensure that the input bus reaches its static state and the internal ramp circuitry stabilizes before soft-start. A large RC could cause the internal ramp amplitude not to synchronize with the input bus voltage during output start-up or when recovering from faults. It is recommended to use open drain or open collector to gate this pin for any system delay, as shown in Figure 5.

The multiphase system can immediately turn off all ICs under fault conditions of one or more phases by pulling all EN/FF pins low. Thus, no bouncing occurs among channels at fault and no single phase could carry all current and be over stressed.

FIGURE 6. TYPICAL 4-PHASE WITH FAULT HANDSHAKE

While EN/FF is pulled to ground, a constant voltage (0.8V) is fed into the ramp generator to maintain a minimum peak-to-peak ramp.

Since the EN/FF pins are pulled down under fault conditions, the pull-up resistor ( $R_{UP}$ ) should be scaled to sink no more than 5mA current from EN/FF pin. Essentially, the EN/FF pins cannot be directly connected to VCC.

#### Soft-start

The ISL8120IRZEC has two independent digital pre-charged soft-start circuitry, which has a rise time inversely proportional to the switching frequency and is determined by an digital counter that increments with every pulse of the phase clock. Refer to Figure 7. The full soft-start time from 0V to 0.6V can be estimated by Equation 1.

$$t_{SS} = \frac{1280}{f_{SW}}$$

(EQ. 1)

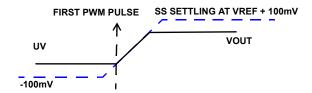

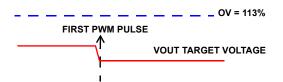

The ISL8120IRZEC has the ability to work under a pre-charged output (see Figure 8). The output voltage would not be yanked down during pre-charged start-up. If the pre-charged output voltage is greater than the final target level but prior to 113% setpoint, the switching will not start until the output voltage reduces to the target voltage and the first PWM pulse is generated (see Figure 9). The maximum allowable pre-charged level is 113%. If the pre-charged level is above 113% but below 120%, the output will hiccup between 113% (LGATE turns on) and 87% (LGATE turns off) while EN/FF is pulled low. If the pre-charged load voltage is above 120% of the targeted output voltage, then the controller will be latched off and not be able to power-up. See "PRE-POR Overvoltage Protection (PRE-POR-OVP)" on page 24 for details.

For above target pre-charged start-up, the output voltage would not change until the end of the soft-start. If the initial dip is below the UV level, the LGATE could be turned off. In such an event, the body-diode drop of the low-side FET will be sensed and could potentiality cause an OCP event for  $r_{\mbox{\footnotesize{DS(ON)}}}$  current sensing applications.

FIGURE 7. SOFT-START WITH VOUT = 0V

FIGURE 8. SOFT-START WITH VOUT = UV

FIGURE 9. SOFT-START WITH VOUT BELOW OV BUT ABOVE FINAL TARGET VOLTAGE

#### Power-Good

FIGURE 10. POWER-GOOD THRESHOLD WINDOW

FIGURE 11. FORCE LGATE HIGH LOGIC

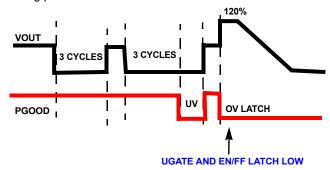

Both channels share the same PGOOD output. Either of the channels indicating out-of-regulation will pull-down the PGOOD pin. The Power-Good comparators monitor the voltage on the VMON pins. The trip points are shown in Figure 10. PGOOD will not be asserted until after the completion of the soft-start cycle of both channels. If Channels 1 or 2 are not used, the Power-Good can stay in operation by connecting 2 channels' VMON pins together. The PGOOD pulls low upon both EN/FF's disabling it if one of the VMON pins' voltage is out of the threshold window. PGOOD will not pull low until the fault presents for three consecutive clock cycles. In Dual/DDR application, if the turn-off channel pre-charges its VMON within the PGOOD threshold window, it could indicate Power-Good, however, the PGOOD signal can pull low with an external PNP or PMOS transistor via the EN/FF of the corresponding off channel.

#### **Undervoltage and Overvoltage Protection**

The Undervoltage (UV) and Overvoltage (OV) protection circuitry monitor the voltage on the VMON pins. The UV functionality is not enabled until the end of soft-start. An OV condition (>120%) during soft-start would latch IC off.

In an UV event, if the output drops below -13% (-9% is the hysteresis level) due to some reasons other than OV, OC, OT, and PLL faults (EN/FF is not pulled low) of the target level at the output voltage falling edge, the lower MOSFETs will turn off to avoid any negative voltage ringing.

An OV event ( $V_{OUT}$  > 120%) causes the high-side MOSFET to latch off permanently, while the low-side MOSFET turns on and then turns off after the output voltage drops below 87%. At the same time, the EN/FF and PGOOD are also latched low. The latch condition can be reset only by recycling VCC. In Dual/DDR mode, each channel is responsible for its own OV event with the corresponding VMON as the monitor. In multiphase mode, both channels respond simultaneously when either triggers an OV event.

To protect the overall power trains in case of only one channel of a multiphase system detecting OV, the low-side MOSFET always turns on at the conditions of EN/FF = LOW and the output voltage above 113% (all VMON pins and EN pins are tied together) and turns off after the output drops below 87%. Thus, in a high phase count application (Multiphase Mode), all cascaded ICs can latch off simultaneously via EN pins, and each IC shares the same sink current to reduce the stress and eliminate the bouncing among phases.

FIGURE 12. UV AND OV TIMING DIAGRAM

#### PRE-POR Overvoltage Protection (PRE-POR-OVP)

When both the VCC and PVCC are below PORs (not include EN POR), the UGATE is low and LGATE is floating (high impedance). EN/FF has no control on LGATE when below PORs. When above PORs, the LGATE would not be floating but toggling with its PWM pulses. An external  $10\Omega$  resistor, connected in between Phase and LGATE nodes, enables the PRE-POR-OVP circuit. The output of the converter that is equal to phase node voltage via output inductors is then effectively clamped to the low-side MOSFET's gate threshold voltage, which provides some protection to the microprocessor if the upper MOSFET(s) is shorted during start-up, shutdown, or normal operations. For complete protection, the low-side MOSFET should have a gate threshold that is much smaller than the maximum voltage rating of the load.

The PRE-POR-OVP works against pre-biased start-up when pre-charged output voltage is higher than the threshold of the low-side MOSFET, however, it can be disabled by placing a 2k resistor from LGATE to ground.

#### Over-Temperature Protection (OTP)

When the junction temperature of the IC is greater than +150°C (typically), both EN/FF pins pull low to inform other cascaded channels via their EN/FF pins. All connected EN/FFs stay low and release after the IC's junction temperature drops below +125°C (typically), with a +25°C hysteresis (typical).

#### **Current Loop**

When the ISL8120IRZEC operates in 2-phase mode, the current control loop keeps the channel's current in balance. After 175ns blanking period with respect to the falling edge of the PWM pulse of each channel, the voltage developed across the DCR of the inductor,  $r_{DS(ON)}$  of the low-side MOSFETs, or a precision resistor, is filtered and sampled for 175ns. The current ( $I_{CS1}/I_{CS2}$ ) is scaled by the  $R_{ISEN}$  resistor and provides feedback proportional to the average output current of each channel.

For DCR sensing, the ICS can be derived from Equation 2:

$$ICS = \frac{IL \bullet DCR}{RISEN}$$

(EQ. 2)

where IL is the inductor DC current, and DCR is its DC resistance.

For low-side MOSFET  $r_{DS(ON)}$  sensing, the ICS can be derived from Equation 3:

$$ICS = \frac{IL \cdot r_{DS(ON)}}{RISEN}$$

(EQ. 3)

In multiphase mode (VSEN2- pulled high), the scaled output currents from both active channels are combined to create an average current reference (I<sub>AVG</sub>) which represents average current of both channel outputs as calculated in Equation 4.

$$IAVG = \frac{ICS1 + ICS2}{2}$$

(EQ. 4)

FIGURE 13. SIMPLIFIED CURRENT SAMPLING AND OVERCURRENT PROTECTION

The signal  $I_{AVG}$  is then subtracted from the individual channel's scaled current ( $I_{CS1}$  or  $I_{CS2}$ ) to produce a current correction signal for each channel. The current correction signal keeps each channel's output current contribution balanced relative to the other active channel.

For multiphase operation, the share bus ( $V_{ISHARE}$ ) represents the average current of all active channels and compares with each IC's average current ( $I_{AVG\_CS}$  equals to  $I_{AVG}$  or  $I_{CS1}$  depending upon the configuration, represented by  $V_{ISET}$ ) to generate current share error signal ( $I_{CS\_ERR}$ ) for each individual channel. Each current correction signal is then subtracted from the error amplifier output and fed to the individual channel PWM circuits.

When both channels operate independently, the average function is disabled and generates zero average current ( $I_{AVG} = 0$ ), and current correction block of Channel 2 is also disabled. The  $I_{AVG\_CS}$  is the Channel 1 current  $I_{CS1}$ . The channel 1 makes any necessary current correction by comparing its channel current (represented by  $V_{ISET}$ ) with the share bus ( $V_{ISHARE}$ ). When the share bus does not connect to other ICs, the ISET and ISHARE pins can be shorted together and grounded via a single resistor to ensure zero share error.

Note that the common mode input voltage range of the current sense amplifiers is VCC - 1.8V. Therefore, the  $r_{DS(ON)}$  sensing should be used for applications with output voltage greater than VCC - 1.8V. For example, application of 3.3V output is suggested to use  $r_{DS(ON)}$  sensing.

In addition, the R-C network components (for DCR sensing) are selected such that the RC time constant matches the inductor L/DCR time constant. Otherwise, it could cause undershoot/overshoot during load transient and start-up. C is

typically set to  $0.1\mu F$  or higher, while R is calculated with Equation 5.

$$R = \frac{L}{C \bullet DCR}$$

(EQ. 5)

Figure 13 shows a simple and flexible configuration for both  $r_{DS(ON)}$  and DCR sensing.

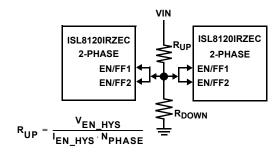

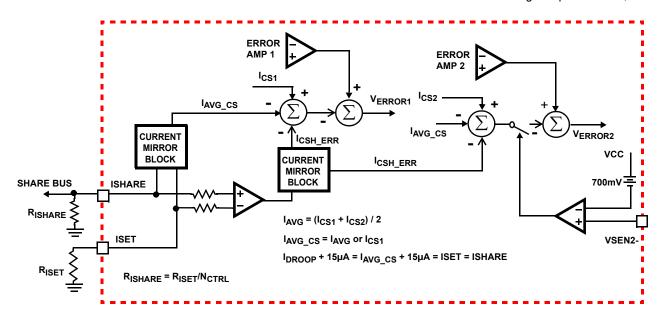

#### Current Share Control in Multiphase Single Output

The  $I_{AVG}$  CS is the average current of both channels ( $I_{AVG}$ 2-phase mode) or only Channel 1 (I<sub>CS1</sub> any other modes). ISHARE and ISET pins source a copy of  $I_{AVG}$  CS with 15 $\mu A$ offset, for example, the full-scale will be 120µA. If one single external resistor is used as RISHARE connecting the ISHARE bus to ground for all the ICs in parallel, RISHARE should be set equal to R<sub>ISET</sub>/N<sub>CTRL</sub> (where N<sub>CNTL</sub> is the number of the ISL8120IRZEC controllers in parallel or multiphase operations), and the share bus voltage (VISHARE) set by the RISHARE represents the average current of all active channels. Another way to set RISHARE is to put one resistor in each IC's ISHARE pin and use the same value with RISET (RISHARE = RISET), in which case the total equivalent resistance value is also R<sub>ISET</sub>/N<sub>CTRL</sub>. The voltage (V<sub>ISET</sub>) set by R<sub>ISET</sub> represents the average current of the corresponding device and compared with the share bus (V<sub>ISHARE</sub>). The current share error signal (I<sub>CSH FRR</sub>) is then fed into the current correction block to adjust each channel's PWM pulse accordingly.

The current share function provides at least 10% overall accuracy between ICs, 5% within the IC when using a 1% resistor to sense a 10mV signal. The current share bus works for up to 12-phase.

For multiphase implementation, one single error amplifier should be used for the voltage loop. Therefore, all other

FIGURE 14. SIMPLIFIED CURRENT SHARE AND INTERNAL BALANCE IMPLEMENTATION

channels' error amplifiers should be disabled with their corresponding VSEN- pulled to VCC, as shown in Figure 15.

#### Current Share Control Loop in Multi-Module with Independent Voltage Loop

The power module controlled by ISL8120IRZEC with its own voltage loop can be paralleled to supply one common output load with its integrated Master-Slave current sharing control, as shown in "Typical Application VIII (Multiple Power Modules in Parallel with Current Sharing Control)" on page 12. A resistor R<sub>CSR</sub> needs to be inserted between VSEN1- pin and the lower resistor of the voltage sense resistor divider for each module. With this resistor, the correction current sourcing from VSEN1- pin will create a voltage offset to maintain even current sharing among modules. The recommended value for the VSEN1- resistor  $R_{CSR}$  is 100 $\Omega$  and it should not be large in order to keep the unity gain amplifier input pin impedance compatibility. The maximum source current from VSEN1- pin is 350µA, which is combined with R<sub>CSR</sub> to determine the current sharing regulation range. The generated correction voltage on R<sub>CSR</sub> is suggested to be within 5% of VREF (0.6V) to avoid fault trigging of UV/OV and PGOOD during dynamic events.

To attain good current balance in system start up preventing single module from overcurrent, the paralleled modules are recommended to be synchronized and the enable pins (EN/FF) should be tied together to initial start-up at the same instant.

#### **Overcurrent Protection**

The OCP function is enabled at start-up. When both channels operate independently, the average function is disabled and generates zero average current ( $I_{AVG} = 0$ ). The Channel 2 current ( $I_{CS2}$ ) is compared with  $I_{TRIP}$  (105µA) and has its own independent overcurrent protection; while the 7 clock cycles delay is bypassed. The Channel 1's current ( $I_{CS1}$ ) plus 15µA offset forms a voltage ( $V_{ISHARE}$ ) with an external resistor  $R_{ISHARE}$  and compares with a

precision 1.2V threshold (±1%, 50mV hysteresis); while the 105μA OCP comparator with 7-cycle delay is also activated.

In multiphase operation, the  $V_{ISHARE}$  represents the average current of all active channels and compares with a precision 1.2V threshold (±1%, 50mV hysteresis) to determine the overcurrent condition, while each channel has additional overcurrent trip point at 105 $\mu$ A with 7-cycle delay. This scheme helps protect against loss of channel(s) in multi-phase mode so that no single channel could carry more than 105 $\mu$ A in such event. See Figure 13. Note that it is not necessary for the R<sub>ISHARE</sub> to be scaled to trip at the same level as the 105 $\mu$ A OCP comparator if the application allows. For instance, when Channel 1 operates independently, the OC trip set by 1.2V comparator can be lower than 105 $\mu$ A trip point as shown in Equation 6.

$$R_{ISEN1} = \frac{\left(\frac{I_{OC}}{N} + \frac{V_{OUT}}{L} \cdot \left(\frac{1-D}{2F_{SW}} - t_{MIN\_OFF}\right)\right) \cdot DCR}{I_{TRIP}}$$

$$R_{ISHARE} = \frac{1V}{I_{TRIP}}$$

$$R_{ISET} = R_{ISHARE} \cdot N_{CNTL}$$

(EQ. 6)

where N is the number of phases; NCNTL is the number of the ISL8120IRZEC controllers in parallel or multiphase operations;  $I_{TRIP}$  = 105µA; IOC is the load overcurrent trip point;  $t_{MIN\_OFF}$  is the minimum Ugate turn off time that is 350ns;  $R_{ISHARE}$  in Equation 6 represents the total equivalent resistance in ISHARE pin bus of all ICs in multiphase or module parallel operation.

The overcurrent trip current source is trimmed to 105 $\mu$ A  $\pm$ 10% for both channels, while the overcurrent threshold (represented by V<sub>ISHARE</sub>) for multiphase operation (or Channel 1 depending upon configuration) is a precision 1.2V  $\pm$ 1% with 50mV hysteresis.

For the R<sub>ISEN</sub> chosen for OCP setting, the final value is usually higher than the number calculated from Equation 6.

$R_{\rm ISHARE\_}$  =  $R_{\rm ISET\_}$  FIGURE 15. SIMPLIFIED 6-PHASE SINGLE OUTPUT IMPLEMENTATION

The reason of which is practical especially for low DCR applications the PCB and inductor pad soldering resistance would have large effects in total impedance affecting the DCR voltage to be sensed.

When OCP is triggered, the controller pulls EN/FF low immediately to turn off UGATE and LGATE. However, if the output overshoot is greater than 113% at EN/FF = LOW, LGATE turns ON until the output voltage drops below 87%.