### **AUTOMATION**

User manual

**IBS SUPI 3 UM E**

Order No.: —

INTERBUS protocol chip IBS SUPI 3

### **AUTOMATION**

# User manual INTERBUS protocol chip IBS SUPI 3

2010-12-09

Designation: IBS SUPI 3 UM E

Revision: 03

Order No.: —

This user manual is valid for:

Designation Order No. IBS SUPI 3 QFP 2746087 IBS CHIP-Muster/... 2746951

## Please observe the following notes

In order to ensure the safe use of the product described, you have to read and understand this manual. The following notes provide information on how to use this manual.

### User group of this manual

The use of products described in this manual is oriented exclusively to qualified electricians or persons instructed by them, who are familiar with applicable standards and other regulations regarding electrical engineering and, in particular, the relevant safety concepts.

Phoenix Contact accepts no liability for erroneous handling or damage to products from Phoenix Contact or third-party products resulting from disregard of information contained in this manual.

### Explanation of symbols used and signal words

This is the safety alert symbol. It is used to alert you to potential personal injury hazards. Obey all safety messages that follow this symbol to avoid possible injury or death.

### **DANGER**

This indicates a hazardous situation which, if not avoided, will result in death or serious injury.

#### **WARNING**

This indicates a hazardous situation which, if not avoided, could result in death or serious injury.

### **CAUTION**

This indicates a hazardous situation which, if not avoided, could result in minor or moderate injury.

The following types of messages provide information about possible property damage and general information concerning proper operation and ease-of-use.

#### NOTE

This symbol and the accompanying text alerts the reader to a situation which may cause damage or malfunction to the device, either hardware or software, or surrounding property.

This symbol and the accompanying text provides additional information to the reader. It is also used as a reference to other sources of information (manuals, data sheets, literature) on the subject matter, product, etc.

PHOENIX CONTACT 6025\_en\_03

#### General terms and conditions of use for technical documentation

Phoenix Contact reserves the right to alter, correct, and/or improve the technical documentation and the products described in the technical documentation at its own discretion and without giving prior notice, insofar as this is reasonable for the user. The same applies to any technical changes that serve the purpose of technical progress.

The receipt of technical documentation (in particular data sheets, installation instructions, manuals, etc.) does not constitute any further duty on the part of Phoenix Contact to furnish information on alterations to products and/or technical documentation. Any other agreement shall only apply if expressly confirmed in writing by Phoenix Contact. Please note that the supplied documentation is product-specific documentation only and that you are responsible for checking the suitability and intended use of the products in your specific application, in particular with regard to observing the applicable standards and regulations. Although Phoenix Contact makes every effort to ensure that the information content is accurate, up-to-date, and state-of-the-art, technical inaccuracies and/or printing errors in the information cannot be ruled out. Phoenix Contact does not offer any guarantees as to the reliability, accuracy or completeness of the information. All information made available in the technical data is supplied without any accompanying guarantee, whether expressly mentioned, implied or tacitly assumed. This information does not include any guarantees regarding quality, does not describe any fair marketable quality, and does not make any claims as to quality guarantees or guarantees regarding the suitability for a special purpose.

Phoenix Contact accepts no liability or responsibility for errors or omissions in the content of the technical documentation (in particular data sheets, installation instructions, manuals, etc.).

The aforementioned limitations of liability and exemptions from liability do not apply, in so far as liability must be assumed, e.g., according to product liability law, in cases of premeditation, gross negligence, on account of loss of life, physical injury or damage to health or on account of the violation of important contractual obligations. Claims for damages for the violation of important contractual obligations are, however, limited to contract-typical, predictable damages, provided there is no premeditation or gross negligence, or that liability is assumed on account of loss of life, physical injury or damage to health. This ruling does not imply a change in the burden of proof to the detriment of the user.

### Statement of legal authority

This manual, including all illustrations contained herein, is copyright protected. Use of this manual by any third party is forbidden. Reproduction, translation, and public disclosure, as well as electronic and photographic archiving or alteration requires the express written consent of Phoenix Contact. Violators are liable for damages.

Phoenix Contact reserves all rights in the case of patent award or listing of a registered design. Third-party products are always named without reference to patent rights. The existence of such rights shall not be excluded.

#### How to contact us

Internet

Up-to-date information on Phoenix Contact products and our Terms and Conditions can be found on the Internet at:

www.phoenixcontact.com.

Make sure you always use the latest documentation.

It can be downloaded at:

www.phoenixcontact.net/catalog.

**Subsidiaries**

If there are any problems that cannot be solved using the documentation, please contact your Phoenix Contact subsidiary.

PHOENIX CONTACT

Subsidiary contact information is available at www.phoenixcontact.com.

Published by

PHOENIX CONTACT GmbH & Co. KG

Flachsmarktstraße 8 P.O. Box 4100

32825 Blomberg Harrisburg, PA 17111-0100 Germany USA

Phone +49 - (0) 52 35 - 3-00 Phone +1-717-944-1300

Fax +49 - (0) 52 35 - 3-4 12 00

Should you have any suggestions or recommendations for improvement of the contents and layout of our manuals, please send your comments to

tecdoc@phoenixcontact.com.

PHOENIX CONTACT 6025\_en\_03

# Table of contents

| 1 | Structure and basic v | wiring |                                                               | 1-1         |

|---|-----------------------|--------|---------------------------------------------------------------|-------------|

|   |                       | 1.1    | Introduction                                                  | 1-2         |

|   |                       | 1.2    | Basic structure                                               | 1-3         |

|   |                       |        | 1.2.1 New features of the IBS SUPI 3 chip                     | 1-5         |

|   |                       |        | 1.2.2 Field of application                                    | 1-8         |

|   |                       | 1.3    | Housing type                                                  | 1-8         |

|   |                       |        | 1.3.1 QFP 100 pin table                                       |             |

|   |                       |        | 1.3.2 QFP 100 (Quad Flat Pack)                                |             |

|   |                       |        | 1.3.3 Signal description                                      |             |

|   |                       | 1.4    | Basic wiring                                                  |             |

|   |                       |        | 1.4.1 Clock, initialization                                   |             |

|   |                       |        | 1.4.2 Configuration options                                   | 1-18        |

| 2 | INTERBUS interface    | s      |                                                               | 2-1         |

|   |                       | 2.1    | Overview                                                      |             |

|   |                       | 2.2    | Local bus interface 8-wire protocol                           | 2-1         |

|   |                       | 2.3    | Remote bus connection                                         | 2-3         |

| 3 | Application interface |        |                                                               | 3-1         |

|   |                       | 3.1    | Overview                                                      | 3-1         |

|   |                       | 3.2    | Bus terminal module mode                                      | 3-1         |

|   |                       | 3.3    | Input/output mode                                             | 3-4         |

|   |                       | 3.4    | μP (microprocessor) access mode                               | 3-7         |

|   |                       |        | 3.4.1 Synchronization options                                 | 3-15        |

|   |                       |        | 3.4.2 SET-I register                                          |             |

|   |                       |        | 3.4.3 SET-II register                                         |             |

|   |                       |        | 3.4.4 ID code register                                        |             |

|   |                       |        | 3.4.5 IB state register                                       |             |

|   |                       |        | 3.4.7 Processor alarm register and processor command register |             |

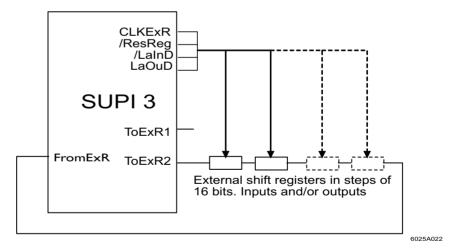

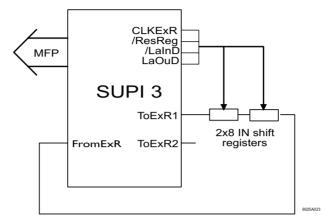

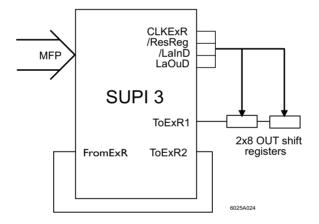

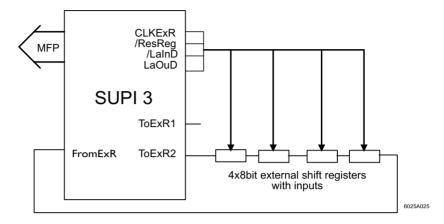

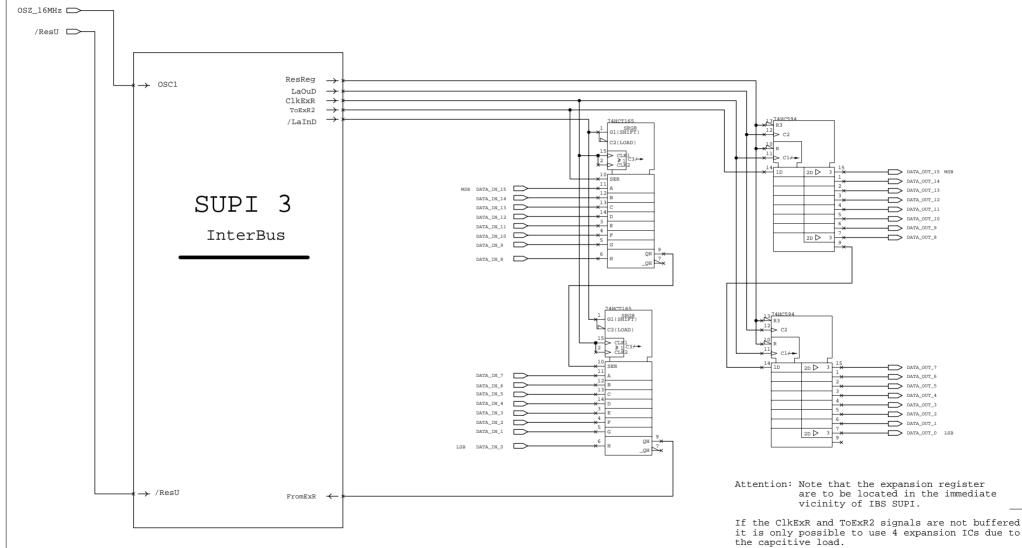

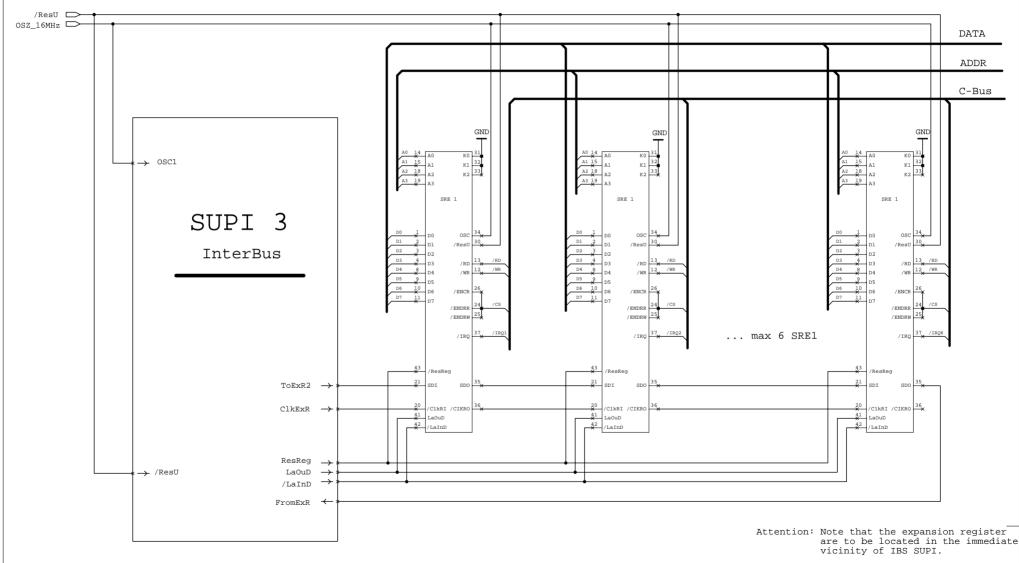

|   |                       | 3.5    | Register expansion                                            |             |

|   |                       | 0.5    | 3.5.1 Examples                                                |             |

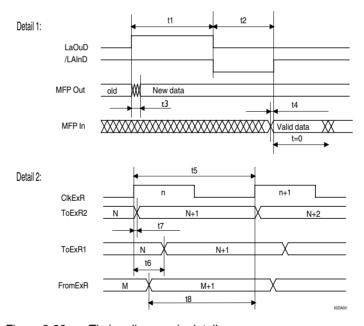

|   |                       |        | 3.5.2 Register expansion interface timing                     |             |

|   |                       | 3.6    | Diagnostic inputs and outputs                                 |             |

| Α | Technical data        |        |                                                               | Δ-1         |

| ^ | r commodi data        | A 1    | General notes about processing                                |             |

|   |                       |        | A 1.1 Storage                                                 |             |

|   |                       |        | A 1.2 Processing time                                         |             |

|   |                       |        | A 1.3 Soldering                                               | <b>A-</b> 3 |

|   |                       | A 2    | ID code specification (extract)                               | A-4         |

|   |                       | А3     | Length code specification                                     | A-7         |

|   |                       |        |                                                               |             |

i

### **IBS SUPI 3**

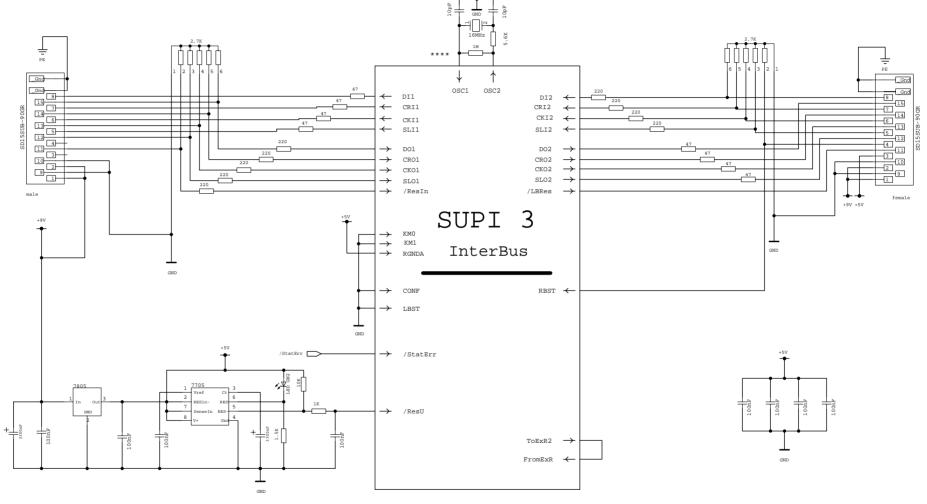

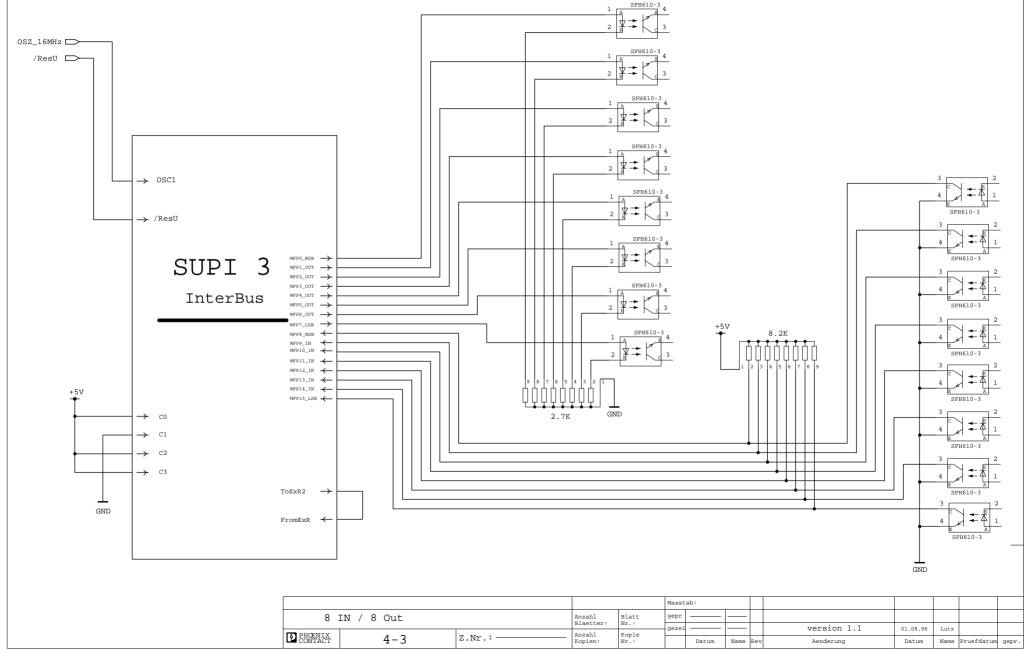

| В | Wiring examples |                 | B-1 |

|---|-----------------|-----------------|-----|

| С | Appendix        |                 | C-1 |

|   | C 1             | List of figures | C-1 |

|   | C 2             | List of tables  | C-3 |

|   | C3              | Index           | C-5 |

# 1 Structure and basic wiring

The IBS SUPI 3 (Serial Universal Protocol Interface) chip represents a new generation of INTERBUS slave protocol chips and an easy interface to INTERBUS. The integrated diagnostic and error management is a novelty in the chip; it allows an exact determination of error location and cause in a system and also reduces external circuitry.

On the basis of this description you may implement your own INTERBUS devices within a very short time. With the end user in mind, subject the devices to the INTERBUS conformance test.

In addition to this document you will find the INTERBUS Club guideline "Conformity Test and Certification" as a reference work on the Internet at www.interbusclub.com.

Current hardware and software information for the device manufacturer as well as further product documents from Phoenix Contact can be found on the Internet at <a href="https://www.phoenixcontact.net/catalog">www.phoenixcontact.net/catalog</a>.

### Application areas of the INTERBUS slave protocol chip

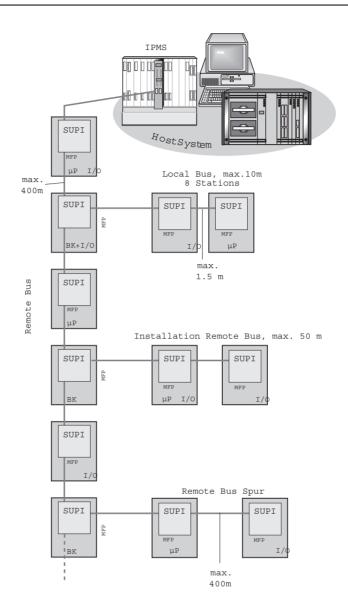

Figure 1-1 Fields of application of the INTERBUS SUPI 3 slave protocol chip

### 1.1 Introduction

The IBS SUPI 3 chip is an ASIC in 0.5  $\mu$ m CMOS technology. It represents the third generation of INTERBUS slave protocol chips and is pin- and function-compatible to the previous SUPI 2 chip. Every INTERBUS master operates together with the SUPI 3 chip. The IBS PC AT-T PC interface board supports the SUPI 3 chip by driver version 3.1 or later.

1-2 PHOENIX CONTACT 6025\_en\_03

Currently, the SUPI 3 is available in one housing type (QFP 100).

Table 1-1 Different versions

| Housing | Order designation | Order No. |

|---------|-------------------|-----------|

| QFP 100 | IBS SUPI 3 QFP    | 2746087   |

| QFP 100 | IBS CHIP-Muster/  | 2746951   |

### 1.2 Basic structure

The SUPI 3 is the third generation of INTERBUS slave protocol chips. It is pin- and function-compatible with the previous SUPI 1 and 2 chip versions. Its most important new feature is its central diagnostics and report manager being part of the new INTERBUS diagnostic concept.

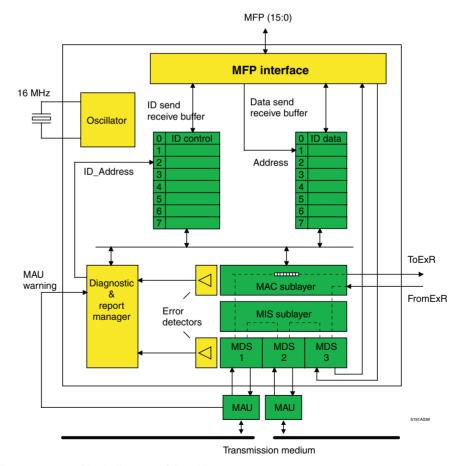

The INTERBUS SUPI 3 protocol chip resulted from a VHDL model and has a complexity of about 15000 gate equivalents. The following block diagram shows the structure of the circuit.

Figure 1-2 Block diagram of the chip

The protocol stack in the middle comprises layer 1 and layer 2 of the ISO/OSI reference model. Data is provided to the MDS (Medium Dependent Sublayer) from an external MAU (Medium Attachment Unit) e.g., RS-485 or fiber-optic access. In this layer, scanning, line decoding and encoding are carried out and time conditions are defined. The SUPI 3 chip has three channels in the MDS for one incoming and two outgoing interfaces.

The MIS (Medium Independent Sublayer) forms the upper edge of layer 1, i.e., the physical layer. It is intended for routing the three MDS channels and for connecting layer 2.

Its lower edge represents the medium access control (MAC). This layer performs the ring access as well as the data security. The MAC sublayer serves the 8-byte transmit and receive buffers for INTERBUS data as well as the 16-byte transmit and receive buffers for the identification transmission cycle. The application and higher protocol layers have access to these buffers via the 16-bit **Multi-Functions Pin interface** (MFP interface). The MFP interface can be set according to the interface implementation requirements via four configuration pins as an I/O port or as a microprocessor interface of a CPU environment. The MFP interface contains an interrupt controller with the necessary write and read registers as well as parameterization and state registers for CPU applications. These registers allow to configure the chip and to visualize certain protocol events.

Data of the transmit and receive buffers is taken from the MAC sublayer, encoded correspondingly and sent to the suitable MDS channel via the MDS sublayer. After the line encoding, data is sent to the medium via the external MAU.

Compared to previous chips, the central diagnostics and report manager as well as the error detectors which are able to read certain error patterns at all MDS channels and the MAC sublayer, are important new features of the SUPI 3 chip. This block distinguishes between events with high or low priority. Events of low priority, also called report events are, for example, the MAU warnings in the block diagram. These warnings are provided by the MAU and indicate an impairment of the transmission quality. This means that not only faults, but also creeping impairment in quality is detected and signaled at a very early stage.

Diagnostic events with high priority are error sources which cause interference in the transmission cycle. The diagnostics and report manager ensures both generation and non-time-critical transmission of error patterns. The error patterns are stored in the ID send buffer and transmitted from the MAC sublayer to the bus master.

If an error exceeds the permissible data update time of the bus system but is too short for a central check of all devices by the master, the on-chip diagnostics shows its performance. The diagnostics manager stores all detected errors on the transmission medium as well as breakdowns of the voltage supply as error patterns in the chip until it has been read and acknowledged by the bus master. This procedure allows a unique assignment of sporadic errors, which in general are difficult to identify, to the error location.

**1-4** PHOENIX CONTACT **6025\_en\_03**

### 1.2.1 New features of the IBS SUPI 3 chip

Although the diagnostics described above is an important feature, it is less important to developers of INTERBUS devices when designing the circuit. The efforts are reduced because functions are implemented in the SUPI 2 chip by additional hardware.

For example, the voltage monitoring of all electrically isolated areas is no longer necessary because the MDS sublayers offer a better evaluation. This reduces hardware expense considerably. The power-up reset circuitry of the SUPI 3 chip has also been optimized.

For a better detection of errors caused by the transmission medium (e.g. loose contacts or failure of a differential signal line of the RS-485 interface), this state must be mapped to a high level at the data input. This means for the RS-485 interface to force a logic "1" on the receive data line in the event of an error. The line decoders in the MDS sublayer interpret this as an idle message. Since idle messages defined in the protocol have a logic "0" encoding, a distinction is possible using MAU fail timers. If the MAU fail timer recognizes this "1" state for a set time, this is indicated as a MAU error to the diagnostics manager. The "MAU warning" function can detect, for example, the impairment of optical components caused by aging or an increasing pollution of lenses in the data light barriers before it comes to a complete failure. For this, the output of a trigger must be led to the new "MAU warning" inputs of the SUPI 3 chip.

For a better support of software flexibility on the slaves, the module identification code (ID code) can now be loaded to the SUPI 3 chip. Like the length code in the SET-I register, this code is protected from accidental writing by an automatic latching mechanism.

This mechanism and applying the " $\mu$ P\_not\_Ready" ID code to the physical pins of the SUPI 3 allows reconfiguration of the protocol chip by intelligent modules even after the bus master has initialized the INTERBUS system. This means when the INTERBUS master has detected a device with the " $\mu$ P\_not\_Ready" ID code in the INTERBUS system, it waits for the final configuration. Therefore, the same hardware can be used for very different applications.

Two message registers which realize a management channel to the INTERBUS master, are another new feature. The user has no direct access to the channel. It is an option for future applications. A new function has been implemented in the SET-II register. By setting bit 5, a  $\mu$ P watchdog input is activated. Register 14, which was previously not available is used to enable additional interrupts. In this way an interrupt can be generated when the master writes a processor alarm register or when the layer 2 watchdog has elapsed. The new register 15 stores test functions for an engineering test during the development of the chip. These functions are not important for the user.

### Summary of the new IBS SUPI 3 chip features:

- With its diagnostic features, the diagnostic and report manager is the heart of the SUPI extensions. It stores error localization information for the bus master.

- The new SUPI 3 functions are supported by controller boards as of Generation 4 only (firmware 4.0 or later).

- The pad dimensions of the QFP 100 housing were modified so that chip requires less space.

# Improvements compared to SUPI 2

Filtering of the quasi-static inputs:

RBST, LBST : 270 ms

CONF : 35 ms

/StatErr : 270 ms (standard) / 2.5 µs (µP watchdog)

/ResIN : 520 μs

These signals also had Schmitt trigger input circuits.

- Increase of driver capability of the outputs /ResReg, ClkExR, BA, RD, LD/TR, Error from 2 mA to 12 mA.

- Watchdog for "bus active" is now reset for every valid ID or data cycle.

- Start bit recognition: A spike (pulse <100 ns) in the critical range is recognized as a start bit error.

#### **Additional functions**

- Manufacturer/mask identification. Hardware version can be detected by the master.

Information is mapped to the INFO register of the ID send buffer.

- Layer 2 timeout monitoring: If LaOuD is not sent within a preset time, process OUT data is reset and /ResReg activated, provided that the master has enabled the function.

- $\,\mu P$ , ID code register: Now, the entire ID code (ID0-ID12) can be set by a microprocessor.

- "μP\_not\_Ready" ID code: If ID0 to ID7 = 38<sub>hex</sub> (remote bus device) or ID0 to ID7 = 78<sub>hex</sub> (local bus device) is set, new functions are active internally.

- /StatErr can additionally be used to indicate activation of an external processor watchdog.

- Processor command and alarm registers on address 9 form a management channel to the master (currently still reserved).

- On-chip diagnostics: The master activates on-chip diagnostics on the devices during

the bus system detection. All devices capable of diagnostics exchange their operation

ID registers and diagnostic ID registers. The master thus recognizes all devices able for

diagnostics. If errors should occur, they are stored in the diagnostic register. The

following diagnostic elements are implemented in the line decoder (forward, return,

branch):

- Power-up reset detection

- MAU fail (wire interrupt, wire short-circuit).

- CRC (Cyclic Redundancy Check)

- Stop bit error detection

- Validity check of the check sequence

- RBST, LBST change detection

- MAU warnings (impairment of the transmission quality).

- Eight alternative ID registers are addressed by a control word of the controller board and transmitted in the next ID cycle.

1-6 PHOENIX CONTACT 6025\_en\_03

- The following registers can be selected:

- 0 Standard register

- 1 First diagnostic bit register

- 2 Second diagnostic Register

- 3 Alarm bit register

- 4 Processor alarm register

- 5 Reserved

- 6 Reserved

- 7 Manufacturer/mask identification

The standard ID register is the default setting.

### 1.2.2 Field of application

The SUPI 3 has been designed for industrial applications.

Table 1-2 General data

|                | Quantity            |     |     |    |  |  |

|----------------|---------------------|-----|-----|----|--|--|

| Value          | Min. Type Max. Unit |     |     |    |  |  |

| Supply voltage | 4.5                 | 5.0 | 5.5 | V  |  |  |

| Temperature    | -40                 | +25 | +85 | °C |  |  |

### 1.3 Housing type

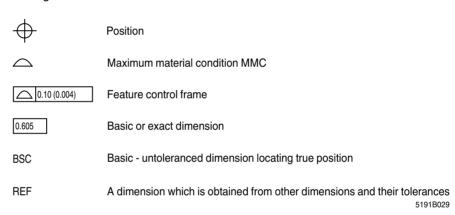

The following list explains general symbols and text that will be used in the drawing of the housing.

1-8 PHOENIX CONTACT 6025\_en\_03

### 1.3.1 QFP 100 pin table

Table 1-3 QFP 100 pin table

| Pin No. | Pin Name     | Pin No. | Pin Name       | Pin No. | Pin Name |

|---------|--------------|---------|----------------|---------|----------|

| 1       | RBST         | 36      | MFP10          | 70      | ID0      |

| 2       | KM0          | 37      | MFP9           | 71      | SLI1     |

| 3       | n.c.         | 38      | MFP8           | 72      | RGNDA    |

| 4       | KM1          | 39      | n.c.           | 73      | /StatErr |

| 5       | n.c.         | 40      | $V_{DD}$       | 74      | n.c.     |

| 6       | CKO2         | 41      | $V_{SS}$       | 75      | CRI1     |

| 7       | n.c.         | 42      | MFP7           | 76      | n.c.     |

| 8       | FromExR      | 43      | $V_{SS}$       | 77      | CONF     |

| 9       | DO2          | 44      | MFP6           | 78      | n.c.     |

| 10      | LBST         | 45      | MFP5           | 79      | BA       |

| 11      | C0           | 46      | MFP4           | 80      | LBDA/TR  |

| 12      | C1           | 47      | MFP3           | 81      | Error    |

| 13      | C2           | 48      | MFP2           | 82      | DI1      |

| 14      | CKO1         | 49      | MFP1           | 83      | С3       |

| 15      | DO1          | 50      | n.c.           | 84      | /LBRes   |

| 16      | CRO1 / MAUWR | 51      | MFP0           | 85      | /ModAck  |

| 17      | SLO1 / MAUWH | 52      | /ResIn / MAUWS | 86      | RBDA     |

| 18      | $V_{SS}$     | 53      | ID12           | 87      | $V_{SS}$ |

| 19      | $V_{DD}$     | 54      | n.c.           | 88      | CKI1     |

| 20      | OSC1         | 55      | ID11           | 89      | $V_{DD}$ |

| 21      | OSC2         | 56      | n.c.           | 90      | n.c.     |

| 22      | /ResU        | 57      | ID10           | 91      | $V_{SS}$ |

| 23      | DI2          | 58      | ID9            | 92      | SLO2     |

| 24      | n.c.         | 59      | ID8            | 93      | LaOuC    |

| 25      | CRI2         | 60      | ID7            | 94      | /LaInD   |

| 26      | n.c.         | 61      | n.c.           | 95      | LaOuD    |

| 27      | SLI2         | 62      | ID6            | 96      | /ClkExR  |

| 28      | CKI2         | 63      | ID5            | 97      | CRO2     |

| 29      | MFP15        | 64      | $V_{DD}$       | 98      | /ResReg  |

| 30      | n.c.         | 65      | ID4            | 99      | ToExR2   |

Table 1-3 QFP 100 pin table (continued)

| Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|

| 31      | MFP14    | 66      | $V_{SS}$ | 100     | ToExR1   |

| 32      | MFP13    | 67      | ID3      |         |          |

| 33      | n.c.     | 68      | ID2      |         |          |

| 34      | MFP12    | 69      | ID1      |         |          |

| 35      | MFP11    |         |          |         |          |

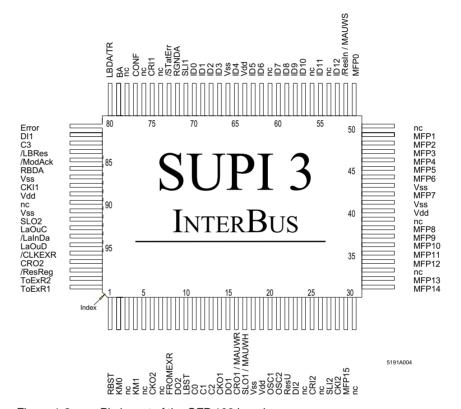

Figure 1-3 Pin layout of the QFP 100 housing

**1-10** PHOENIX CONTACT 6025\_en\_03

### 1.3.2 QFP 100 (Quad Flat Pack)

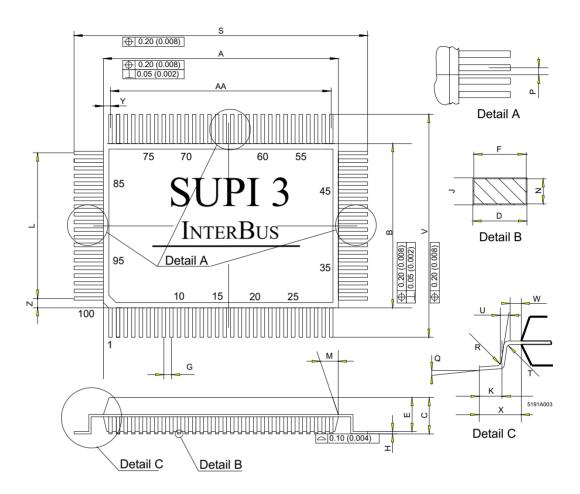

Figure 1-4 Mechanical dimensions of the QFP 100 housing (original dimension: millimeters)

Table 1-4 Mechanical dimensions of the QFP 100 housing

|     | Millim | neters | Inc   | hes   |     | Millimeters |       | ers Inches |       |

|-----|--------|--------|-------|-------|-----|-------------|-------|------------|-------|

| DIM | Min.   | Max.   | Min.  | Max.  | DIM | Min.        | Max.  | Min.       | Max.  |

| Α   | 19.90  | 20.10  | 0.783 | 0.791 | Р   | 0.325       | BSC   | 0.013      | BSC   |

| В   | 13.90  | 14.10  | 0.547 | 0.555 | Q   | 0°          | 7°    | 0°         | 7°    |

| С   | 2.80   | 3.40   | 0.110 | 0.134 | R   | 0.25        | 0.35  | 0.010      | 0.014 |

| D   | 0.22   | 0.38   | 0.009 | 0.015 | S   | 22.95       | 23.45 | 0.904      | 0.923 |

| Е   | 2.55   | 3.05   | 0.100 | 0.120 | Т   | 0.13        | -     | 0.005      | -     |

| F   | 0.22   | 0.33   | 0.009 | 0.013 | U   | 0°          | -     | 0°         | -     |

| G   | 0.65   | BSC    | 0.026 | BSC   | ٧   | 16.95       | 17.45 | 0.667      | 0.687 |

| Н   | 0.25   | -      | 0.010 | _     | W   | 0.40        | -     | 0.016      | -     |

| J   | 0,11   | 0,23   | 0.004 | 0.009 | Х   | 1.60        | REF   | 0.063      | REF   |

| K   | 0.73   | 1.03   | 0.028 | 0.040 | Υ   | 0.58        | REF   | 0.023      | REF   |

| L   | 12.35  | REF    | 0.486 | REF   | Z   | 0.83        | REF   | 0.033      | REF   |

| М   | 5°     | 16°    | 5°    | 16°   | AA  | 18.85       | REF   | 0.742      | REF   |

| N   | 0.11   | 0.17   | 0.004 | 0.007 |     |             |       |            |       |

1-12 PHOENIX CONTACT 6025\_en\_03

# 1.3.3 Signal description

Table 1-5 Signal description

| Designation                        | Meaning                                                                                                                                      | Туре                   |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| OSC1<br>OSC2                       | Oscillator input<br>Oscillator output                                                                                                        | OSC<br>OSC             |

| C3<br>C2<br>C1<br>C0               | Configuration inputs for the MFP interface**                                                                                                 | Clp<br>Cl<br>Cl        |

| KM1<br>KM0<br>RGNDA                | Configuration inputs for the INTERBUS interface**                                                                                            | CI                     |

| ID12-ID0                           | Identification code setting data length entry**                                                                                              | CI                     |

| MFP15-MFP0                         | Multi-function pins                                                                                                                          | BDp                    |

| SLxx                               | Control line ID/data cycle                                                                                                                   |                        |

| SLO1/MAUWH<br>SLO2<br>SLI1<br>SLI2 | Select line IN forward path/MAU warning forward path* Select line OUT forward path Select line OUT return path Select line IN return path    | ST<br>B12<br>B12<br>ST |

| Dxx                                | Data line of the INTERBUS ring                                                                                                               |                        |

| DO1<br>DO2<br>DI1<br>DI2           | Data line IN forward path Data line OUT forward path Data line OUT return path Data line IN return path                                      | ST<br>B12<br>B12<br>ST |

| CKxx                               | Clock line for the INTERBUS devices                                                                                                          |                        |

| CKO1<br>CKO2<br>CKI1<br>CKI2       | Clock line IN forward path Clock line OUT forward path Clock line OUT return path Clock line IN return path                                  | ST<br>B12<br>B12<br>ST |

| CRxx                               | Control line check sequence                                                                                                                  |                        |

| CRO1/MAUWR<br>CRO2<br>CRI1<br>CRI2 | Control line IN forward path/MAU warning return path* Control line OUT forward path Control line OUT return path Control line IN return path | ST<br>B12<br>B12<br>ST |

| /Resin/MAUWS                       | INTERBUS reset input/MAU warning branch*. Input filtered with $t_1 = 520 \ \mu s^{***}$ , directly passed on to pin /LBRes.                  | STp                    |

| /LBRes                             | INTERBUS reset output                                                                                                                        | B2                     |

| RBST                               | Alarm input whether outgoing INTERBUS interface is used. Input filtered with tr1 = 270 ms***                                                 | ST                     |

Table 1-5 Signal description (continued)

| Designation     | Meaning                                                                                                                                                                                                                                    | Туре |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| LBST            | Alarm input whether local bus interface is used in BK module applications. In all other modes of operation this pin is to be connected to V <sub>SS</sub> . Input filtered with tf1 = 270 ms***                                            | ST   |  |  |

|                 | Diagnostic signals                                                                                                                                                                                                                         |      |  |  |

| /StatErr        | "Module error" alarm input or $\mu P$ watchdog, input filtered with $t_{f1} = 270$ ms***. When using the pin as a $\mu P$ watchdog pin the scan time is set to $t_{f3} = 2.5$ $\mu$ s***. See also Section "SET-II register" on page 3-19. | STp  |  |  |

| /ModAck         | Acknowledge output for a recognized module error. This output is not used in standard applications.                                                                                                                                        | B2   |  |  |

| CONF            | "Reconfiguration request" alarm input. The input is filtered with $t_1 = 35 \text{ ms}^{***}$ . This input is connected to GND in standard applications.                                                                                   |      |  |  |

| RBDA            | "Outgoing interface is disabled" alarm output                                                                                                                                                                                              |      |  |  |

| LBDA/TR         | "Local bus disabled" alarm output for BK "PCP active" with μP with PCP protocol software                                                                                                                                                   |      |  |  |

| ВА              | "INTERBUS active" alarm output                                                                                                                                                                                                             | B12  |  |  |

| Error           | "Error in the connected local bus" alarm output for BK modules                                                                                                                                                                             | B12  |  |  |

|                 | Signals for external register expansion                                                                                                                                                                                                    |      |  |  |

| ClkExR          | Clock for external shift registers                                                                                                                                                                                                         | B12  |  |  |

| ToExR1          | Data output for external shift registers without using the SUPI 3 internal registers                                                                                                                                                       | B2   |  |  |

| ToExR2          | Data output for external shift registers after use of the SUPI 3 internal registers                                                                                                                                                        | B2   |  |  |

| FromExR         | Data input for external shift registers                                                                                                                                                                                                    | ST   |  |  |

| LaOuD           | Latch signal of output data shift registers -> latch registers                                                                                                                                                                             | B2   |  |  |

| LaOuC           | Latch signal of control data shift registers -> latch registers                                                                                                                                                                            | B2   |  |  |

| /LaInD          | Latch signal of input data peripherals -> shift registers                                                                                                                                                                                  | B2   |  |  |

| /ResReg         | Reset signal for external latch registers. Can also be used as the "INTERBUS reset inactive" alarm output                                                                                                                                  | B12  |  |  |

| /ResU           | Initialization reset                                                                                                                                                                                                                       | ST   |  |  |

| V <sub>DD</sub> | +5 V supply voltage                                                                                                                                                                                                                        |      |  |  |

| V <sub>SS</sub> | Ground                                                                                                                                                                                                                                     |      |  |  |

**1-14** PHOENIX CONTACT 6025\_en\_03

- \* The MAU warning bits (Medium Attachment Unit) indicate a critical, but still functioning transmission path. MAU warnings can only be used in dedicated 2-wire operation (as MAU warning input filtered with tf3=520 μs). See also "Diagnostic inputs and outputs" on page 3-32

- \*\* These inputs require a hardware connection and the levels applied must not be modified during bus operation. (See Section "Overview" on page 2-1 and Section "Overview" on page 3-1)

- The filtering causes the signals to have the same state for at least the before a modified signal state becomes effective internally.

### **Explanation of cell types**

| BDp | Bidirectional, with Schmitt trigger inputs with internal pull-up resistor (50 $k\Omega$ typical) and 4 mA driver outputs |

|-----|--------------------------------------------------------------------------------------------------------------------------|

| CI  | CMOS input                                                                                                               |

| Clp | CMOS input with internal pull-up resistor (50 $k\Omega$ typical)                                                         |

| ST  | Schmitt trigger input                                                                                                    |

| STp | Schmitt trigger input with internal pull-up resistor (50 k $\Omega$ typical)                                             |

| B2  | 2 mA output                                                                                                              |

| B12 | 12 mA driver output                                                                                                      |

| osc | Oscillator cell                                                                                                          |

|     |                                                                                                                          |

### 1.4 Basic wiring

### 1.4.1 Clock, initialization

#### Clock supply

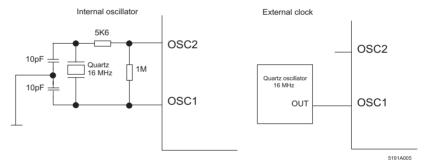

The SUPI 3 has an on-chip oscillator. Therefore, for applications in which the 15 MHz clock required by the SUPI 3 is of no further use, it is sufficient to use a 16 MHz quartz. The quartz is connected to the OSC1 and OSC2 pins. With the two capacitors that are connected from OSC1 and OSC2 to ground, the quartz forms a three-point oscillator. To set the working point of the on-chip oscillator, a 1  $M\Omega$  resistor is inserted, from OSC1 to OSC2, in parallel to the quartz. The capacitor values given in Figure "Clock lines of the SUPI 3" on page 1-16 are only a typical case. Please observe that due to the board layout the interfering capacitances have a considerable effect on the response time of the quartz oscillating circuit. Therefore, it is required to check, as for any other design, the correct behavior in the specified range and to modify the proposed values, if necessary. Tests of typical layouts with the quartz elements recommended in the component reference list of the INTERBUS Club have shown a safe response with the circuit and case capacitances of 22 pF each described in the SUPI 2 manual. The circuit of Figure 1-5 should be used for new designs or redesigns.

With this clock no other components must be operated additionally when a quartz crystal is used. The oscillator can also be operated by an external 16 MHz clock with a CMOS level. In this case, the oscillator operates as a buffer. The external clock signal is to be connected to the OSC1 oscillator input.

Figure 1-5 Clock lines of the SUPI 3

For the clock applies:

$f=16\;MHz\pm100\;ppm$

Clock ratio: 50% ± 10% duty cycle

1-16 PHOENIX CONTACT 6025\_en\_03

The permissible deviation applies to both short-time as well as long-time stability.

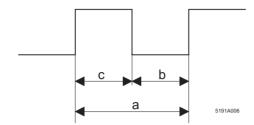

Figure 1-6 Clock ratio for the clock of INTERBUS protocol chips

Table 1-6 Clock timing

| Designation | Name             | Symbol | Min.  | Typical | Max.  | Unit |

|-------------|------------------|--------|-------|---------|-------|------|

| а           | Clock period     | tc     | 62.5  | 62.5    | 62.5  | ns   |

|             |                  |        | -6.25 |         | +6.25 | ps   |

| b           | Pulse width high | tрН    | 25    | 31.25   | 37.5  | ns   |

| С           | Pulse width low  | tpL    | 25    | 31.25   | 37.5  | ns   |

#### Initialization

To put the SUPI 3 to a defined state after power up, the initialization input /ResU should be set to low during power up. During operation, /ResU should be set to high. The reset time must be at least 2 clock cycles (125 ns) when the oscillator has settled and the voltage has been applied. During the reset phase all outputs have a low level. If in microprocessor applications the "µP\_not\_Ready" ID code is not used (see Section "ID code register" on page 3-20), the SUPI 3 must be initialized before the INTERBUS master is started up.

#### **Reset conditions**

The following conditions must be met for the INTERBUS reset at protocol chips of the 3rd generation (SUPI 3 kernel):

- The voltage must be monitored in the specified range (5 V  $\pm$  10%).

- The reset time must be at least 2 clock cycles (125 ns) when the oscillator has settled and the voltage is reached.

- The reset must not be influenced by software, LCAs, or similar.

In particular, the reset must not be controlled by a microprocessor.

**NOTE:** For indirect and direct connection of the reset input, the components used in the entire voltage range of the voltage monitor must be operated in accordance with regulations. Standard logic gates are not suitable for this purpose.

### 1.4.2 Configuration options

#### **INTERBUS** interfaces

The SUPI 3 has two separate INTERBUS interfaces, and one interface to the application. The SUPI 3 chip can be interfaced to the INTERBUS remote bus or local bus. The RGNDA pin of the SUPI 3 determines whether the chip will be used for a remote or local bus device.

In addition, pins KM0, KM1 and CKO1 have to be configured according to the following table.

Table 1-7 Configuration of the INTERBUS interface

| KM0 | KM1 | CKO1 | RGNDA | INTERBUS interface mode               |

|-----|-----|------|-------|---------------------------------------|

| 0   | 0   | -    | 1     | 8-wire local bus                      |

| 1   | 1   | 0    | 1     | 2-wire local bus                      |

| 1   | 1   | 0    | 0     | 2-wire remote bus 500 kbit            |

| 0   | 1   | 0    | 0     | 2-wire remote bus 2 Mbit <sup>*</sup> |

For copper interfaces only

Pin CKO1 is the incoming INTERBUS clock line for 8-wire applications. For 2-wire applications, the pin must have a low level.

1-18 PHOENIX CONTACT 6025\_en\_03

### **Multifunction interface**

The 16-bit multifunction pin interface (MFP) is the interface to the application. Configuration pins C3, C2, C1, C0 allow the following interface connections to the INTERBUS network

Table 1-8 Configuration of the MFP interface

| С3 | C2 | C1 | C0 | MFP mode                              |

|----|----|----|----|---------------------------------------|

| 1  | 0  | 0  | 0  | BK 8-wire local bus                   |

| 0  | 0  | 1  | 1  | BK I/O module with 8-wire local bus   |

| 0  | 0  | 0  | 0  | BK module 2-wire branch line          |

| 0  | 1  | 0  | 0  | BK I/O module with 2-wire branch line |

| 1  | 0  | 0  | 1  | 16-bit output                         |

| 1  | 0  | 1  | 0  | 16-bit input                          |

| 1  | 1  | 0  | 1  | 8-bit input and 8-bit output          |

| 0  | 0  | 0  | 1  | μP interface 1 byte                   |

| 1  | 0  | 1  | 1  | μP interface 2 bytes                  |

| 1  | 1  | 1  | 1  | μP interface 4 bytes                  |

| 1  | 1  | 0  | 0  | μP interface 6 bytes                  |

| 0  | 0  | 1  | 0  | μP interface 8 bytes                  |

#### Identification code

Each INTERBUS device has an identification code (ID code), which can be read by the INTERBUS master (controller) in an identification cycle (ID cycle). The INTERBUS master obtains information from the identification code about the type of the device and its data register length in a data cycle. The identification code consists of three groups.

- An 8-bit code is applied to pins ID0-ID7. The INTERBUS Club has determined this code in the ID code specification, depending on the functionality of the device. An extract of these codes can be obtained from the Appendix.

- Signals ID13-ID15 are not available as pins. They are reserved for the system management (e.g. diagnostics) and cannot be changed directly by the user.

- Pins ID8-ID12 specify the physical data length of the entire bus device. It is to be set for each device according to the following table.

Table 1-9 ID code data length

| ID12 | ID11 | ID10 | ID9 | ID8 | Data length | Firmware version* |

|------|------|------|-----|-----|-------------|-------------------|

| 0    | 0    | 0    | 0   | 0   | 0 words     |                   |

| 0    | 0    | 0    | 0   | 1   | 1 word      |                   |

| 0    | 0    | 0    | 1   | 0   | 2 words     |                   |

| 0    | 0    | 0    | 1   | 1   | 3 words     |                   |

| 0    | 0    | 1    | 0   | 0   | 4 words     |                   |

| 0    | 0    | 1    | 0   | 1   | 5 words     |                   |

| 0    | 0    | 1    | 1   | 0   | 8 words     |                   |

Table 1-9 ID code data length (continued)

| ID12 | ID11 | ID10 | ID9 | ID8 | Data length | Firmware version* |

|------|------|------|-----|-----|-------------|-------------------|

| 0    | 0    | 1    | 1   | 1   | 9 words     |                   |

| 0    | 1    | 0    | 0   | 0   | 1 nibble    | 4.0               |

| 0    | 1    | 0    | 0   | 1   | 1 byte      | 4.0**             |

| 0    | 1    | 0    | 1   | 1   | 3 bytes     | 4.0**             |

| 0    | 1    | 1    | 0   | 0   | Reserved    |                   |

| 0    | 1    | 1    | 0   | 1   | 2 bits      | 4.0               |

| 0    | 1    | 1    | 1   | 0   | 6 words     | 3.2               |

| 0    | 1    | 1    | 1   | 1   | 7 words     | 3.2               |

| 1    | 0    | 0    | 0   | 0   | Reserved    |                   |

| 1    | 0    | 0    | 0   | 1   | 26 words    | 3.7               |

| 1    | 0    | 0    | 1   | 0   | 16 words    | 3.2               |

| 1    | 0    | 0    | 1   | 1   | 24 words    | 3.2               |

| 1    | 0    | 1    | 0   | 0   | 32 words    | 3.2               |

| 1    | 0    | 1    | 0   | 1   | 10 words    | 3.2               |

| 1    | 0    | 1    | 1   | 0   | 12 words    | 3.2               |

| 1    | 0    | 1    | 1   | 1   | 14 words    | 3.2               |

| 1    | 1    | x    | x   | x   | Reserved    |                   |

- \* The data length is supported by the controller board (bus master) with the specified firmware version or later.

- \*\* The data lengths 1 byte and 3 bytes are supported by the PC AT-T board, version 3.1 or later. The data lengths supported by firmware version 3.2 or later are recognized by the PC AT-T board by driver version 2.0 or later.

The length entry determines the data register length of the entire INTERBUS device - that means the total of registers configurable in the SUPI chip and additional external registers, if any. By default this length entry is wired via the SUPI 3 pins ID12-ID8 by hardware. The physical data length of the IBS SUPI 3 to be set by C0-C3 and possibly used external register must match the logic data length to be set by ID8-ID12, even if the chip was reconfigured with software afterwards (see Section "SET-I register" on page 3-16 and Section "SET-II register" on page 3-19).

1-20 PHOENIX CONTACT 6025\_en\_03

Example: SUPI 3 chip with register expansion SRE 1:

Data length SUPI 3: 4 words C3 to C0 0010

Data length SRE 1: 3 words

Length entry at the ID pins 7 words ID12 to 8 01111

(Total of SUPI 3 and register expansion)

**1-22** PHOENIX CONTACT 6025\_en\_03

### 2 INTERBUS interfaces

### 2.1 Overview

When the chip is interfaced to INTERBUS it can be connected to the remote bus, installation remote bus, or local bus.

Remote bus connection is always chosen when long distances (up to 800 m via fiber-optic HCS fiber or up to 400 m via wires) have to be covered. An asynchronous 2-wire protocol and a fiber-optic or differential voltage interface according to RS-485 are used in the remote bus. Therefore the bus cable requires two fibers or five signal lines. Five signal lines for electrical transmission are necessary since there is always one wire pair for the forward and return path as well as a ground cable. A remote bus device always has its own voltage supply. In the event of a remote bus failure, the entire network can only be operated up to the last functioning remote bus device. Post-connected devices can no longer be addressed.

The installation remote bus is a special type of remote bus. In a hybrid cable it carries additional 24 V for the power supply of the I/O. This limits expansion of the installation remote bus to a maximum of 50 m.

A local bus device is used where the physical distance to the next device is limited to less than 10 m (e.g., switch cabinet level). The synchronous 8-wire protocol with CMOS levels or the 2-wire protocol with CMOS levels is used for the local bus. The entire logic required for the INTERBUS interface of a local bus device is supplied by the pre-connected bus terminal module through a supply line in the bus cable. This allows to operate the INTERBUS interface even if the voltage of the application breaks down.

When a local bus branch device fails the bus terminal module can disconnect the defective local bus branch from the network. The rest of the network can continue operation.

### 2.2 Local bus interface 8-wire protocol

Table 2-1 8-wire local bus configuration

|   | KM0 | KM1 | CKO1 | RGNDA | INTERBUS interface mode |

|---|-----|-----|------|-------|-------------------------|

| Ī | 0   | 0   | -    | 1     | 8-wire local bus        |

The RGNDA pin is to be set to high and the KM0 and KM1 pins to low for local bus applications. The bus signal pins of the SUPI 3 fulfill the INTERBUS specification of the local bus. The 9 V supply of the local bus can be lowered to 5 V and monitored. The active low output signal of a monitoring module is connected to the /ResU initialization pin. The RBST pin is connected to pin 4 of the local bus output connector. The output connector of the INTERBUS cable contains a jumper. Without an output connector and thus without a jumper (RBST = 0), the outgoing interface is switched off and diverted to the return path by circuitries inside the chip.

15-pos D-SUB connectors are used for the local bus. The following table lists the assignments of the input and output interfaces.

Table 2-2 Pin assignment of the 15-pos. D-SUB INTERBUS local bus connector

| Pin | Signal name of the incoming interface (male connector) | Signal name of the outgoing interface (female connector) |

|-----|--------------------------------------------------------|----------------------------------------------------------|

| 1   | +9 V                                                   | +9 V                                                     |

| 2   | +9 V                                                   | +9 V                                                     |

| 3   | Not used                                               | +5 V                                                     |

| 4   | Not used                                               | RBST                                                     |

| 5   | SLI1                                                   | SLI2                                                     |

| 6   | CKI1                                                   | CKI2                                                     |

| 7   | CRI1                                                   | CRI2                                                     |

| 8   | DI1                                                    | DI2                                                      |

| 9   | GND                                                    | GND                                                      |

| 10  | GND                                                    | GND                                                      |

| 11  | /ResIn                                                 | /LBRes                                                   |

| 12  | SLO1                                                   | SLO2                                                     |

| 13  | CKO1                                                   | CKO2                                                     |

| 14  | CRO1                                                   | CRO2                                                     |

| 15  | DO1                                                    | DO2                                                      |

Please refer to the Appendix for application examples.

### Local bus interface 2-wire protocol

Table 2-3 2-wire local bus configuration

| KM0 | KM1 | CKO1 | RGNDA | INTERBUS interface mode |

|-----|-----|------|-------|-------------------------|

| 1   | 1   | 0    | 1     | 2-wire local bus        |

The two INTERBUS interfaces only consist of the data lines DO1, DI1, DO2, DI2 and RBST. All other input signals of the two interfaces are to be connected to a low potential. The **incoming** bus interface can be equipped with optocouplers for electrical isolation. The /RBST signal is jumpered in the output connector to  $V_{SS}$ . Without output connector (/RBST = 1), the outgoing interface is thus switched off and diverted to the return path by circuitries inside the chip.

2-2 PHOENIX CONTACT 6025\_en\_03

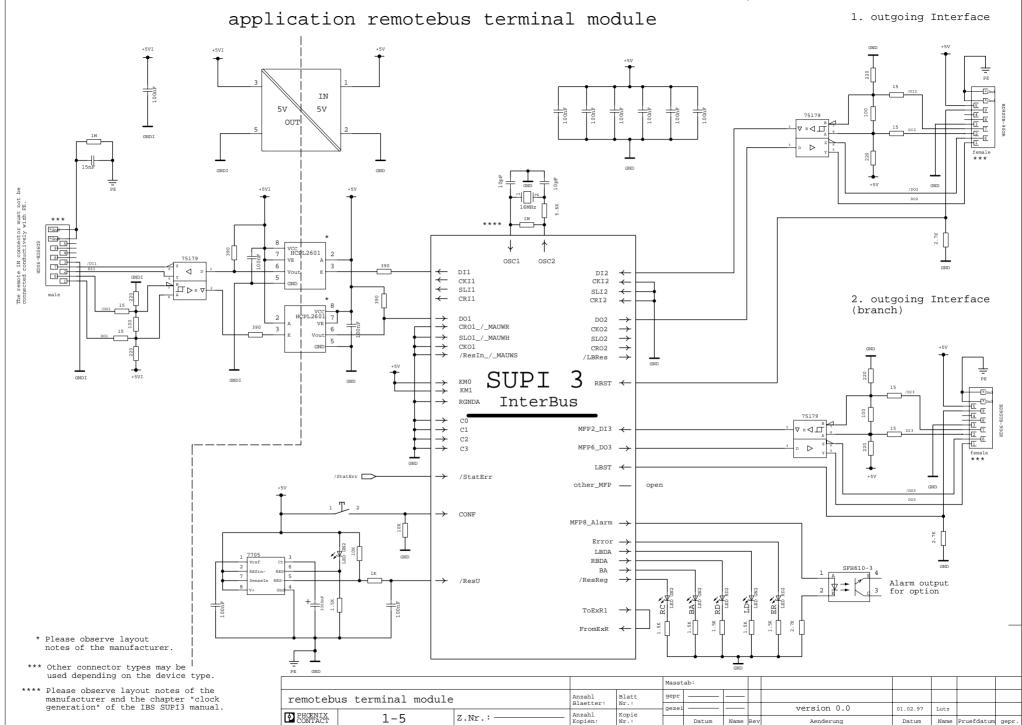

### 2.3 Remote bus connection

Table 2-4 Remote bus configuration

| KM0 | KM1 | CKO1 | RGNDA | INTERBUS interface mode      |

|-----|-----|------|-------|------------------------------|

| 1   | 1   | 0    | 0     | 2-wire remote bus, 500 kbits |

Fiber-optic transmitters and receivers or RS-485 drivers are pre-connected to the INTERBUS interface. The two INTERBUS interfaces consist only of data lines DO1, DI1, DO2, and DI2. All other input signals of the two interfaces are to be connected to a low potential. The incoming bus interface is equipped with optocouplers for electrical isolation.

The RBST pin is connected to pin 9 of the remote bus output connector. Pin RBST recognizes the physical position of the device in the ring. A low potential is connected externally to this pin via a resistor. Pin 9 is jumpered to  $V_{DD}$  in the remote bus cable connector. The RBST input is thus connected to high and SUPI 3 recognizes that it is not the last device in the ring. Therefore, it forwards its data to the following device in the ring. Without output connector (RBST = 0), the outgoing interface is switched off and diverted to the return path by circuitries inside the chip.

By default, 9-pos D-SUB connectors are used for the remote bus. When using other connectors, make sure that RBST is high when the connector is connected and low when the connector is disconnected. The following table lists the assignments of the input and output interfaces.

Table 2-5 Pin assignment of the 9-pos. D-SUB INTERBUS remote bus connector

| Pin | Signal name of the incoming interface (male connector) | Signal name of the outgoing interface (female connector) |

|-----|--------------------------------------------------------|----------------------------------------------------------|

| 1   | DO1                                                    | DO2                                                      |

| 2   | DI1                                                    | DI2                                                      |

| 3   | GNDI                                                   | GND                                                      |

| 4   | Reserved                                               | Reserved                                                 |

| 5   | Reserved                                               | +5 V                                                     |

| 6   | /DO1                                                   | /DO2                                                     |

| 7   | /DI1                                                   | /DI2                                                     |

| 8   | Reserved                                               | Reserved                                                 |

| 9   | Reserved                                               | RBST                                                     |

Please refer to the Appendix for application examples.

2-4 PHOENIX CONTACT 6025\_en\_03

# 3 Application interface

### 3.1 Overview

The configuration of the MFP interface determines how the application accesses the INTERBUS network via the SUPI 3 chip.

Three classes are distinguished:

- Bus terminal module (BK)

- Direct input/output

- Access using a microprocessor (μP interface).

The following table lists the three classes and the configuration via pins C3, C2, C1 and C0.

Table 3-1 Operating modes of the MFP interface

| C3 | C2 | C1 | C0 | MFP mode                              |

|----|----|----|----|---------------------------------------|

| 1  | 0  | 0  | 0  | BK module 8-wire local bus            |

| 0  | 0  | 1  | 1  | BK I/O module with 8-wire local bus   |

| 0  | 0  | 0  | 0  | BK module 2-wire branch line          |

| 0  | 1  | 0  | 0  | BK I/O module with 2-wire branch line |

| 1  | 0  | 0  | 1  | 16-bit output                         |

| 1  | 0  | 1  | 0  | 16-bit input                          |

| 1  | 1  | 0  | 1  | 8-bit input and 8-bit output          |

| 0  | 0  | 0  | 1  | μP interface 1 byte                   |

| 1  | 0  | 1  | 1  | μP interface 2 bytes                  |

| 1  | 1  | 1  | 1  | μP interface 4 bytes                  |

| 1  | 1  | 0  | 0  | μP interface 6 bytes                  |

| 0  | 0  | 1  | 0  | μP interface 8 bytes                  |

### 3.2 Bus terminal module mode

A bus terminal (BK) module always starts a new level in the INTERBUS system. A new level can be a remote bus or a local bus. A maximum of 16 levels (FW 4.0 or later) is permitted. BK modules are always remote bus devices.

A BK module connects the INTERBUS local bus devices in the field with the INTERBUS remote bus. The BK module makes voltage supply (9 V/1 A) available for the INTERBUS logic of the local bus devices. The BK module can also connect or disconnect the connected remote bus or local bus branch to or from the rest of the network when requested by the INTERBUS master.

A distinction is made between a standard BK module and a BK module (BK) with I/O points (BK I/O).

The standard BK module fulfills the functions described above. However, it has no I/O points so that a data length of "0" must be set. Since no external I/O points are implemented, the FromExR input pin is to be connected to the ToExR1 output.

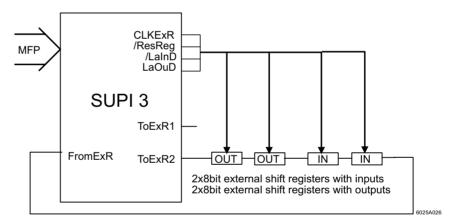

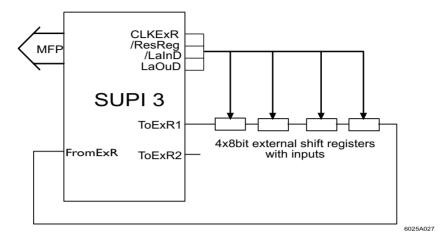

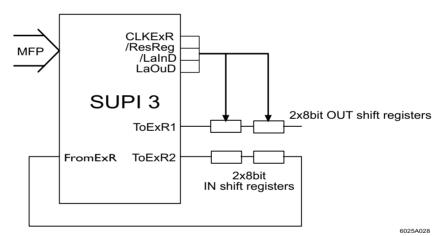

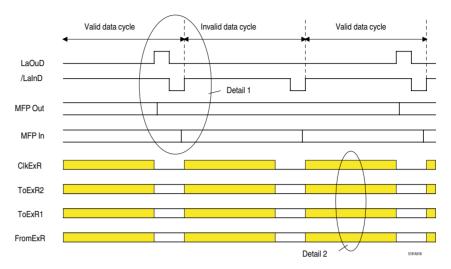

In addition to the BK functions described above, the BK modules with I/O points can loop external in I/O points between pins ToExR1 and FromExR (see also Section 3.5). The LBST message input is used in these operating modes to recognize a connected local bus or remote bus branch cable.

#### BK module with 8-wire local bus branch

Table 3-2 Configuration BK module with local bus branch

| C3 | C2 | C1 | C0 | MFP mode                            |

|----|----|----|----|-------------------------------------|

| 1  | 0  | 0  | 0  | BK module 8-wire local bus          |

| 0  | 0  | 1  | 1  | BK I/O module with 8-wire local bus |

Both operating modes provide as local bus an 8-wire interface which is available at the MFP interface according to the following table:

| MFP(n) | Assignment |                                    |

|--------|------------|------------------------------------|

| 0      | CKI        | Clock line input                   |

| 1      | SLI        | Control line data/ID cycle input   |

| 2      | DI         | Data line input                    |

| 3      | CRI        | Control line check sequence input  |

| 4      | СКО        | Clock line output                  |

| 5      | SLO        | Control line data/ID cycle output  |

| 6      | DO         | Data line output                   |

| 7      | CRO        | Control line check sequence output |

| 8      | ALARM      | Alarm output <sup>1</sup>          |

| 9      | Х          |                                    |

| 10     | Х          |                                    |

| 11     | X          |                                    |

| 12     | Х          |                                    |

| 13     | Х          |                                    |

| 14     | Х          |                                    |

| 15     | Х          |                                    |

The INTERBUS master can set the alarm output via a corresponding service.

#### X: Not to be used

In this case, the /LBRes signal belongs to the complete 8-wire local bus interface.

3-2 PHOENIX CONTACT 6025\_en\_03

#### BK module with 2-wire branch

A second group within the "bus terminal module" class are BKs with 2-wire branch as an additional INTERBUS interface. The 2-wire branch can be used, for example, for setting up an (installation) remote bus segment or a 2-wire local bus segment. In this group a distinction is also made between a BK and a BK I/O.

Table 3-3 Configuration BK module with 2-wire branch

| С3 | C2 | C1 | C0 | MFP mode                              |

|----|----|----|----|---------------------------------------|

| 0  | 0  | 0  | 0  | BK module 2-wire branch line          |

| 0  | 1  | 0  | 0  | BK I/O module with 2-wire branch line |

In this group the MFP interface has the following assignment:

| MFP(n) | Assignment |                    |

|--------|------------|--------------------|

| 0      | X          |                    |

| 1      | Х          |                    |

| 2      | DI         | Incoming data line |

| 3      | Х          |                    |

| 4      | Х          |                    |

| 5      | Х          |                    |

| 6      | DO         | Outgoing data line |

| 7      | Х          |                    |

| 8      | ALARM      | Alarm output *     |

| 9      | Х          |                    |

| 10     | Х          |                    |

| 11     | Х          |                    |

| 12     | Х          |                    |

| 13     | Х          |                    |

| 14     | Х          |                    |

| 15     | Х          |                    |

X: Not to be used

<sup>\*</sup> The INTERBUS master can set the alarm output via a corresponding service.

## 3.3 Input/output mode

#### 16-bit output

In the 16-bit output mode the INTERBUS OUT data of the first two internal OUT registers is available in parallel at the multifunction pins and can be connected directly to the application. Data is updated synchronously with the INTERBUS cycle. The outputs are 4 mA CMOS drivers. If no additional I/O points are to be used, the 'ToExR2' and 'FromExR' pins are to be connected. Should additional IN data be used, external shift registers are to be connected between pins 'ToExR1' and 'FromExR'. OUT data can be expanded by the connection of external shift registers to the 'ToExR2' pin (see also Section "Register expansion" on page 3-25).

Table 3-4 Configuration 16-bit output

| <b>C</b> 3 | C2 | C1 | C0 | MFP mode      |

|------------|----|----|----|---------------|

| 1          | 0  | 0  | 1  | 16-bit output |

Table 3-5 Assignment of the MFP interface for the 16-bit output mode

| MFP(n) | Assignment | Significance        |

|--------|------------|---------------------|

| 0      | Byte0A(0)  | 2 <sup>8</sup>      |

| 1      | Byte0A(1)  | 2 <sup>9</sup>      |

| 2      | Byte0A(2)  | 2 <sup>10</sup>     |

| 3      | Byte0A(3)  | 2 <sup>11</sup>     |

| 4      | Byte0A(4)  | 2 <sup>12</sup>     |

| 5      | Byte0A(5)  | 2 <sup>13</sup>     |

| 6      | Byte0A(6)  | 2 <sup>14</sup>     |

| 7      | Byte0A(7)  | 2 <sup>15</sup> MSB |

| 8      | Byte1A(0)  | 2 <sup>0</sup> LSB  |

| 9      | Byte1A(1)  | 2 <sup>1</sup>      |

| 10     | Byte1A(2)  | 2 <sup>2</sup>      |

| 11     | Byte1A(3)  | 2 <sup>3</sup>      |

| 12     | Byte1A(4)  | 2 <sup>4</sup>      |

| 13     | Byte1A(5)  | 2 <sup>5</sup>      |

| 14     | Byte1A(6)  | 2 <sup>6</sup>      |

| 15     | Byte1A(7)  | 2 <sup>7</sup>      |

Please note that the lower byte of the data word is on the MFP pins 8 to 15 and the higher byte is on the MFP pins 0 to 7.

3-4 PHOENIX CONTACT 6025\_en\_03

#### 16-bit input

In the 16-bit input mode, the application can connect 16 parallel signals directly to the multifunction pins. The inputs are designed as CMOS Schmitt triggers. Data is taken over synchronously to the INTERBUS cycle and transmitted to the INTERBUS master. The data length can be expanded by external shift registers which are connected between 'ToExR2' and 'FromExR'. Should additional OUT data be used, these external shift registers are to be connected to pin 'ToExR1'. If no external extension is necessary, pins 'ToExR2' and 'FROMEXR' are to be connected (see Section "Register expansion" on page 3-25).

Table 3-6 Configuration 16-bit input

| СЗ | C2 | C1 | C0 | MFP mode     |

|----|----|----|----|--------------|

| 1  | 0  | 1  | 0  | 16-bit input |

Table 3-7 Assignment of the MFP interface for the 16-bit input mode

| MFP(n) | Assignment | Significance        |

|--------|------------|---------------------|

| 0      | Byte0E(0)  | 2 <sup>8</sup>      |

| 1      | Byte0E(1)  | 2 <sup>9</sup>      |

| 2      | Byte0E(2)  | 2 <sup>10</sup>     |

| 3      | Byte0E(3)  | 2 <sup>11</sup>     |

| 4      | Byte0E(4)  | 2 <sup>12</sup>     |

| 5      | Byte0E(5)  | 2 <sup>13</sup>     |

| 6      | Byte0E(6)  | 2 <sup>14</sup>     |

| 7      | Byte0E(7)  | 2 <sup>15</sup> MSB |

| 8      | Byte1E(0)  | 2 <sup>0</sup> LSB  |

| 9      | Byte1E(1)  | 2 <sup>1</sup>      |

| 10     | Byte1E(2)  | 2 <sup>2</sup>      |

| 11     | Byte1E(3)  | 2 <sup>3</sup>      |

| 12     | Byte1E(4)  | 2 <sup>4</sup>      |

| 13     | Byte1E(5)  | 2 <sup>5</sup>      |

| 14     | Byte1E(6)  | 2 <sup>6</sup>      |

| 15     | Byte1E(7)  | 2 <sup>7</sup>      |

Please note that the lower byte of the data word is on the MFP pins 8 to 15 and the higher byte is on the MFP pins 0 to 7.

#### 8-bit input and 8-bit output

Unlike the two I/O modes described above, this mode does not represent a 16-bit, but an 8-bit device. The MFP interface is configured in such a way, that both 8-bit input, as well as 8-bit output is possible simultaneously without register expansion. The outputs are 4 mA CMOS drivers. Please observe (see also Section "Identification code") that the INTERBUS controller boards support the data length of 1 byte (8 bits) only as of firmware version 4.0. If no external expansion is necessary, the 'ToExR2' and 'FROMEXR' pins are to be connected (see Section "Register expansion" on page 3-25).

Table 3-8 Configuration 8-bit input and 8-bit output

| C3 | C2 | C1 | C0 | MFP mode                     |

|----|----|----|----|------------------------------|

| 1  | 1  | 0  | 1  | 8-bit input and 8-bit output |

Table 3-9 Assignment of the MFP interface for the 8-bit input and 8-bit output mode

| MFP(n) | Assignment | Significance       |        |

|--------|------------|--------------------|--------|

| 0      | Byte0A(0)  | 2 <sup>0</sup> LSB |        |

| 1      | Byte0A(1)  | 2 <sup>1</sup>     |        |

| 2      | Byte0A(2)  | 2 <sup>2</sup>     |        |

| 3      | Byte0A(3)  | 2 <sup>3</sup>     | OUTPUT |

| 4      | Byte0A(4)  | 2 <sup>4</sup>     | Byte   |

| 5      | Byte0A(5)  | 2 <sup>5</sup>     |        |

| 6      | Byte0A(6)  | 2 <sup>6</sup>     |        |

| 7      | Byte0A(7)  | 2 <sup>7</sup> MSB |        |

| 8      | Byte0E(0)  | 2 <sup>0</sup> LSB |        |

| 9      | Byte0E(1)  | 2 <sup>1</sup>     |        |

| 10     | Byte0E(2)  | 2 <sup>2</sup>     |        |

| 11     | Byte0E(3)  | 2 <sup>3</sup>     | INPUT  |

| 12     | Byte0E(4)  | 2 <sup>4</sup>     | Byte   |

| 13     | Byte0E(5)  | 2 <sup>5</sup>     |        |

| 14     | Byte0E(6)  | 2 <sup>6</sup>     |        |

| 15     | Byte0E(7)  | 2 <sup>7</sup> MSB |        |

Byte0A = Output byte

Byte0E = Input byte

Please refer to the Appendix for application examples.

**3-6** PHOENIX CONTACT **6025\_en\_03**

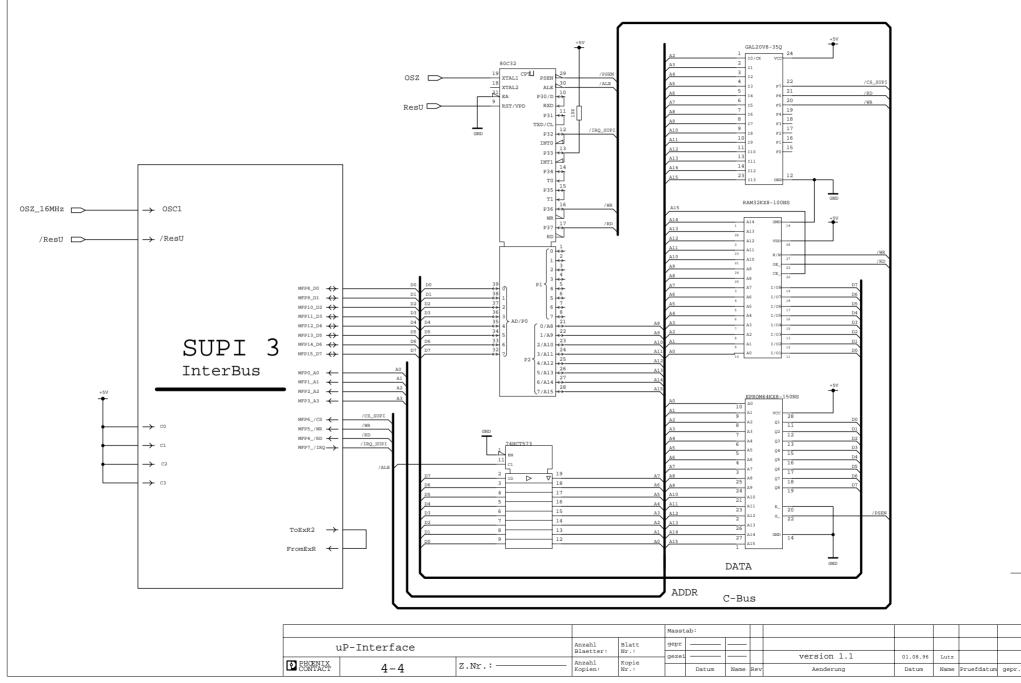

## 3.4 µP (microprocessor) access mode

In the  $\mu P$  access mode it is possible to address the SUPI 3 chip from a microprocessor, like an I/O component (e.g., RAM). For this purpose, the SUPI 3 has an 3-bit bidirectional data bus D7 to D0, a 4-bit address bus A3 to A0), the active-low control signals Chip Select /CS (/ENCR, /ENDRR), /ENDRW), Read (/RD), and Write (/WR) and an active-low interrupt request line /IRQ.

Table 3-10 Assignment of the MFP interface for the  $\mu P$  access mode

| MFP(n) | Assignment |

|--------|------------|

| 0      | A0         |

| 1      | A1         |

| 2      | A2         |

| 3      | А3         |

| 4      | /RD        |

| 5      | /WR        |

| 6      | /CS        |

| 7      | /IRQ       |

| 8      | D0         |

| 9      | D1         |

| 10     | D2         |

| 11     | D3         |

| 12     | D4         |

| 13     | D5         |

| 14     | D6         |

| 15     | D7         |

Please refer to the Appendix for application examples.

## MFP interface timing

The MFP interface timing is suitable for both Intel- and Motorola-based bus access. The signal /CS and /WR or /CS and /RD are connected internally such that even an inactive signal is sufficient to stop the access.

## Write access

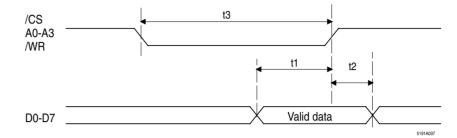

Figure 3-1 MFP interface timing, write access

Table 3-11 MFP interface timing, write access

| Symbol | Explanation                            | Time / ns<br>minimum |

|--------|----------------------------------------|----------------------|

| t1     | Valid data before positive edge of /WR | 15                   |

| t2     | Valid data after positive edge of /WR  | 10                   |

| t3     | /WR pulse width                        | 30                   |

3-8 PHOENIX CONTACT 6025\_en\_03

#### **Read access**

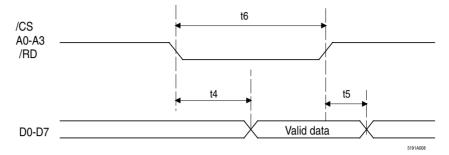

Figure 3-2 MFP interface timing, read access

Table 3-12 MFP interface timing, read access

| Symbol | Explanation                                         | Time / ns |      |

|--------|-----------------------------------------------------|-----------|------|

|        |                                                     | Min.      | Max. |

| t4     | Valid data after negative edge of /RD               |           | 25   |

| t5     | Data bus high resistance after positive edge of /RD |           | 25   |

| t6     | /RD pulse width                                     | 80        |      |

## μP modes of operation

Table 3-13 μP modes of operation

| S  | UPI pin |    |    | MFP interface mode   |

|----|---------|----|----|----------------------|

| СЗ | C2      | C1 | C0 |                      |

| 0  | 0       | 0  | 1  | μP interface 1 byte  |

| 1  | 0       | 1  | 1  | μP interface 2 bytes |

| 1  | 1       | 1  | 1  | μP interface 4 bytes |

| 1  | 1       | 0  | 0  | μP interface 6 bytes |

| 0  | 0       | 1  | 0  | μP interface 8 bytes |

In the  $\mu P$  modes of operation, the data width may be varied between one and eight bytes with the configuration pins C0 to C3. The five  $\mu P$  modes of operation, therefore, differ only with respect to the active data length. This data length can also be changed with the software (see Section "SET-II register" on page 3-19).

#### Address area assignment

The following register descriptions are independent of the selected  $\mu P$  mode of operation. The SUPI 3 chip provides four address lines A3 to A0. The address area assignment is backward-compatible with the SUPI 2 chip.

Table 3-14 Address area assignment of the SUPI 3

| Rel. address | Write register             | Read register              |

|--------------|----------------------------|----------------------------|

| 0            | IB-IN byte 0 (MSB)         | IB-OUT byte 0 (MSB)        |

| 1            | IB-IN byte 1               | IB-OUT byte 1              |

| 2            | IB-IN byte 2               | IB-OUT byte 2              |

| 3            | IB-IN byte 3               | IB-OUT byte 3              |

| 4            | Interrupt enable I         | Interrupt event I          |

| 5            | Set I                      | Interrupt event II         |

| 6            | Set II                     | Reserved                   |

| 7            | ID code (low byte)         | IB state                   |

| 8            | Cycle write                | Cycle read                 |

| 9            | Processor message register | Processor command register |

| 10           | IB-IN byte 4               | IB-OUT byte 4              |

| 11           | IB-IN byte 5               | IB-OUT byte 5              |

| 12           | IB-IN byte 6               | IB-OUT byte 6              |

| 13           | IB-IN byte 7 (LSB)         | IB-OUT byte 7 (LSB)        |

| 14           | Interrupt enable II        | Reserved                   |

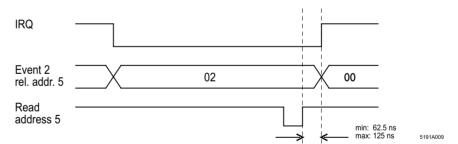

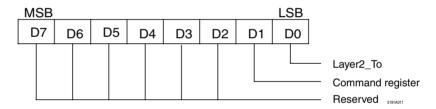

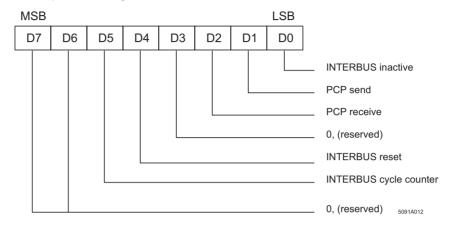

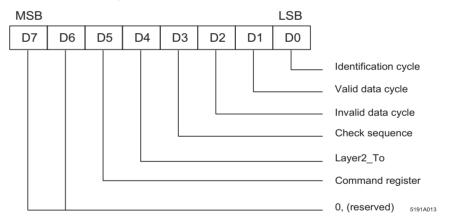

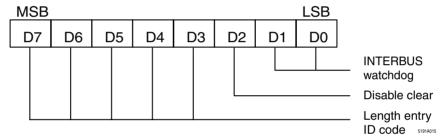

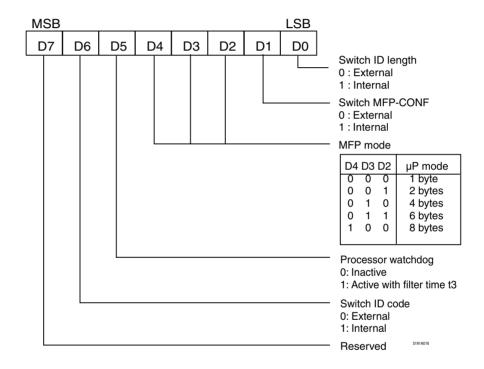

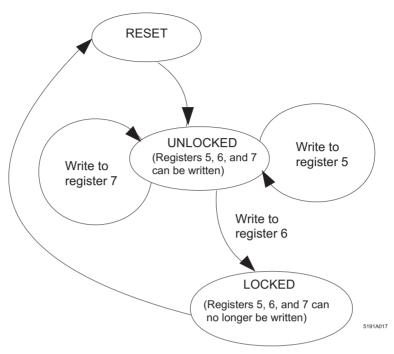

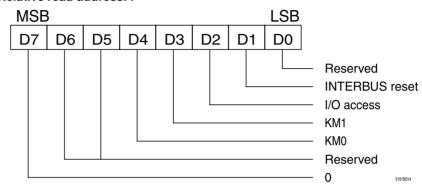

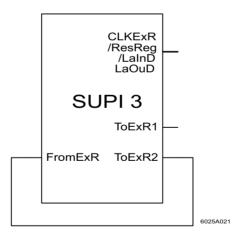

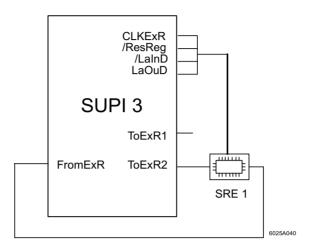

| 15           | Test mode                  | Test state                 |