## **TOSHIBA**

32 Bit RISC Microcontroller TX03 Series

TMPM363F10FG

## **TOSHIBA CORPORATION**

Semiconductor & Storage Products Company

TOSHIBA TMPM363F10FG

ARM, ARM Powered, AMBA, ADK, ARM9TDMI, TDMI, PrimeCell, RealView, Thumb, Cortex, Coresight, ARM9, ARM926EJ-S, Embedded Trace Macrocell, ETM, AHB, APB, and KEIL are registered trademarks or trademarks of ARM Limited in the EU and other countries.

**ARM**°

## Important Notices

Make sure to read read this chapter before using the product.

## 1 Serial bus interface

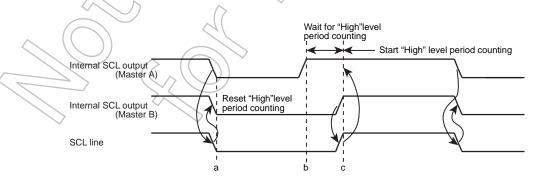

There are restrictions on the use of I2C bus mode when the multi-master function is used.

## 1.1 Description

When the multi-master function is used in I2C bus mode, if these masters start the communications simultaneously, the following phenomena may occur:

- 1. Communications may be locked up.

- 2. SCL pulse widths shorten; therefore these pulses may not satisfy I2C Specifications.

## 1.2 Condition

These phenomena occur only when the multi-master function is used in 12C bus mode. If a single master is used, these phenomena do not occur.

#### 1.3 Workaround

There is no workaround for these phenomena. Perform recovery process by software.

## 1.4 How to Recover from These Phenomena

Perform recovery process by software.

By using a timer, add timeout process to check whether communication is in a lock-up state.

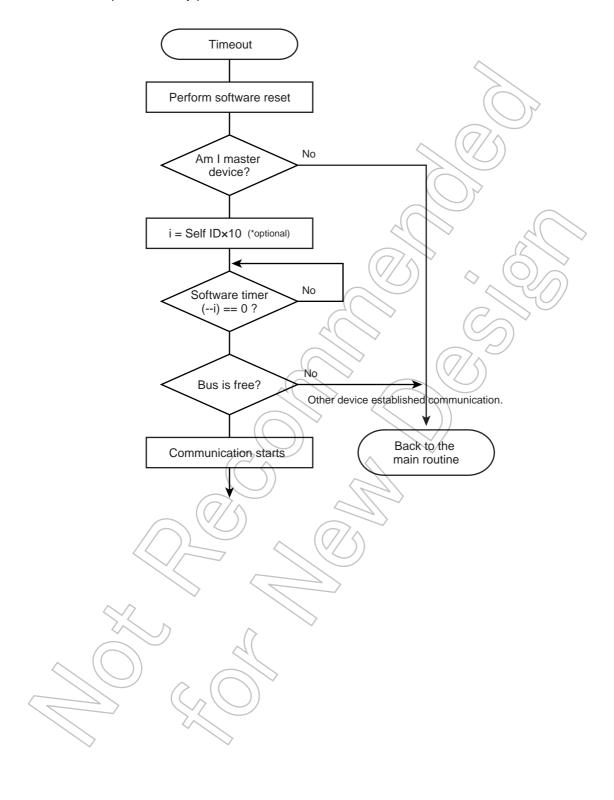

## An example of recovery process:

- 1. Start a timer count synchronously with start of the transmission.

- 2. If a serial interface interrupt (INTSBIx) does not occur in a certain period, the MCU determines the timeout.

- 3. If the MCU determines the timeout, communications may be locked up. Perform software reset on the serial bus interface circuit. This circuit is initialized to release communication from the lock up state.

- 4. Resend transmission data.

Mostly, Process 1 to 4 are enough to recovery; however if the multiple products are connected to the same bus line, add a delay time between each product's recovery process before Process 4 (resending data) is performed. This delay makes a time difference between each master; therefore bus collision can be avoided when the data is sent again.

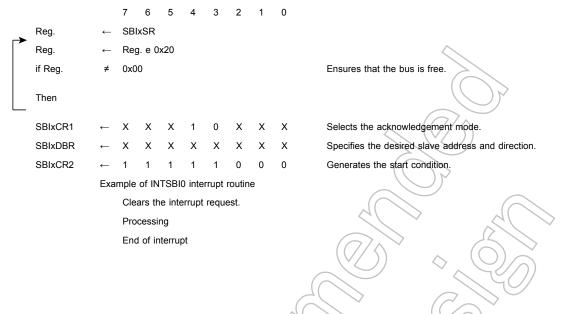

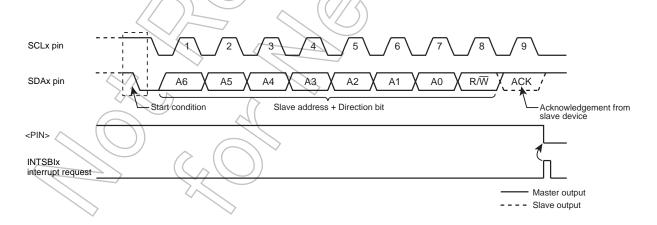

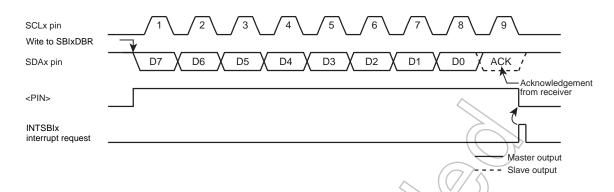

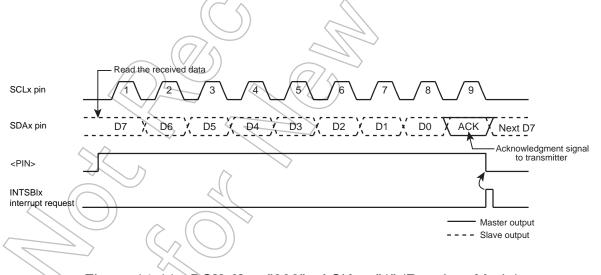

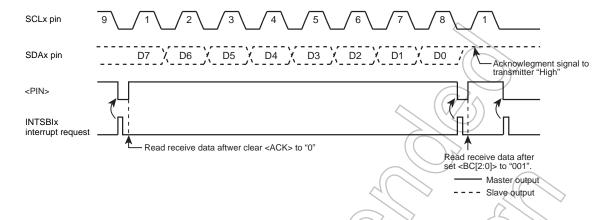

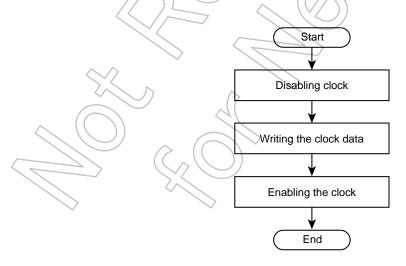

Example: Recovery process after a timeout is detected.

## <u>Introduction: Notes on the description of SFR (Special Function Register) under this specification</u>

An SFR (Special Function Register) is a control register for periperal circuits (IP).

The SFR addressses of IPs are described in the chapter on memory map, and the details of SFR are given in the chapter of each IP.

Definition of SFR used in this specification is in accordance with the following rules

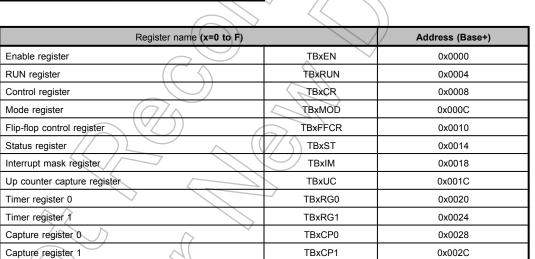

- a. SFR table of each IP as an example

- SFR tables in each chapter of IP provides register names, addresses and brief descriptions.

- All registers have a 32-bit unique address and the addresses of the registers are defined as follows, with some exceptions: "Base address + (Unique) address"

Base Address = 0x0000 0000

| Register name    |       | Address(Base+) |

|------------------|-------|----------------|

| Control register | SAMCR | 0x0004         |

|                  |       | 0x000C         |

Note: SAMCR register address is 32 bits wide from the address 0x0000\_0004 (Base Address(0x00000000) + unique address (0x0004)).

Note: The register shown above is an example for explanation purpose and not for demonstration purpose. This register does not exist in this microcontroller.

- b. SFR(register)

- Each register basically consists of a 32-bit register (some exceptions).

- The description of each register provides bits, bit symbols, types, initial values after reset and functions.

#### 1.2.2 SAMCR(Control register)

|             | 31   | 30 | 29 | 28 | 27    | 26    | 25  | 24  |

|-------------|------|----|----|----|-------|-------|-----|-----|

| bit symbol  | -    | -  | -  | -  | -     | - <   | -   | -   |

| After reset | 0    | 0  | 0  | 0  | 0     | 0     | 0   | 0   |

|             | 23   | 22 | 21 | 20 | 19    | 18    | 177 | 16  |

| bit symbol  | -    | -  | -  | -  | -     |       | )   | -   |

| After reset | 0    | 0  | 0  | 0  | 0 ^   | (0//< | 0   | 0   |

|             | 15   | 14 | 13 | 12 | 11    | 10    | 9   | 8   |

| bit symbol  | -    | -  | -  | -  | -     |       | МС  | DDE |

| After reset | 0    | 0  | 0  | 0  | 0     |       | 0   | 0   |

|             | 7    | 6  | 5  | 4  | 3     | 2     | 10  | 0   |

| bit symbol  | MODE |    |    |    | TDATA |       | 4   |     |

| After reset | 0    | 0  | 0  | 1  | 0     | 0     | 20  | 0   |

| Bit   | Bit Symbol | Туре | Function                                                                                                                                              |

|-------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-10 | -          | R    | "0" can be read.                                                                                                                                      |

| 9-7   | MODE[2:0]  | R/W  | Operation mode settings 000 : Sample mode 0 001 : Sample mode 1 010 : Sample mode 2 011 : Sample mode 3 The settings other than those above: Reserved |

| 6-0   | TDATA[6:0] | W    | Transmitted data                                                                                                                                      |

Note: The Type is divided into three as shown below.

R / W READ WRITE

R READ

WRITE

c. Data descriptopn

Meanings of symbols used in the SFR description are as shown below.

- x:channel numbers/ports

- n,m;bit numbers

- d. Register descriptoption

Registers are described as shown below.

Register name <Bit Symbol>

Exmaple: SAMCR<MODE>="000" or SAMCR<MODE[2:0]>="000"

<MODE[2:0]> indicates bit 2 to bit 0 in bit symbol mode (3bit width).

· Register name [Bit]

Example: SAMCR[9:7]="000"

It indicates bit 9 to bit 7 of the register SAMCR (32 bit width).

## Revision History

| Date      | Revision    | Comment                    |

|-----------|-------------|----------------------------|

| 2011/4/13 | Tentative 1 | First Release of Tentative |

| 2011/6/23 | 1           | First Release              |

| 2013/5/31 | 2           | Contents Revised           |

# **Table of Contents**

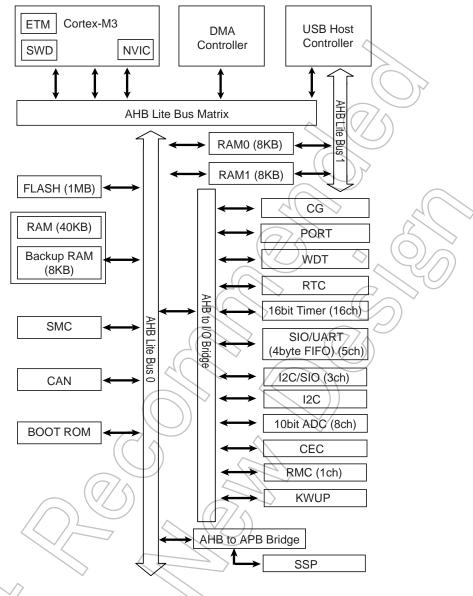

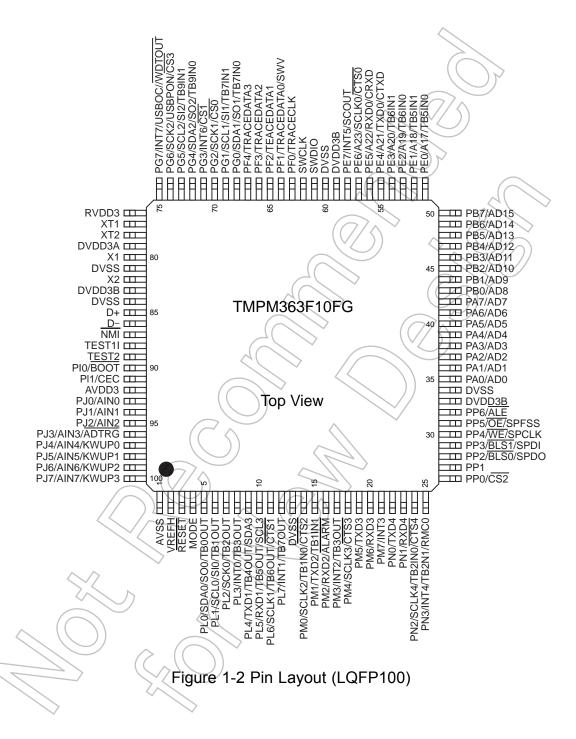

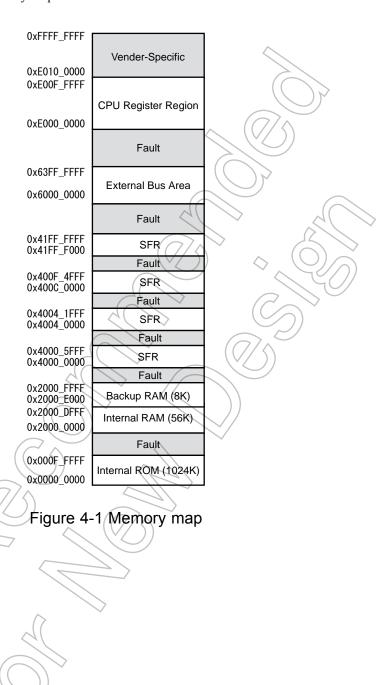

Introduction: Notes on the description of SFR (Special Function Register) under this specification TMPM363F10FG 1.1 Features. Block Diagram 5 Pin layout (Top view)......6 Pin names and Functions 7 Pin Numbers and Power Supply Pins. **Processor Core** Configurable Options 15 2.3 2.3.1 2.3.2 234 2.3.5 Events 17 Exclusive access 17 **Debug Interface** 3ASW-DP 19 Pin functions 20 Peripheral Functions in Halt Mode......21 Reset Vector Break. 21 3.7 Memory Map 4.2 SFR area detail 25

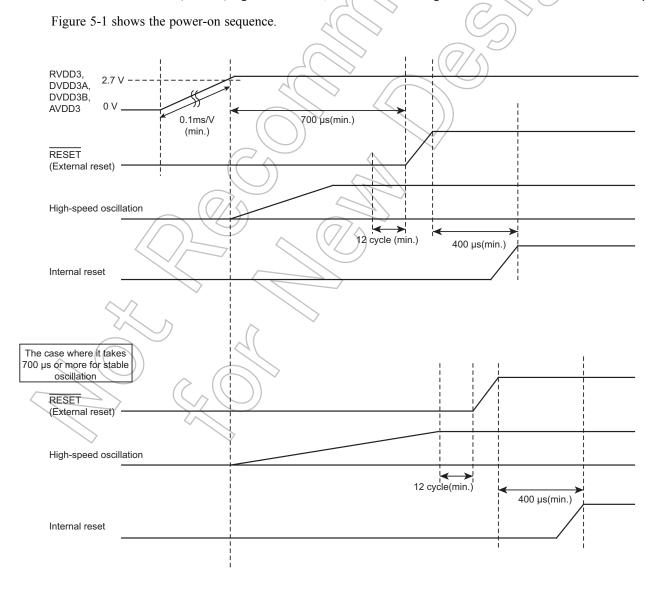

| 5. | Reset                                                                                          |                                         |    |

|----|------------------------------------------------------------------------------------------------|-----------------------------------------|----|

|    | 5.1 Cold reset                                                                                 |                                         | 27 |

|    |                                                                                                |                                         |    |

|    | 5.2 Warm reset                                                                                 |                                         |    |

|    | 5.3 After reset.                                                                               |                                         | 29 |

|    | 5.5 Mill reset                                                                                 |                                         | ,  |

|    |                                                                                                |                                         |    |

| 5. | Clock / Mode Control                                                                           |                                         |    |

|    | 6.1 Features                                                                                   | $\mathcal{A}(\mathcal{A})$              | 31 |

|    |                                                                                                |                                         | 31 |

|    | 6.2 Registers                                                                                  |                                         | 32 |

|    | 6.2.2 CGSYSCR (System control register)                                                        | (\(\frac{\lambda}{\rangle}\))           | 33 |

|    | 6.2.3 CGOSCCR (Oscillation control register)                                                   |                                         | 34 |

|    | 6.2.4 CGSTRYCR (Standby control register)                                                      |                                         | 35 |

|    | 6.2.5 CGPLLSEL (PLL Selection Register)                                                        |                                         | 36 |

|    | 6.2.6 CGCKSEL (System clock selection register)                                                |                                         | 37 |

|    | 6.3 Clock control                                                                              |                                         | 38 |

|    | 6.3.1 Clock Type                                                                               |                                         | 38 |

|    | 6.3.2 Initial Values after Reset                                                               | - X - X - X - X - X - X - X - X - X - X | 38 |

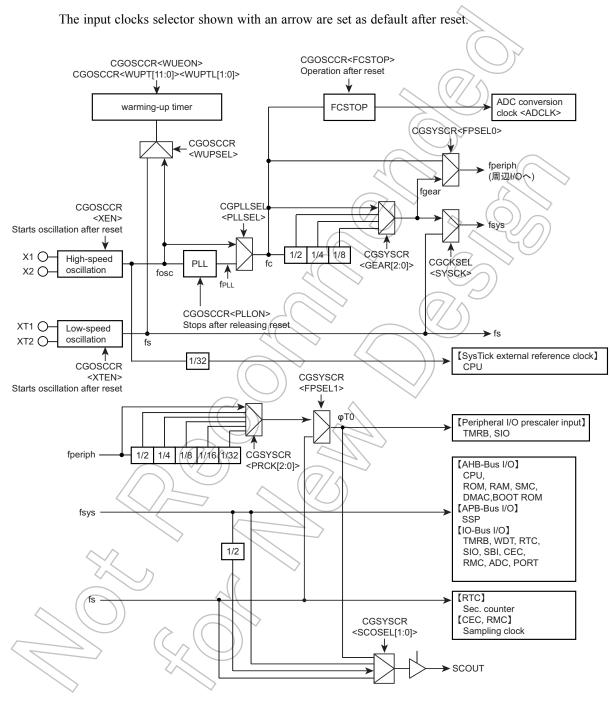

|    | 6.3.3 Clock system Diagram                                                                     |                                         | 39 |

|    | 6.3.5 Clock Multiplication Circuit (PLL)                                                       |                                         |    |

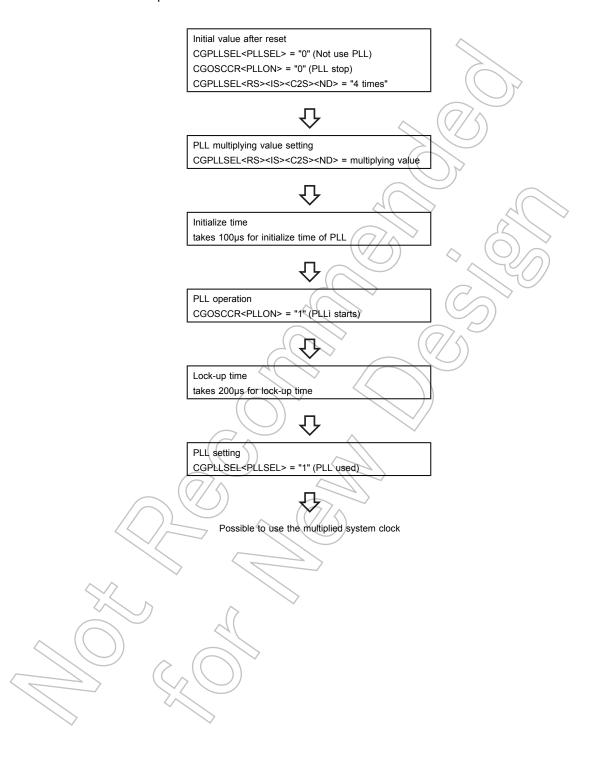

|    | 6.3.5.1 How to configure the PLL function                                                      |                                         |    |

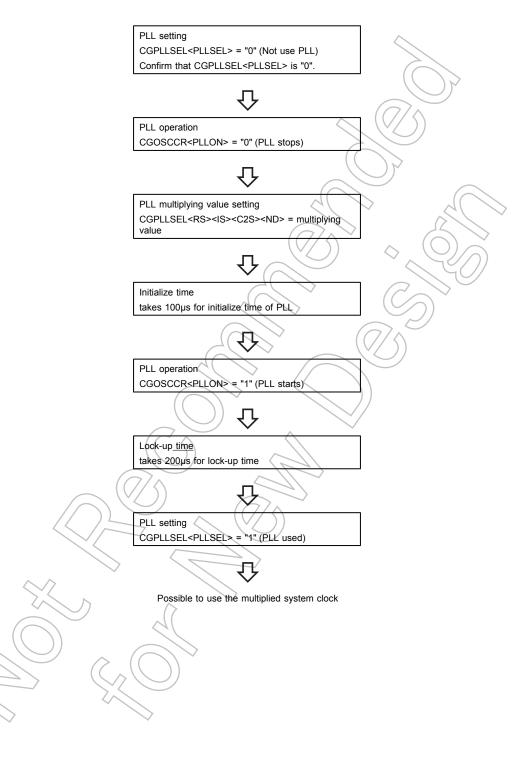

|    | 6.3.5.2 Changing PLL multiplying                                                               |                                         |    |

|    | 6.3.5.3 Start PLL sequence 6.3.5.4 Multiplying value change sequence                           | _                                       |    |

|    | 6.3.6 System Clock                                                                             |                                         | 46 |

|    | 6.3.6.1 High-speed clock                                                                       |                                         |    |

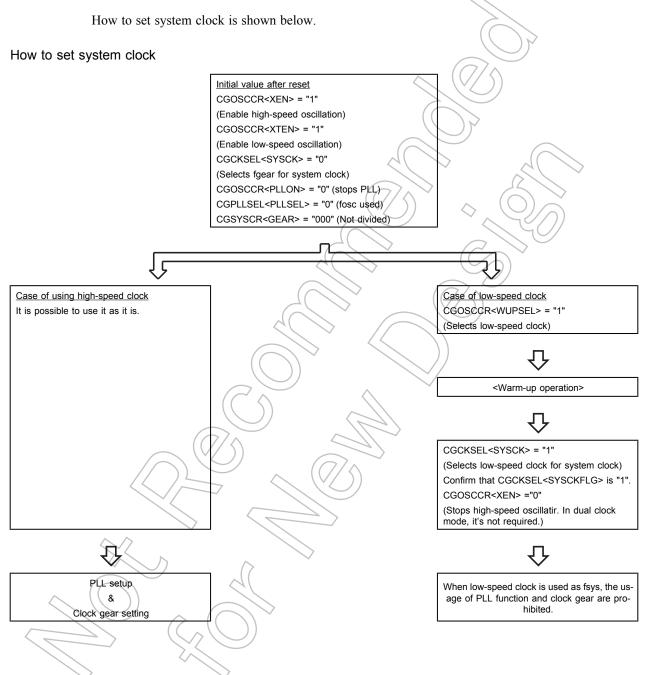

|    | 6.3.6.2 Low-speed clock<br>6.3.6.3 Setting system clock                                        |                                         |    |

|    | 6.3.7 Prescaler Clock Control                                                                  |                                         | 48 |

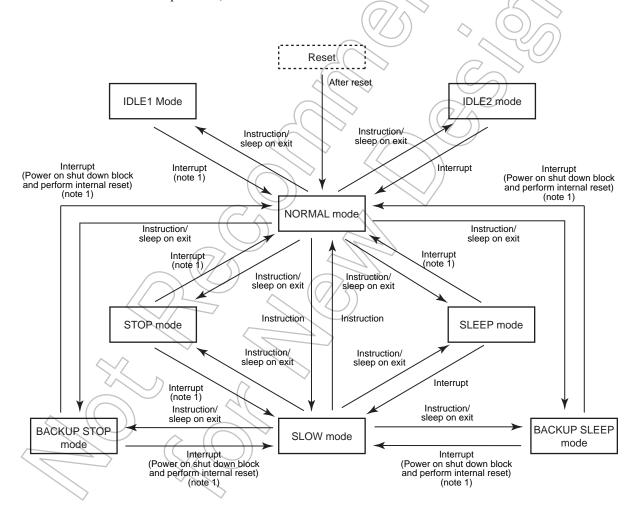

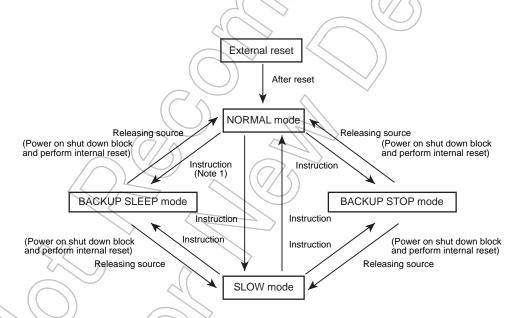

|    | 6.3.8 System Clock Pin Output Function  6.4 Modes and Mode Transitions  6.4.1 Mode Transitions | <u> </u>                                | 48 |

|    | 6.4 Modes and Mode Transitions                                                                 | // 5)                                   | 49 |

|    | 6.4.1 Mode Transitions                                                                         | <u> </u>                                | 49 |

|    | 6.5 Operation Mode.                                                                            |                                         | 50 |

|    | 6.5.1 NORMAL mode                                                                              | <u> </u>                                | 50 |

|    | 6.5.2 SLOW mode                                                                                |                                         |    |

|    | 6.6 Low Power Consumption Modes                                                                |                                         | 51 |

|    | 6.6.1 IDLE Mode (IDLE2, IDLE1)                                                                 |                                         | 51 |

|    | 6.6.1.1 IDLE2 mode                                                                             |                                         |    |

|    | 6.6.1.2 IDLE1 mode<br>6.6.2 SLEEP mode                                                         |                                         | 52 |

|    |                                                                                                |                                         |    |

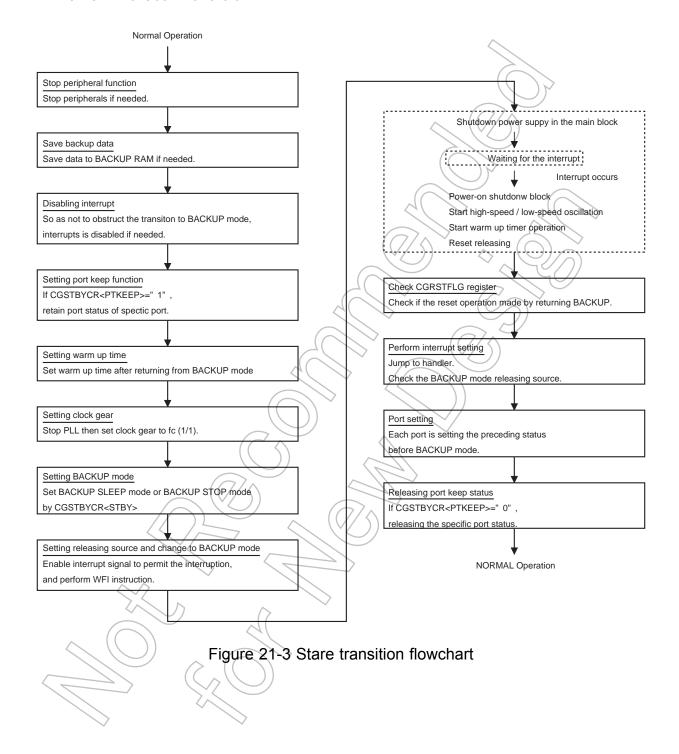

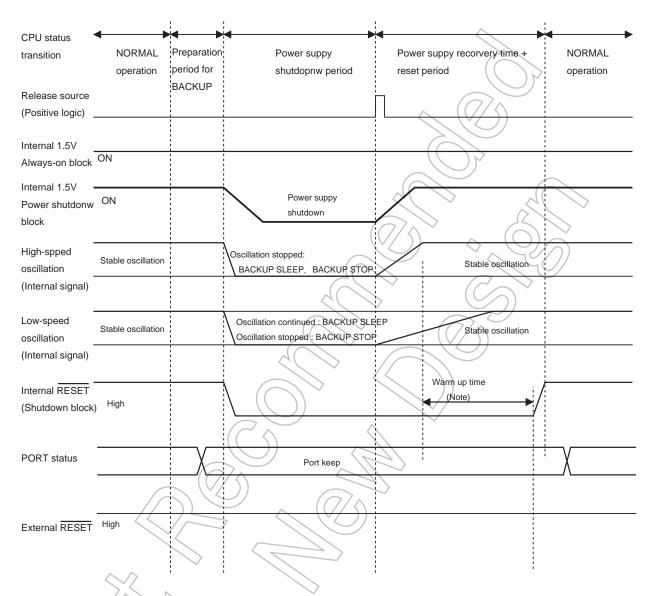

| _  | 6.6.4 BACKUP mode (BACKUP STOP, BACKUP SLEE                                                    |                                         |    |

|    | 6.6.5 Low power Consumption Mode Setting                                                       |                                         |    |

|    | 6.6.6 Operational Status in Each Mode                                                          |                                         |    |

|    | 6.6.7 Releasing the Low Power Consumption Mode                                                 |                                         |    |

|    | 6.6.8 Warm-up                                                                                  |                                         |    |

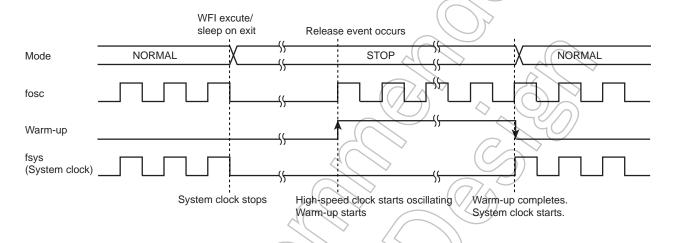

|    | 6.6.9.1 Transition of operation modes: NORMAL → STOP -                                         |                                         | 00 |

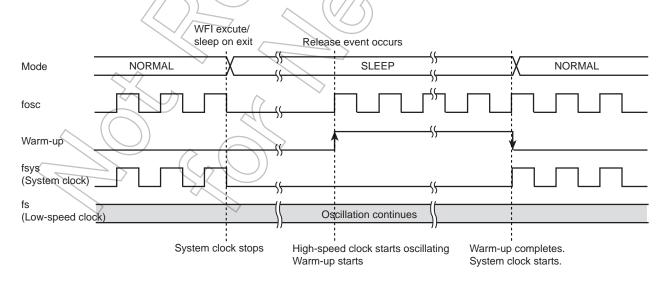

|    | 6.6.9.2 Transition of operation modes : NORMAL $\rightarrow$ SLEEP                             |                                         |    |

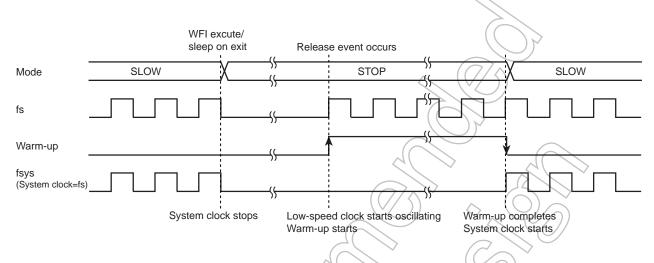

|    | 6.6.9.3 Transition of operation modes: SLOW $\rightarrow$ STOP $\rightarrow$ S                 |                                         |    |

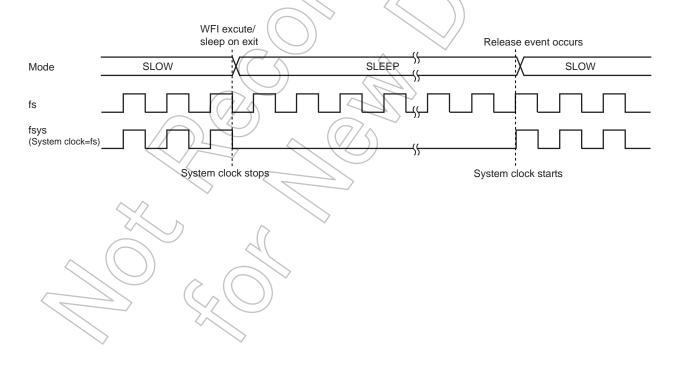

|    | 6.6.9.4 Transition of operation modes : SLOW $\rightarrow$ SLEEP $\rightarrow$                 | SLUW                                    |    |

|    |                                                                                                |                                         |    |

| ,  | E                                                                                              |                                         |    |

| 7. | Exceptions                                                                                     |                                         |    |

|    | 7.1 Overview                                                                                   |                                         | 63 |

|                                                                                                                                                               | exception types                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                                                               | Iandling Flowchart                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| 7.1.2.1<br>7.1.2.2                                                                                                                                            | Exception Request and Detection Exception Handling and Branch to the Interrupt Service Routine (Pre-emption)                                                                                                                                                                                                                                                                                                              |        |

| 7.1.2.3                                                                                                                                                       | Executing an ISR                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 7.1.2.4                                                                                                                                                       | Exception exit                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| 7.2 <b>Res</b>                                                                                                                                                | et Exceptions                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| 7.3 Nor                                                                                                                                                       | n-Maskable Interrupts (NMI)                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 7.4 Sys                                                                                                                                                       | Tick ( ( )                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 7.7 Bys                                                                                                                                                       | TICK                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 7.5 Inte                                                                                                                                                      | errupts                                                                                                                                                                                                                                                                                                                                                                                                                   | •••••  |

| 7.5.1 Iı<br>7.5.1.1                                                                                                                                           | Interrupt Sources                                                                                                                                                                                                                                                                                                                                                                                                         | •••••• |

| 7.5.1.1                                                                                                                                                       | Generation                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 7.5.1.3                                                                                                                                                       | Transmission                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 7.5.1.4<br>7.5.1.5                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.5.1.6                                                                                                                                                       | List of Interrupt Sources Active level                                                                                                                                                                                                                                                                                                                                                                                    | 7      |

|                                                                                                                                                               | nterrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 7.5.2.1                                                                                                                                                       | Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 7.5.2.2                                                                                                                                                       | Preparation  Detection by Cleak Conserter                                                                                                                                                                                                                                                                                                                                                                                 |        |

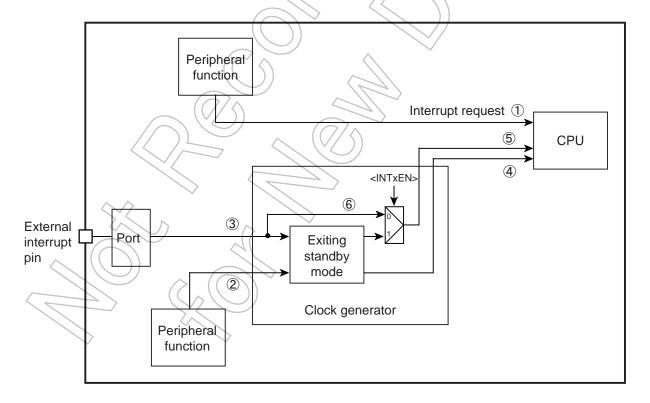

| 7.5.2.3<br>7.5.2.4                                                                                                                                            | Detection by Clock Generator Detection by CPU                                                                                                                                                                                                                                                                                                                                                                             |        |

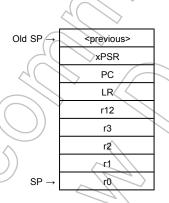

| 7.5.2.5                                                                                                                                                       | CPU processing                                                                                                                                                                                                                                                                                                                                                                                                            |        |

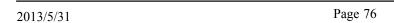

| 7.5.2.6                                                                                                                                                       | Interrupt Service Routine (ISR)                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6 Exc                                                                                                                                                       | ception / Interrupt-Related Registers                                                                                                                                                                                                                                                                                                                                                                                     |        |

|                                                                                                                                                               | Register List.                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|                                                                                                                                                               | IVIC Registers                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| 7.6.2.1<br>7.6.2.2                                                                                                                                            | SysTick Control and Status Register                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 7.6.2.3                                                                                                                                                       | SysTick Reload Value Register SysTick Current Value Register                                                                                                                                                                                                                                                                                                                                                              |        |

| 7.6.2.4                                                                                                                                                       | SysTick Calibration Value Register                                                                                                                                                                                                                                                                                                                                                                                        |        |

| 7.6.2.5                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.6<br>7.6.2.7                                                                                                                                            | Interrupt Set-Enable Register 2 Interrupt Set-Enable Register 3                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.8                                                                                                                                                       | Interrupt Set-Enable Register 4                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.9                                                                                                                                                       | Interrupt Clear-Enable Register 1                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 7.6.2.10<br>7.6.2.11                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.11                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.13                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.14                                                                                                                                                      | 1/ = \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 7.6.2.15<br>7.6.2.16                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.17                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.18                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.19                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.20<br>7.6.2.21                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.22                                                                                                                                                      | 2 Vector Table Offset Register                                                                                                                                                                                                                                                                                                                                                                                            |        |

|                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.23                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.24                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 7.6.2.24<br>7.6.2.25                                                                                                                                          | System Handler Control and State Register                                                                                                                                                                                                                                                                                                                                                                                 | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3<br>7.6.3.1                                                                                                                      | System Handler Control and State Register Tock generator registers                                                                                                                                                                                                                                                                                                                                                        | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3<br>7.6.3.1<br>7.6.3.2                                                                                                           | System Handler Control and State Register  Plock generator registers                                                                                                                                                                                                                                                                                                                                                      | 1      |

| 7.6.2.25<br>7.6.2.25<br>7.6.3<br>7.6.3.1<br>7.6.3.2<br>7.6.3.3                                                                                                | System Handler Control and State Register  Plock generator registers                                                                                                                                                                                                                                                                                                                                                      | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3<br>7.6.3.1<br>7.6.3.2                                                                                                           | System Handler Control and State Register lock generator registers                                                                                                                                                                                                                                                                                                                                                        | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 Q<br>7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6                                                             | System Handler Control and State Register  Plock generator registers                                                                                                                                                                                                                                                                                                                                                      | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 Q<br>7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6                                                             | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 Q<br>7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5                                                                        | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (0<br>7.6.3.1<br>7.6.3.2<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7                                                            | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (0<br>7.6.3.1<br>7.6.3.2<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7                                                            | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 1      |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7                                                      | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       |        |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7<br>Input / (8.1 Por                                  | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 13     |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7<br>Input / (8.1 Por<br>8.1.1 F<br>8.1.2 P                       | System Handler Control and State Register  lock generator registers  CGIMCGA (CG Interrupt Mode Control Register A)  CGIMCGB (CG Interrupt Mode Control Register B)  CGIMCGE (CG Interrupt Mode Control Register F)  CGIMCGF (CG Interrupt Mode Control Register F)  CGICRCG (CG Interrupt Request Clear Register)  CGNMIFLG (NMI Flag Register)  CGRSTFLG (Reset Flag Register)  Dutput Ports  t Functions  unction list | 1:     |

| 7.6.2.24<br>7.6.2.25<br>7.6.3 (7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.6<br>7.6.3.7<br>Input / (8.1 Por<br>8.1.1 F<br>8.1.2 P<br>8.1.3 P | System Handler Control and State Register  lock generator registers                                                                                                                                                                                                                                                                                                                                                       | 1:     |

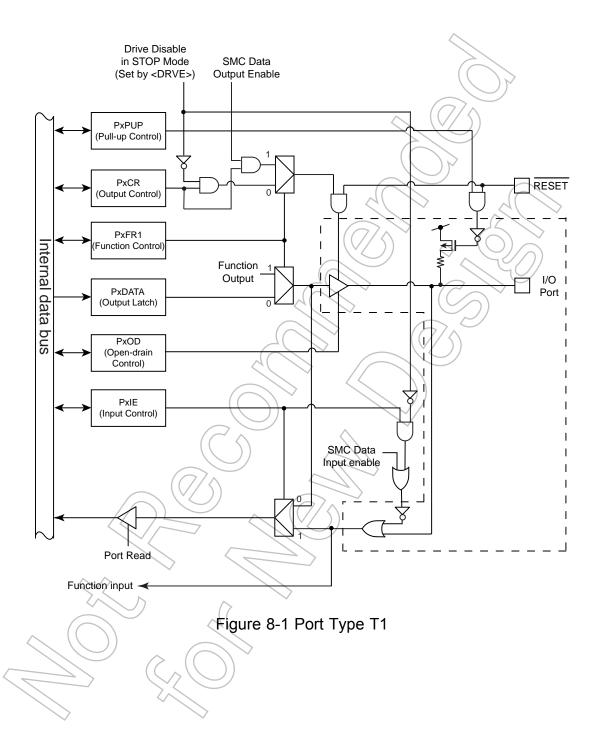

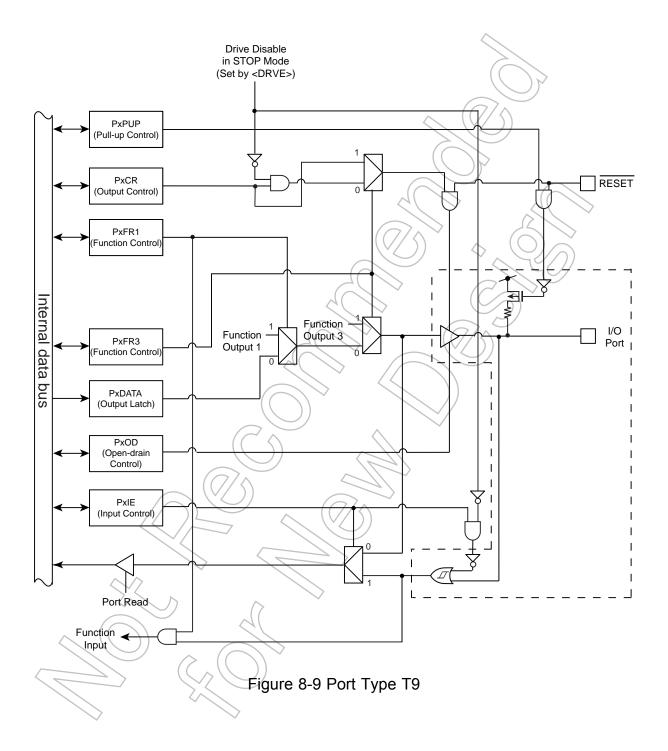

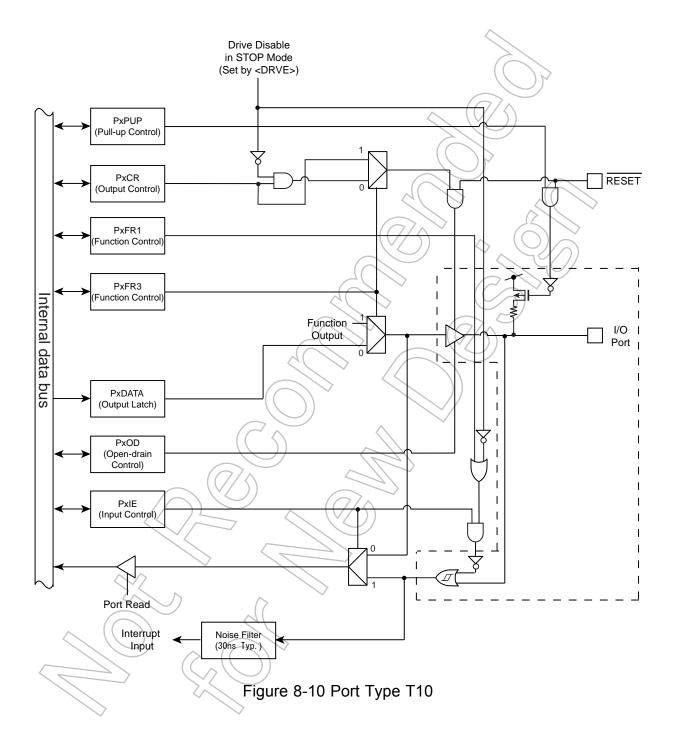

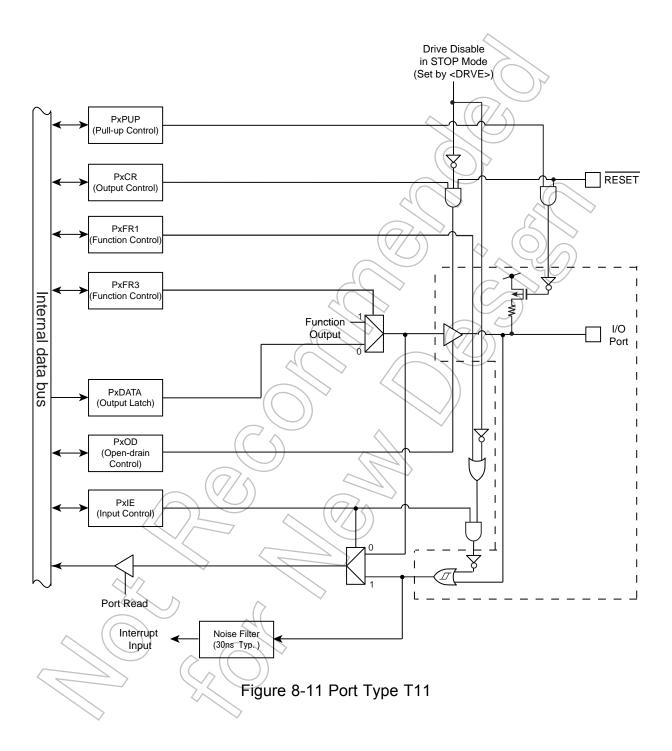

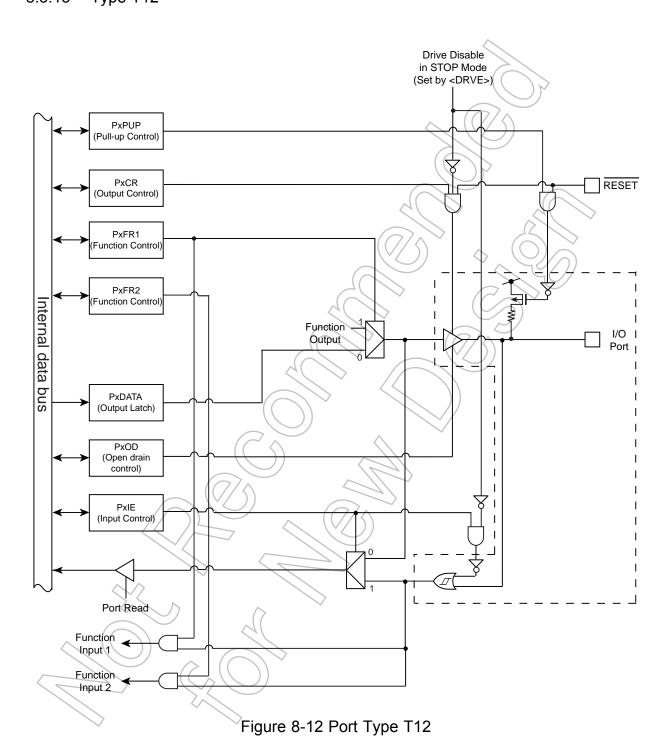

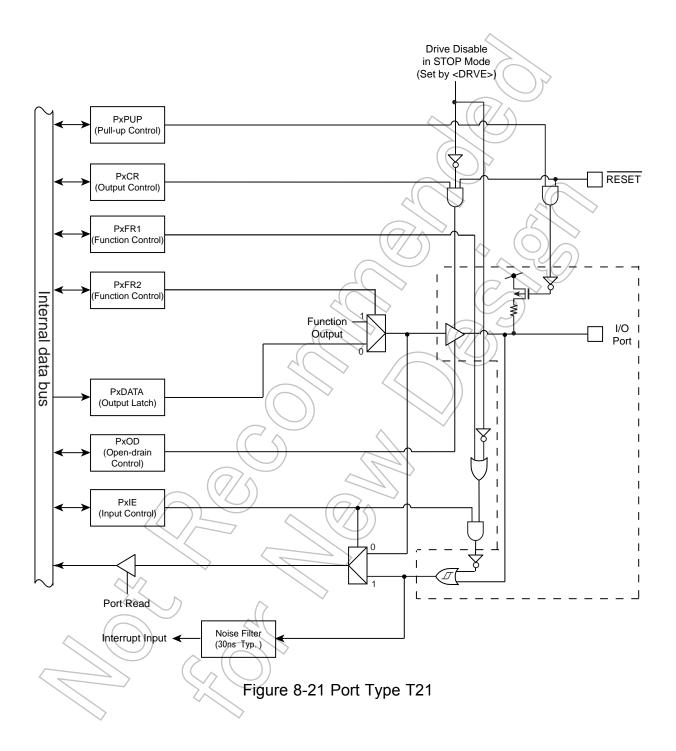

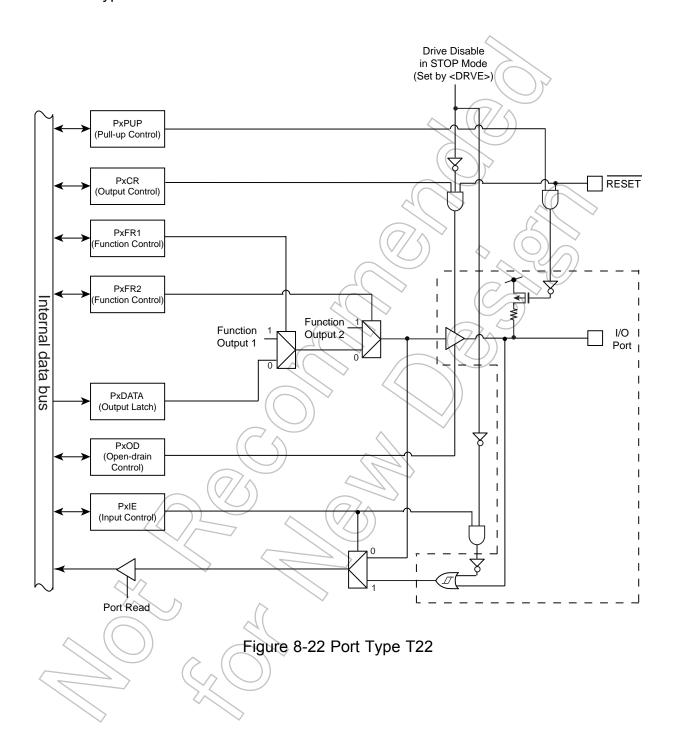

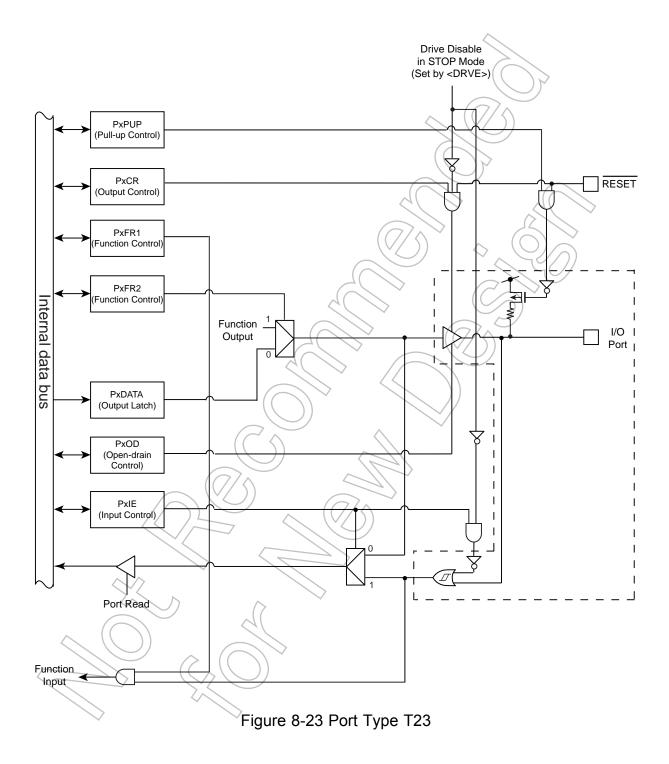

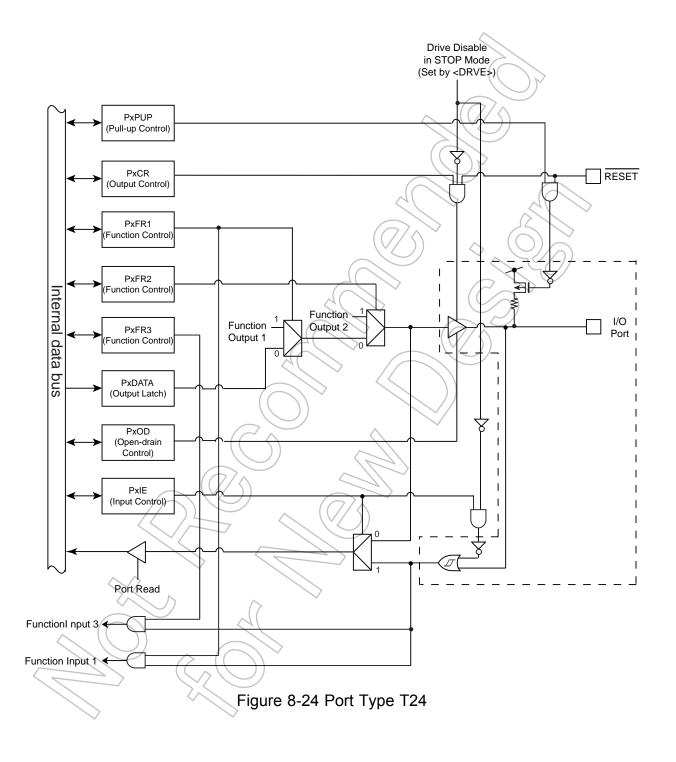

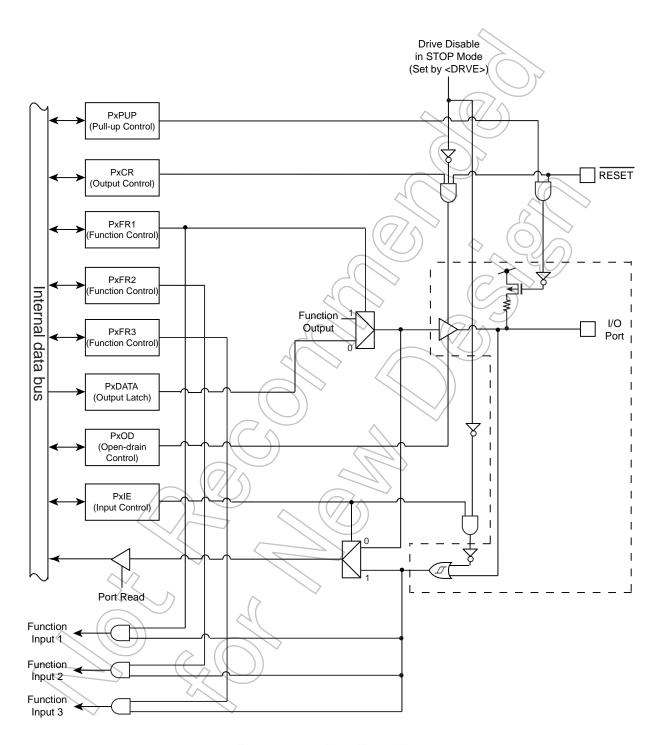

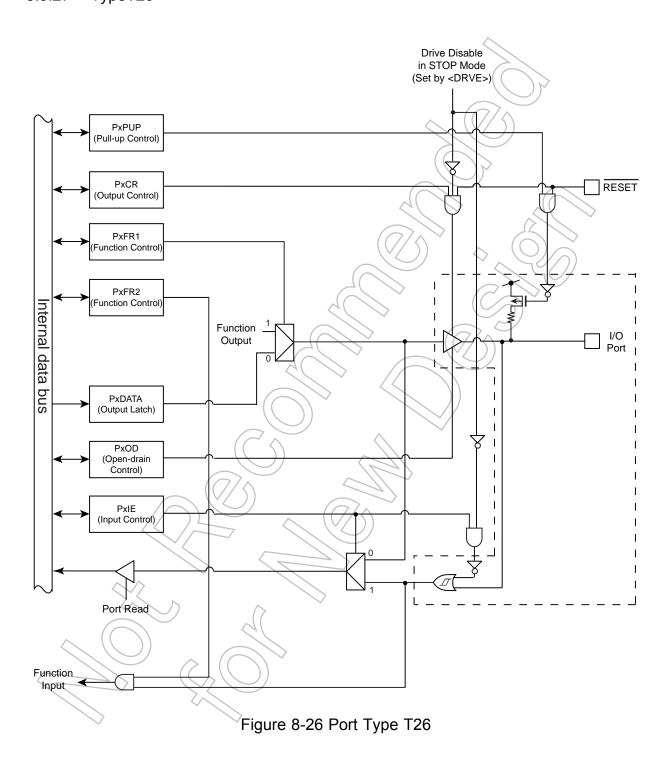

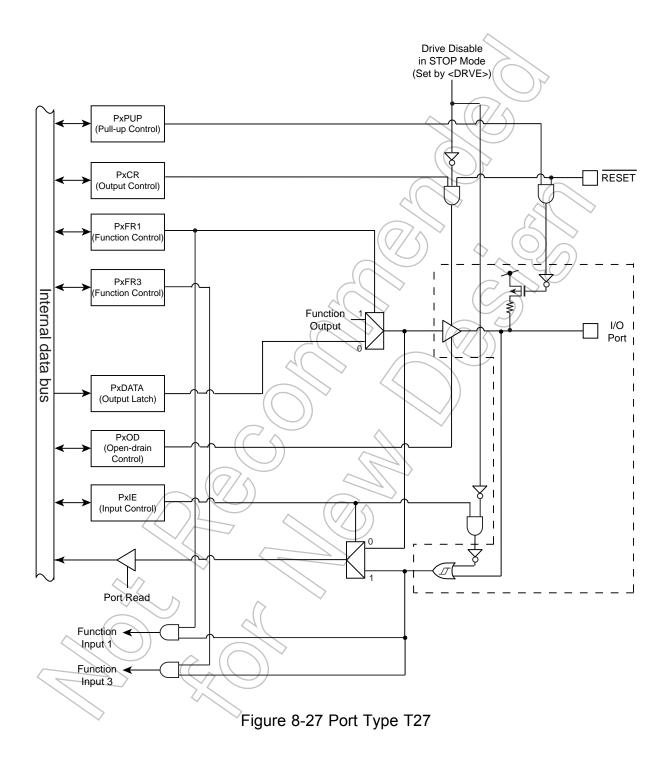

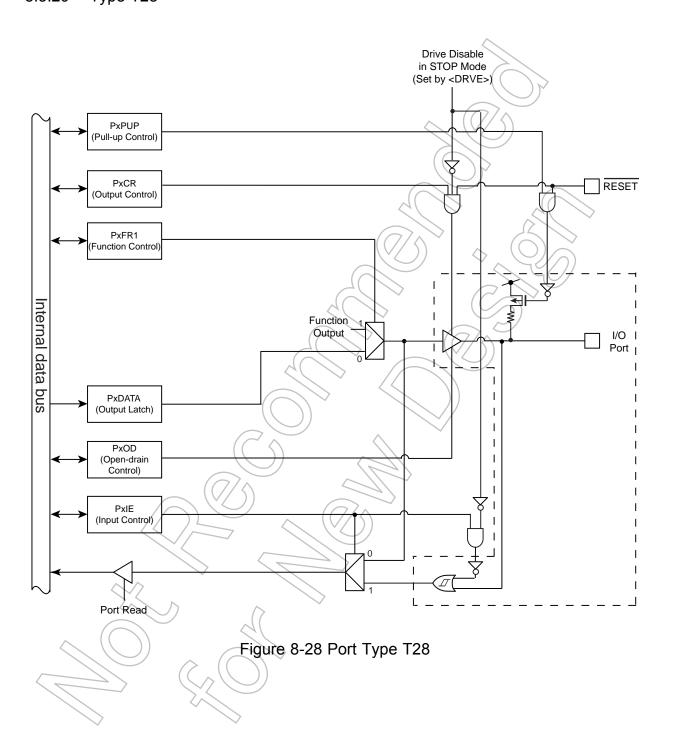

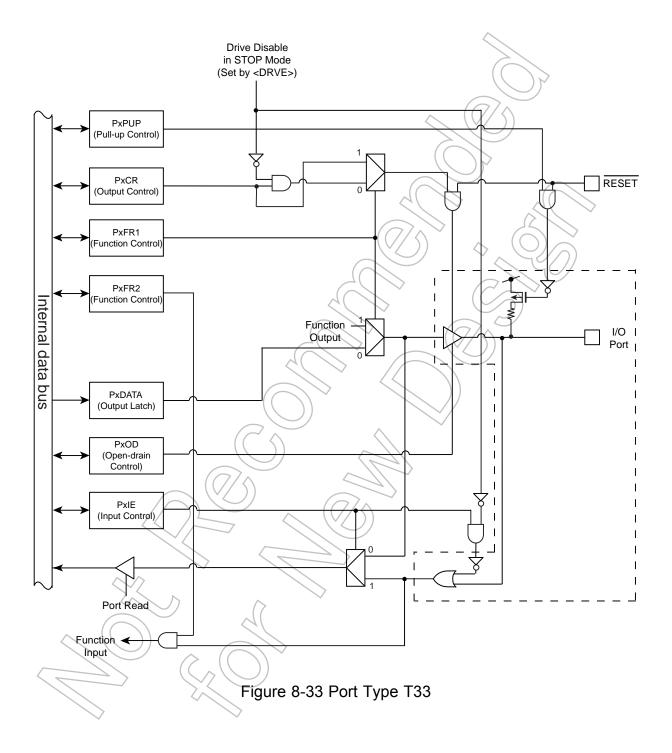

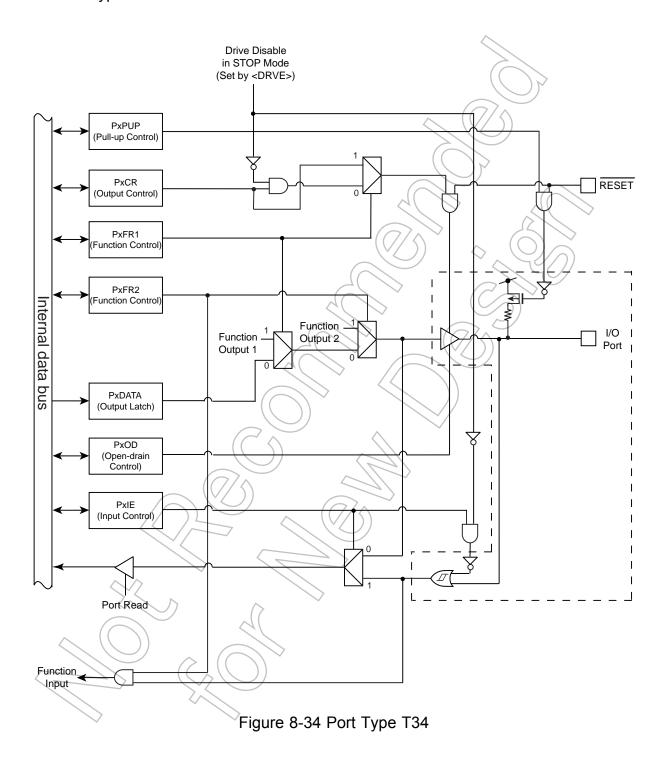

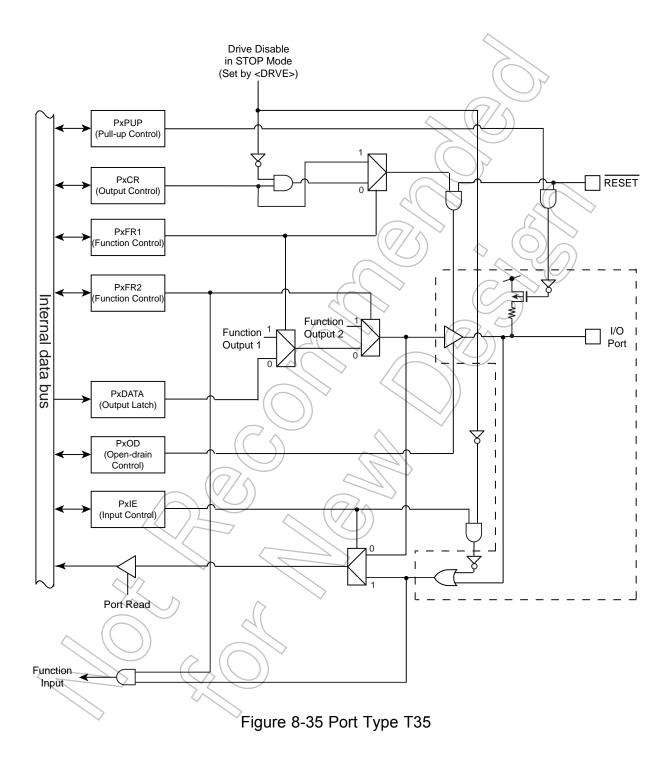

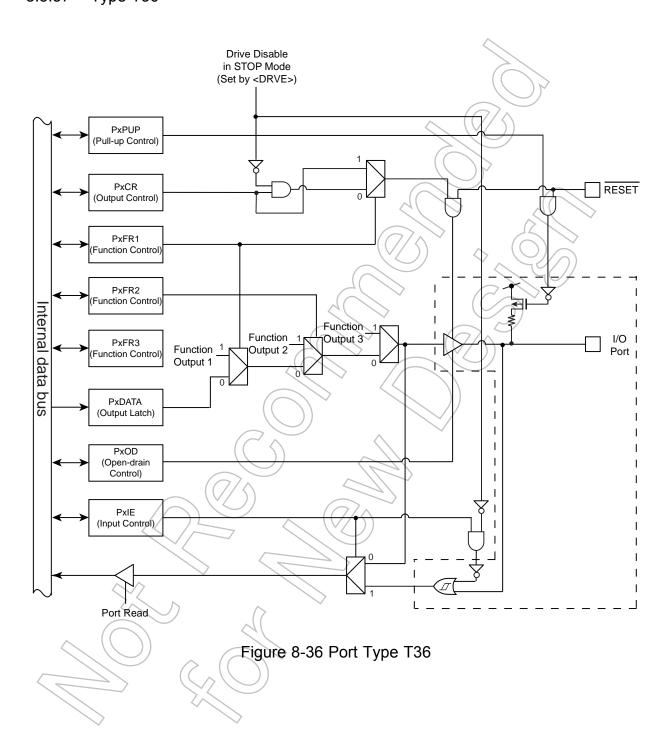

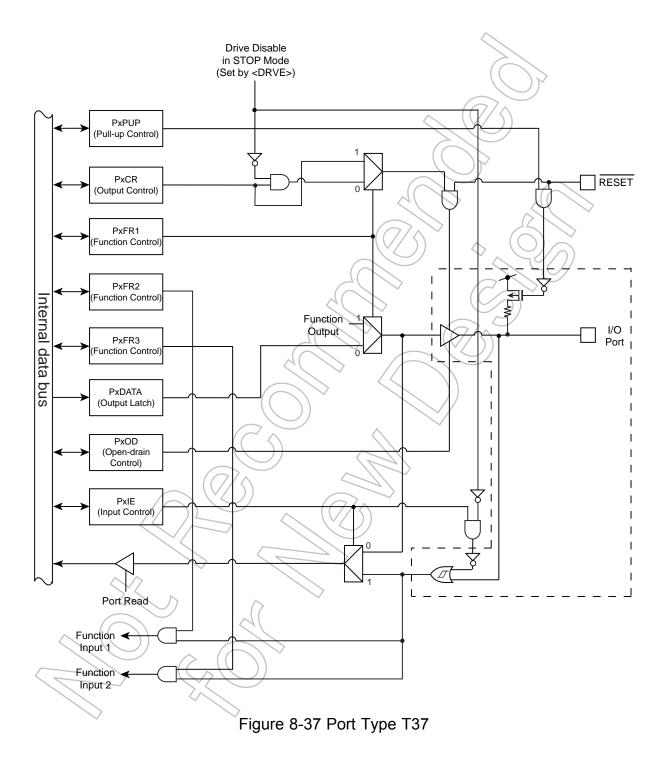

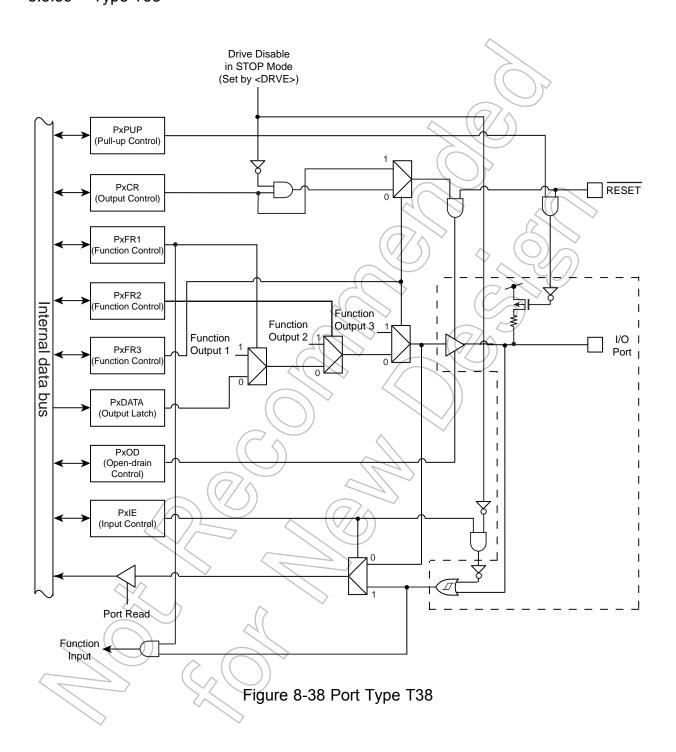

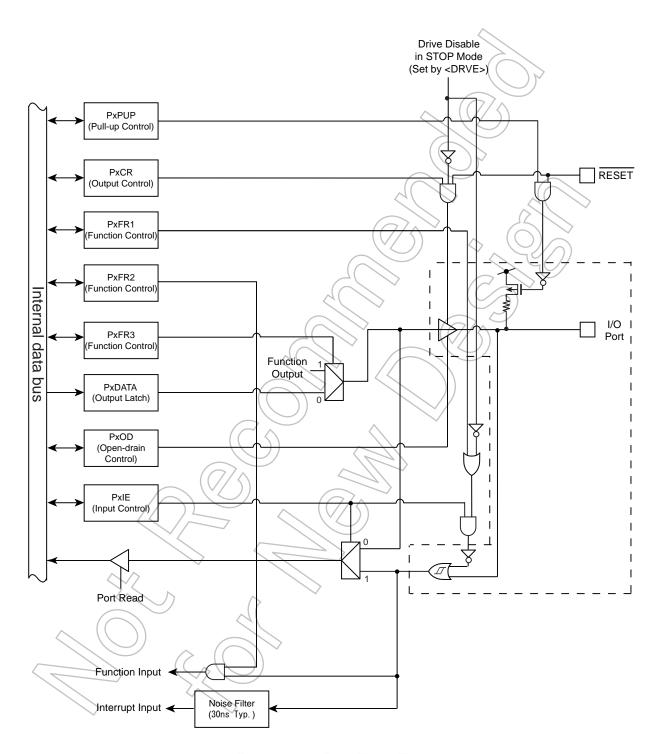

| 8.2.1.1              | Port A Circuit Type                                                               |      |

|----------------------|-----------------------------------------------------------------------------------|------|

| 8.2.1.2              | Port A Register PADATA (Port A data register)                                     |      |

| 8.2.1.3<br>8.2.1.4   | PACR (Port A output control register)                                             |      |

| 8.2.1.5              | PAFR1 (Port A function register 1)                                                |      |

| 8.2.1.6              | PAOD (Port A open drain control register)                                         |      |

| 8.2.1.7              | PAPUP (Port A pull-up control register)                                           |      |

| 8.2.1.8              | PAIE (Port A input control register)                                              |      |

| 8.2.2 Pc             | ort B (PB0 to PB7)                                                                | .131 |

| 8.2.2.1              | Port B Circuit Type                                                               |      |

| 8.2.2.2              | Port B Register                                                                   |      |

| 8.2.2.3              | PBDATA (Port B data register)                                                     |      |

| 8.2.2.4              | PBCR (Port B output control register)                                             |      |

| 8.2.2.5              | PBFR1 (Port B function register)                                                  |      |

| 8.2.2.6              | PBOD (Port B open drain control register)                                         |      |

| 8.2.2.7<br>8.2.2.8   | PBPUP (Port B pull-up control register) PBIE (Port B input control register)      |      |

|                      | ort E (PE0 to PE7)                                                                | .136 |

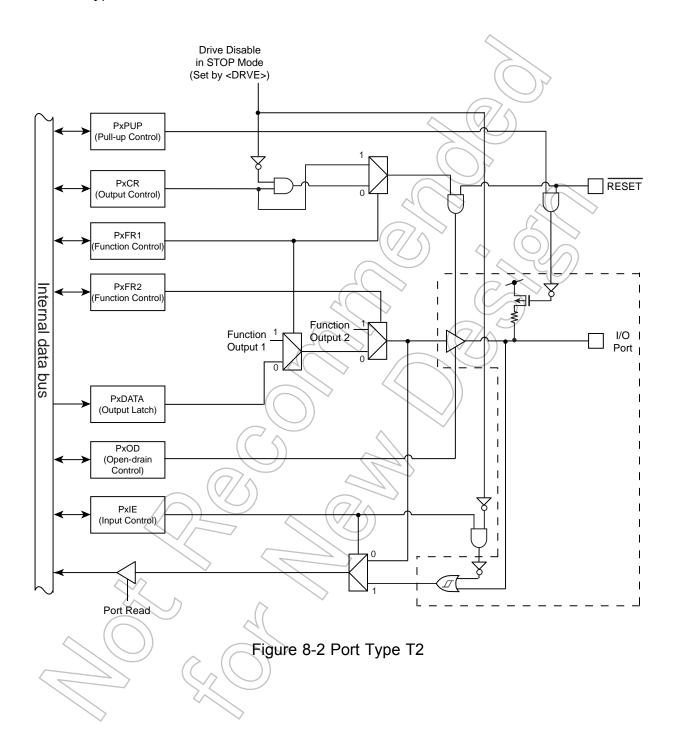

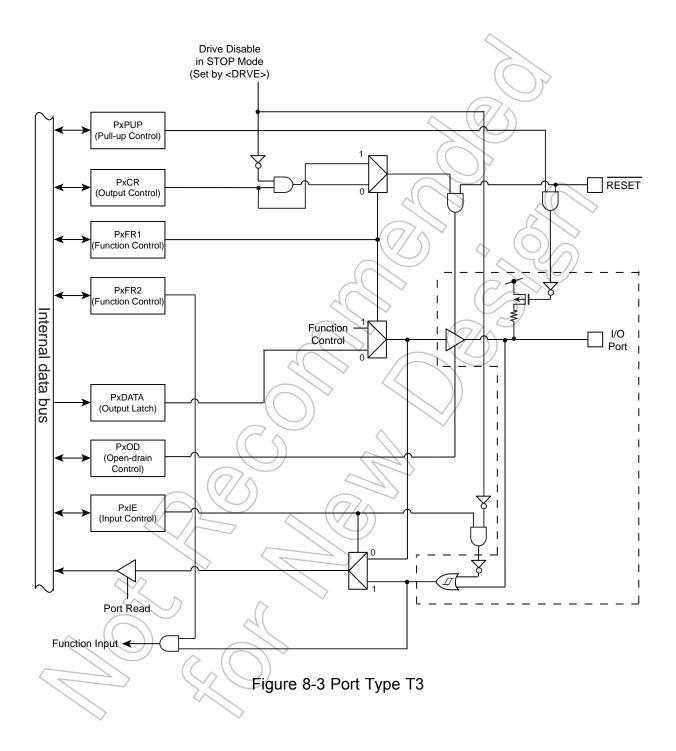

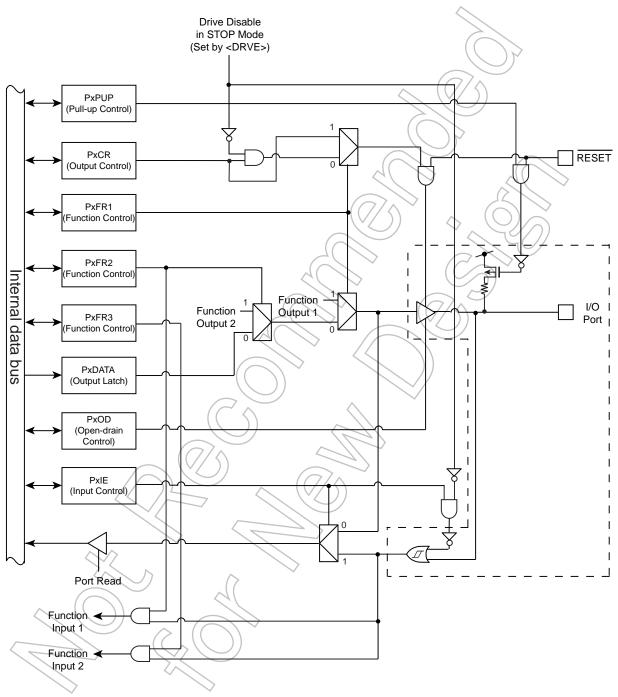

| 8.2.3.1              | Port E Circuit Type                                                               | .130 |

| 8.2.3.2              | Port E register                                                                   |      |

| 8.2.3.3              | PEDATA (Port E data register)                                                     |      |

| 8.2.3.4              | PECR (Port E output control register)                                             |      |

| 8.2.3.5              | PEFR1 (Port E function register 1)                                                |      |

| 8.2.3.6              | PEFR2 (Port E function register 2)                                                |      |

| 8.2.3.7              | PEFR3 (Port E function register 3)                                                |      |

| 8.2.3.8              | PEOD (Port E open drain control register)                                         |      |

| 8.2.3.9              | PEPUP (Port E pull-up control register) PEIE (Port E input control register)      |      |

| 8.2.3.10             | ort F (PF0 to PF4)                                                                | .142 |

| 8.2.4 Pc<br>8.2.4.1  | Port F Circuit Type                                                               | .142 |

| 8.2.4.1              | Port F Register                                                                   |      |

| 8.2.4.3              | PFDATA (Port F data register)                                                     |      |

| 8.2.4.4              | PFCR (Port F output control register)                                             |      |

| 8.2.4.5              | PFFR1 (Port F function register 1)                                                |      |

| 8.2.4.6              | PFOD (Port F open drain control register)                                         |      |

| 8.2.4.7              | PFPUP (Port F pull-up control register)                                           |      |

| 8.2.4.8              | PFIE (Port F input control register)                                              |      |

|                      | ort G (PG0 to PG7)                                                                | .147 |

| 8.2.5.1              | Port G Circuit Type                                                               |      |

| 8.2.5.2<br>8.2.5.3   | Port G register PGDATA (Port G data register)                                     |      |

| 8.2.5.4              | PGCR (Port G output control register)                                             |      |

| 8.2.5.5              | PGFR1 (Port G function register 1)                                                |      |

| 8.2.5.6              | PGFR2 (Port G function register 2)                                                |      |

| 8.2.5.7              | PGFR3 (Port G function register 3)                                                |      |

| 8.2.5.8              | PGOD (Port G open drain control register)                                         |      |

| 8.2.5.9              | PGPUP (Port G pull-up control register)                                           |      |

| 8.2.5.10<br>8.2.6 Pc |                                                                                   | 151  |

| 8.2.6.1              | ort I (PIO to PII)                                                                | .134 |

| 8.2.6.2              | Port I register                                                                   |      |

| 8.2.6.3              | PIDATA (Port I data register)                                                     |      |

| 8.2.6.4              | PICR (Port I output control register)                                             |      |

| 8.2.6.5              | PIFR1 (Port/I function register 1)                                                |      |

| 8.2.6.6<br>8.2.6.7   | PIOD (Port I open drain control register) PIPUP (Port I pull-up control register) |      |

| 8.2.6.8              | PITE (Port I input control register)                                              |      |

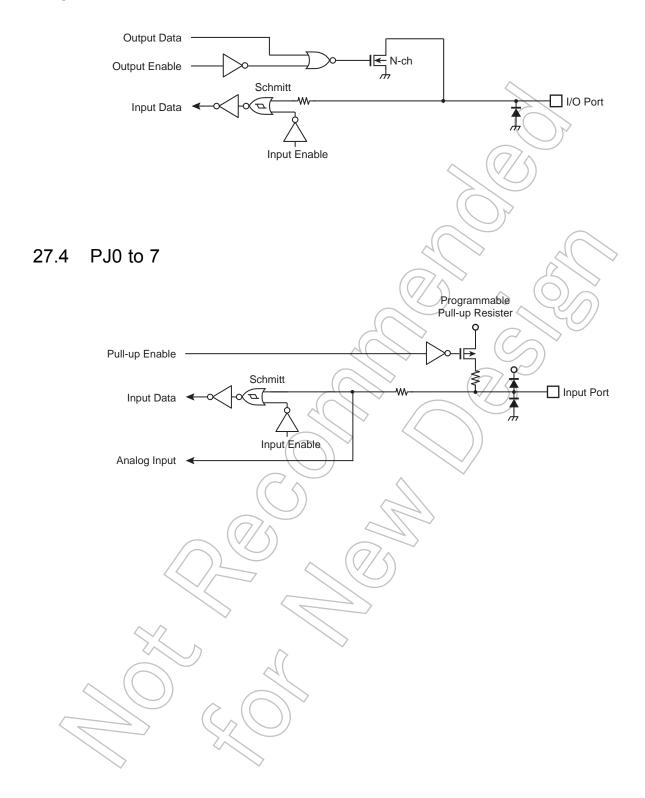

|                      | ort J (PJO to PJ7)                                                                | 160  |

| 8.2.7.1              | Port J Circuit Type                                                               | .100 |

| 8.2.7.2              | Port J register                                                                   |      |

| 8.2.7.3              | PJDATA (Port J data register)                                                     |      |

| 8.2.7.4              | PJFR2 (Port J function register 1)                                                |      |

| 8.2,7.5              | PJPUP (Port J pull-up control register)                                           |      |

| 8.2.7.6              | PJIE (Port J input control register)                                              |      |

|                      | ort L (PL0 to PL7)                                                                | .164 |

| 8.2.8.1              | Port L Circut Type                                                                |      |

| 8.2.8.2              | Port L register                                                                   |      |

| 8.2.8.3<br>8.2.8.4   | PLDATA (Port L data register) PLCR (Port L output control register)               |      |

| 8.2.8.4<br>8.2.8.5   | PLFR1 (Port K function register 1)                                                |      |

| 8.2.8.6              | PLFR2 (Port L function register 2)                                                |      |

| 8.2.8.7              | PLFR3 (Port L function register 3)                                                |      |

| 8.2.8.8              | PLOD (Port L open drain control register)                                         |      |

| 8.2.8.9              | PLPUP (Port L pull-up control register)                                           |      |

| 8.2.8.10             | • •                                                                               |      |

| 8.2.9 Pc             | ort M (PM0 to PM7)                                                                | .170 |

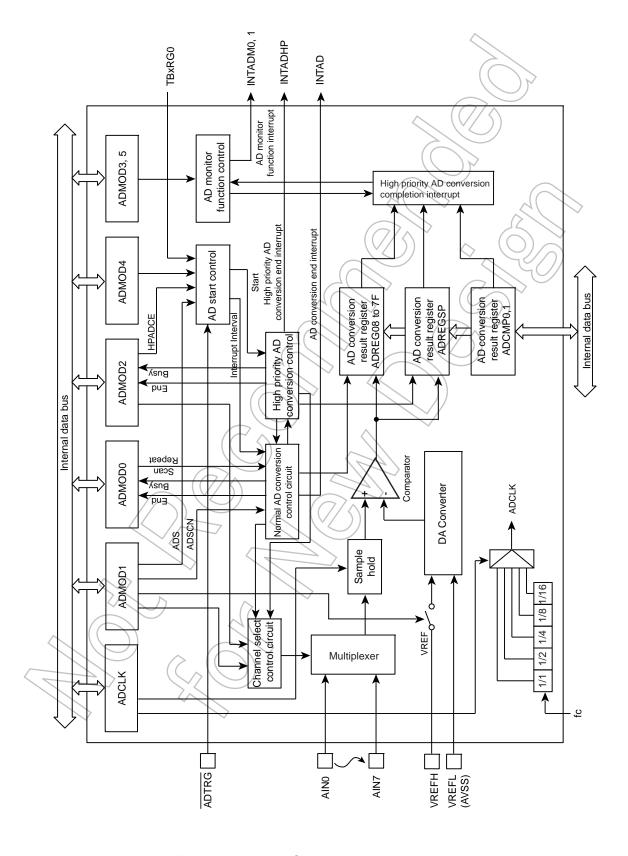

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Port Circuit Type                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 8.2.9.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 8.2.9.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 8.2.9.4<br>8.2.9.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 8.2.9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | `                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |