### THAT1570

### **FEATURES**

- Low Noise:

- 1 nV//Hz input noise (60 dB gain) • Low THD+N:

- 0.0003% ≤ 30 dB gain 0.0008% @ 40 dB gain

- Low Current: 7.5 mA typ

- Wide Bandwidth: 4.2MHz @40dB gain

- High Slew Rate: 53 V/µs

- Wide Signal Swing: >28.7dBu (±18V supplies)

- Gain adjustable from 0 to >60 dB

- Differential output

- Small 4 x 4mm QFN16 package

- Mates with THAT5171 Digital Preamplifier Controller IC

# APPLICATIONS

- Microphone Preamplifiers

- Digitally-Controlled Microphone Preamplifiers

- Differential Low-Noise Preamplifiers

- Differential Summing Amplifiers

- Differential Variable-Gain Amplifiers

- Moving-Coil Transducer Amplifiers

- Line Input Stages

- Audio

- Sonar

- Instrumentation

# Description

The THAT1570 is a versatile, high performance current-feedback amplifier suitable for differential microphone preamp and bus summing applications. The IC comes in a small QFN package, which saves PCB space over discrete and other integrated solutions.

Gain is adjusted via three external resistors (R<sub>A</sub>, R<sub>B</sub>, and R<sub>G</sub>), making it possible to optimize noise over a wide range of gains. The 1570 supports the traditional approach to gain control (viz., THAT's 1510 or 1512) by fixing R<sub>A</sub> and R<sub>B</sub>, and varying R<sub>G</sub> to control gain. However, the 1570 also supports varying all three resistors simultaneously with a dual-gang potentiometer or a switched resistor network. This flexible approach enables the designer to optimize noise over a wider range of gains than is possible with fixed R<sub>A</sub> and R<sub>B</sub>.

The 1570's differential output simplifies connection to differential input devices such as A/D converters. The part operates from as little as  $\pm 5V$  up through  $\pm 18V$  supplies. Running on  $\pm 18V$  supplies, at unity gain, the part accepts >+28dBu input signals.

The 1570 is designed to mate perfectly with THAT's 5171 Digital Preamplifier Controller IC. The part-pair comprises an optimized, digitally controlled audio preamplifier.

Designed from the ground up in THAT's complementary bipolar dielectric-isolation process and including laser-trimmed Si-Chrome thin-film resistors, the 1570 improves on existing integrated microphone preamps by offering more versatile gain configuration, lower noise at low gains, higher slew rate, and lower distortion.

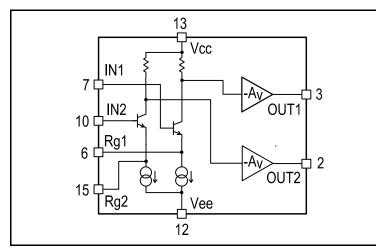

Figure 1. THAT1570 Block Diagram

| Pin Name        | QFN Pin     |

|-----------------|-------------|

| N/C             | 1           |

| OUT2            | 2           |

| OUT1            | 3           |

| N/C             | 4           |

| N/C             | 5           |

| Rg1             | 6           |

| IN1             | 7           |

| N/C             | 8           |

| N/C             | 9           |

| IN2             | 10          |

| N/C             | 11          |

| V <sub>EE</sub> | 12          |

| V <sub>cc</sub> | 13          |

| N/C             | 14          |

| Rg2             | 15          |

| N/C             | 16          |

| V <sub>EE</sub> | Thermal Pad |

Table 1. Pin Assignments

# SPECIFICATIONS<sup>1</sup>

# Absolute Maximum Ratings<sup>2,3</sup>

| Supply Voltage ( $V_{CC}$ - $V_{EE}$ )     |  |  |  |  |

|--------------------------------------------|--|--|--|--|

| Maximum Input Voltage (V <sub>IMax</sub> ) |  |  |  |  |

| Storage Temperature Range ( $T_{STG}$ )    |  |  |  |  |

40 V  $V_{CC}$ +0.5V to  $V_{EE}$ -0.5V -40 to +125 °C Operating Temperature Range (T<sub>OP</sub>) Output Short-Circuit Duration (t<sub>SH</sub>) Junction Temperature (T<sub>JMAX</sub>)

-40 to +85 °C Continuous +125 °C

|                                    | Elec                               | ctrical Characteristics <sup>2</sup>                                                 | 2,4,3                 |                                           |                       |                                      |

|------------------------------------|------------------------------------|--------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|-----------------------|--------------------------------------|

| Parameter                          | Symbol                             | Conditions                                                                           | Min                   | Тур                                       | Max                   | Units                                |

| Power Supply                       |                                    |                                                                                      |                       |                                           |                       |                                      |

| Supply Voltage                     | $V_{CC}; \text{-}V_{EE}$           | Referenced to GND                                                                    | 5                     | _                                         | 18                    | V                                    |

| Supply Current                     | I <sub>CC</sub> ; -I <sub>EE</sub> | No Signal                                                                            | —                     | 7.5                                       | 10                    | mA                                   |

| Input Characteristics              |                                    |                                                                                      |                       |                                           |                       |                                      |

| Input Bias Current                 | I <sub>B</sub> N                   | lo signal; either input connected to GN                                              | 1D —                  | 6.4                                       | 22                    | μA                                   |

| Input Offset Current               | $I_{B-OFF}$                        | No signal;                                                                           | -2.2                  |                                           | +2.2                  | μA                                   |

| Differential Input Offset Voltage  | V <sub>os</sub>                    | No signal, Inputs connected to GND<br>0 dB gain<br>+60 dB gain                       | -5.25<br>-255         | _                                         | +5.25<br>+255         | mV<br>μV                             |

| Input Common Mode Voltage Range    | e V <sub>IN_CM</sub>               | Common Mode                                                                          | V <sub>EE</sub> + 4   | _                                         | V <sub>cc</sub> - 4   | V                                    |

| Input Impedance                    | Z <sub>IN_DIFF</sub>               | Differential<br>≥ 20 dB gain<br>40 dB gain<br>60 dB gain<br>Common Mode<br>All gains | <br><br>              | 58  1<br>58  3.5<br>57  28.7<br>29.4  1.4 |                       | MΩ  pF<br>MΩ  pF<br>MΩ  pF<br>MΩ  pF |

| Maximum Differential Input Level   | $V_{\text{IN-BAL}}$                | $R_G = \infty$                                                                       | _                     | 26.8                                      | _                     | dBu                                  |

| Output Characteristics             |                                    |                                                                                      |                       |                                           |                       |                                      |

| Total Differential Output Offset   |                                    | G = gain                                                                             | -(5+0.25*G            | ) —                                       | (5+0.25*G)            | mV                                   |

| Common Mode Output Voltage         | V <sub>OSCM</sub>                  | No signal; IN1, IN2 connected to GNE                                                 | D —                   | -610                                      | _                     | mV                                   |

| Maximum Single Output Voltage      | V <sub>OUT-SINGL</sub>             | <sub>E</sub> R <sub>L</sub> = 2 kΩ                                                   | V <sub>EE</sub> + 2.4 | _                                         | V <sub>cc</sub> - 1.4 | V                                    |

| Differential Short Circuit Current | I <sub>SC</sub>                    | $R_L = 0 \Omega$ ; Cold start<br>$R_L = 0 \Omega$ ; Continuous                       | _                     | ± 42<br>± 28                              | _                     | mA<br>mA                             |

| Maximum Capacitive Load            | $C_{\text{L}\text{MAX}}$           | Over entire temperature range<br>Stable operation 50% overshoot                      | _                     | <br>400                                   | 100                   | pF<br>pF                             |

|                                    | Vout                               | $R_1 = 2 k\Omega$                                                                    | 26.6                  | _                                         | _                     | dBu                                  |

1. All specifications are subject to change without notice.

2. Unless otherwise noted,  $T_{A=2}$ 5%C,  $V_{cc}$ =+15V. 3. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. 4. 0 dBu = 0.775 Vrms

5. Unless otherwise noted,  $R_A = R_B = 2.21 \text{ k}\Omega$ ;  $C_L = 10 \text{ pF}$

|                                | Electrica         | l Characteristics (con'                                                                                                                                                         | <b>t)</b> <sup>1,3,4</sup> | ,5                                           |                  |                                                |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------|------------------|------------------------------------------------|

| Parameter                      | Symbol            | Conditions                                                                                                                                                                      | Min                        | Тур                                          | Max              | Units                                          |

| AC Characteristics             |                   |                                                                                                                                                                                 |                            |                                              |                  |                                                |

| Gain Equation                  | $G_{DIFF}$        | Differential in to differential out See Figure 2. $(R_G = R_{GV} + R_{GF})$                                                                                                     | 1 +                        | + (R <sub>A</sub> + R <sub>B</sub> ) /       | / R <sub>G</sub> |                                                |

| Feedback Impedance             | $R_A, R_B$        |                                                                                                                                                                                 | 2                          |                                              |                  | kΩ                                             |

| Differential Gain              | GDIFF             | Programmed by $R_A$ , $R_B$ , $R_G$                                                                                                                                             | 0                          | _                                            | 70               | dB                                             |

| Power Supply Rejection Ratio   | PSRR              | $V_{CC} = -V_{EE}; \pm 5V \text{ to } \pm 20V$<br>0 dB gain<br>20 dB gain<br>40 dB gain<br>60 dB gain                                                                           | <br>                       | 97<br>105<br>105<br>105                      |                  | dB<br>dB<br>dB<br>dB                           |

| Bandwidth -3dB                 | f. <sub>3dB</sub> | Small signal<br>$\leq 10$ dB gain<br>20 dB gain<br>40 dB gain<br>50 dB gain<br>60 dB gain<br>Small signal; $R_G = \infty$<br>$R_A = R_B = 2 k\Omega$<br>$R_A = R_B = 5 k\Omega$ |                            | 12<br>10.5<br>4.2<br>1.7<br>600<br>14<br>4.2 | <br><br>         | MHz<br>MHz<br>MHz<br>MHz<br>kHz<br>MHz<br>MHz  |

| Slew Rate                      | SR                | $R_{A} = R_{B} = 10 \text{ k}\Omega$ $V_{OUT} = 10V_{P-P}; R_{L}=2k\Omega \text{ ; } C_{L}=100\text{pF}$ All gains                                                              | _                          | 1.9<br>53                                    |                  | MHz<br>V/μs                                    |

| Total Harmonic Distortion      | THD + N           | V <sub>OUT</sub> = 5V <sub>RMS</sub> ; f=1kHz; BW=22kHz<br>0 dB gain<br>20 dB gain<br>40 dB gain<br>60 dB gain                                                                  |                            | 0.0003<br>0.0003<br>0.0008<br>0.006          |                  | ν/μs<br>%<br>%<br>%                            |

| Equivalent Input Noise Voltage | e <sub>n</sub> Ir | nputs connected to GND; BW=22kHz<br>0 dB gain<br>6 dB gain<br>20 dB gain<br>40 dB gain<br>60 dB gain                                                                            |                            | 18.5<br>10.4<br>3.5<br>1.4<br>1              | <br>             | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz |

| Equivalent Input Noise Current | i <sub>N</sub>    | f=1kHz; BW=22kHz; 60 dB gain                                                                                                                                                    | _                          | 2                                            | _                | pA/√Hz                                         |

| Noise Figure                   | NF                | 60 dB gain; R <sub>s</sub> = 150 Ω                                                                                                                                              | _                          | 1.5                                          |                  | dB                                             |

### Applications

### **Gain Setting**

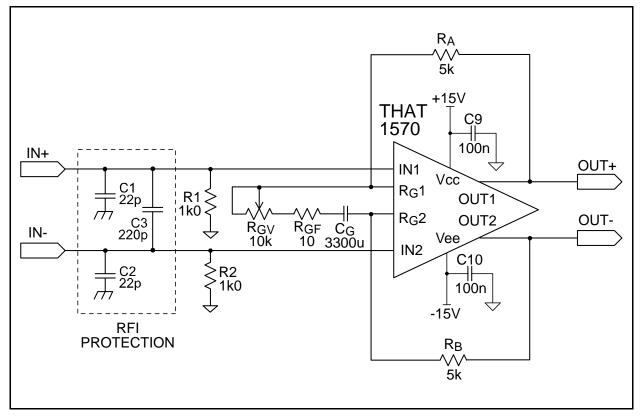

Three external resistors ( $R_A$ ,  $R_B$ , and  $R_G$ ) set the gain of the THAT1570. Gain follows the formula:

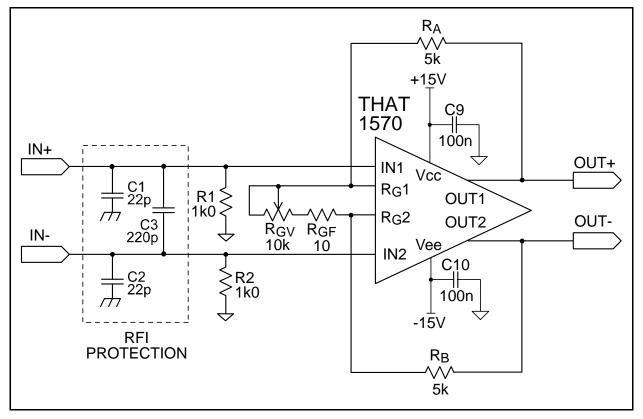

$A_V = 1 + \frac{R_A + R_B}{R_G}$ ; where  $A_v$  is the (differential) voltage gain of the part (See Figure 2, in which  $R_G$  is made up of a fixed ( $R_{GF}$ ) portion and a variable ( $R_{GV}$ ) portion).

Because all three resistors are external, the designer is free to select them for best noise performance at the desired gain setting(s). Note, however, that as with any current-feedback amplifier, the part's bandwidth will vary with  $R_A$ . The 1570 is stable with  $R_A$  values of  $2k\Omega$  or larger; bandwidth decreases with increasing  $R_A$ .

The part's minimum gain is unity (0dB). This occurs with  $R_G$  open. Maximum gain depends on the required bandwidth. Full audio bandwidth is maintained to well beyond 60dB gain.

Other integrated mic preamps which include internal resistors for  $R_A$  and  $R_B$  (e.g., the THAT 1510 and 1512) allow gain to be varied using one singlegang potentiometer. The 1570 offers a similar hookup, by fixing  $R_A$  and  $R_B$  and varying  $R_G$ . This is shown in the circuit of Figure 2. In such applications, designers should take care in specifying the pot's element construction to avoid excess noise. The potentiometer taper will set the circuit's characteristic of gain vs. pot rotation. Typically, reverse log (audio) taper elements offer the desired behavior in which gain increases with clockwise rotation (and lower values for  $R_{GV}$ ).

Overall gain accuracy depends on the tolerance of the resistors, including especially the pot  $(R_{GV})$  which dominates  $R_G$ . Theoretically, when  $R_{GV}$  is zero, the gain is determined by RA, RB, RGF alone. End resistance ("hop off") will alter the actual gain; reducing  $R_{GF}$  by the amount of end resistance may be appropriate, especially if the end resistance is consistent. It will be easier to maintain consistent gain at the highgain end of the pot travel at higher values for  $R_A$  and  $R_{\rm B}$ , since this makes the value of  $R_{\rm G}$  required proportionately larger for any given gain. The circuit of Figure 2 shows 5 k $\Omega$  resistors for R<sub>A</sub> and R<sub>B</sub>, so for 60 dB gain,  $R_G = 10 \Omega$ . Its noise performance is very good at 60 dB gain (1.1 nV/Hz, or -133.9 dBu with a)zero ohm input termination, or 2.27 nV/ $\sqrt{Hz}$ , or -127.7 dBu with a more realistic 150  $\Omega$  input termination). At minimum gain (6 dB) its noise performance is still good (21.3 nV/ $\sqrt{Hz}$ ), or -108.3 dBu with a zero ohm input termination.

One disadvantage of the circuit of Figure 2 is that differential dc offset at the 1570 output will vary with gain. At 0 dB gain, the 1570's worst-case differential output offset voltage is  $\sim$ 5 mV, while at 60dB gain,

Figure 2. 1570 Typical Application Circuit Using Single-Gang Pot for Gain Control

this is  $\sim 255$  mV. As well, if the wiper of the pot loses contact with the element, gain will abruptly change to unity, with an attendant change in dc offset as well. To minimize dc offsets, consider the circuits of Figures 5 and 7, which ac couple R<sub>G</sub>.

#### **Improving Noise Performance**

The 1570 has extremely low input voltage noise. To achieve this feature, the input transistors are large-geometry NPN types, biased at high ( $\sim$ 1 mA) collector current. In order to maintain the low voltage-noise performance of the 1570, designers should take care not to present too high a source impedance to the input pins. A high impedance generates its own self-noise when not shunted by the impedance of the source connected to the input pins.

Additionally, the input transistors' base current, and any noise in that base current, must be drawn through the bias network ( $R_1$  and  $R_2$  in Figure 2) connected to IN1 and IN2 (which connect to the bases of the input transistors). Any input current noise will be drawn across the source impedance (as seen by the inputs), which turns it into a voltage that is amplified by the gain of the device. Too high a source impedance can easily spoil the noise of the device. The  $1k\Omega$  resistors used at  $R_1$  and  $R_2$  in Figure 2 provide a low source impedance for the 1570 even when the input is open, and provide a 2  $k\Omega$  (differential) load for the microphone. Higher source impedances will increase noise seen (and heard!) with open inputs.

One disadvantage of the single-pot approach is that noise at low gains is dominated by the noise of resistors  $R_A$  and  $R_B$ . For the circuit of Figure 2, the equivalent input noise at 6 dB gain (the minimum pot setting) is ~21.3 nV/\Hz, or -108.3 dBu. Much lower noise (~ 11.8 nV/\Hz) can be achieved if  $R_A$  and  $R_B$  are reduced to ~2.5 k\Omega, but to achieve 60 dB gain, this requires  $R_G$  to be = 5  $\Omega$ . (This analysis also assumes  $R_{GV} = 5 \ k\Omega$ .)

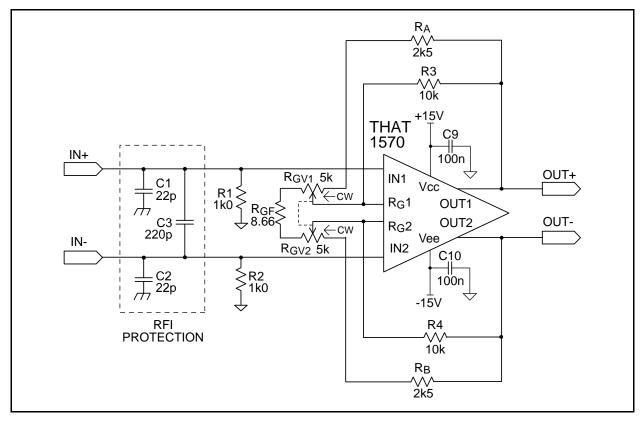

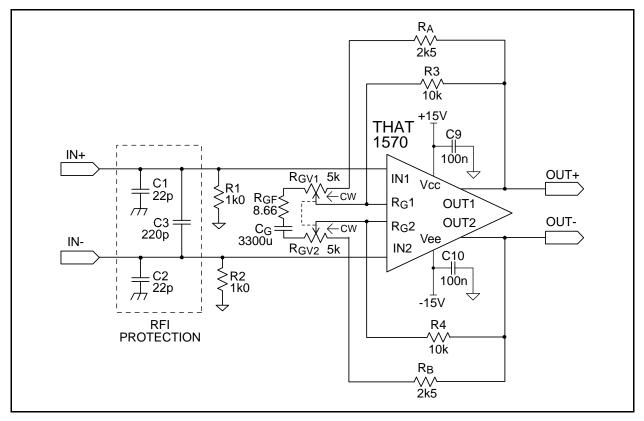

An alternative offered by the 1570 (and not by preamps with internal  $R_A$  and  $R_B$ ) is that all three resistors may be varied at once. See the circuit of Figure 3, which uses a dual-gang potentiometer as the variable element.

In Figure 3, high gain occurs by decreasing  $R_{G}$  while simultaneously increasing  $R_{A}$  and  $R_{B}$ . The advantage of this approach is that  $R_{A}$  and  $R_{B}$  will naturally be lower for low gains, without requiring such a low value for  $R_{G}$  to achieve high gains. In this circuit, 60 dB gain occurs with  $R_{G}$ = 8.66  $\Omega$ , and EIN is 1.1 nV/\Hz, or -133.9 dBu with a zero ohm input termination. With a 150  $\Omega$  resistor, is 2 nV/\Hz or  $\sim$  -128.7 dBu.

This circuit's minimum gain is 3dB, where  $R_{\rm GV}$  is fully CCW. At this gain, the input-referred noise is  ${\sim}13~nV\!/\!{\rm Hz}$ , or -112.5 dBu with a shorted input, and

Figure 3. 1570 Typical Application Circuit Using Dual-Gang Pot for Gain Control

is essentially no different with a 150  $\Omega$  input termination. This is about 4.2 dB better than the circuit of Figure 2 at its minimum gain (6dB). Note also that at the minimum +3 dB gain and ±18 V rails, the circuit of Figure 3 can accept up to +25.7 dBu input signals without clipping. This offers more headroom than the circuit of figure 2.

Of course, other minimum and maximum gains can be accommodated by varying the resistors at  $R_A$ ,  $R_B$ ,  $R_{GV}$ , and  $R_{GF}$ .

For variable-gain applications where gain accuracy is important, THAT recommends using discrete, switched resistors for  $R_A$ ,  $R_B$  and  $R_G$ . With switched resistors, it becomes even easier to vary all three resistors to optimize noise.

As with the circuit of Figure 2,  $R_G$  in Figure 3 is dc coupled. This means that the differential output offset voltage will vary with gain. Also, if the wiper of either half of the gain pot loses contact with the element, gain, and output offset, will change abruptly.  $R_3$  and  $R_4$  help this situation by minimizing the change in dc offset generated by the 1570's input bias current (drawn across the combination of  $R_3$  in parallel with the series combination of  $R_A$  and part of  $R_{GV1}$ , or the other mirror half). Again, for best dc performance, consider the circuits of Figures 6 and 8 which ac-couple  $R_G$ .

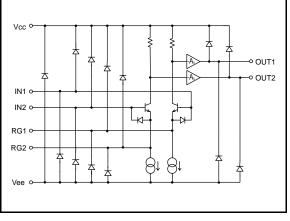

Figure 4. 1570 Equivalent Circuit with Internal Protection Diodes

#### Inputs

#### Simple Configurations

As shown in Figure 4, the 1570 includes protection diodes at all pins except  $V_{\rm CC}$  and  $V_{\rm EE}.$  These diodes reduce the likelihood that accidental electrostatic discharge (ESD) or electrical over stress (EOS) will damage the ICs. Other diodes across the base-emitter junctions of the input transistors prevent excessive reverse biasing of these junctions (which would degrade the noise performance of the input devices).

Figure 5. 1570 Typical Application Circuit With Single-Gang Pot for Gain Control, AC-Coupled  $R_G$

However, while the internal diodes are effective against ESD, they should not be relied upon to protect against excessive input voltage, which can result in significant current flow. This is a particular problem when the preamplifier includes a source of +48 V phantom power (see text below) but can be of concern in any situation where the input may be connected to high signal levels, in which the input signal voltage could exceed the supply rails. The phantom power protection networks shown in Figures 7 and 8 are worth considering even if phantom power is not included in the design.

#### DC Offsets and C<sub>G</sub>

Because  $R_G$  is dc coupled in the circuits of Figure 2 and 3, the differential dc level at the output of the 1570 will vary with gain. In most such applications, the output should be ac-coupled to the next stage, in order to eliminate this varying offset.

For applications where gain is variable, THAT recommends that  $R_G$  be ac-coupled as shown in Figures 5 and 6. (Figure 5 corresponds to Figure 2, while Figure 6 corresponds to Figure 3.) By adding  $C_G$  in series with  $R_G$ , dc gain is fixed at unity. This constrains the differential output dc offset to just over  $\pm 5$  mV, and prevents it from varying with gain.

$C_{\rm G}$  must be large enough not to interfere with low-frequency response at the smallest values of  $R_{\rm G}$ . With the values shown in Figures 5 and 6, the -3 dB

corner is about 5 Hz. Both circuits require a  $C_G$  of 3,300  $\mu$ F to maintain this low-frequency corner.

Note also that the voltage appearing across  $C_{\rm g}$  is very small. Since polarized electrolytic capacitors normally can withstand some small reverse bias,  $C_{\rm g}$  can usually be a polarized capacitor.

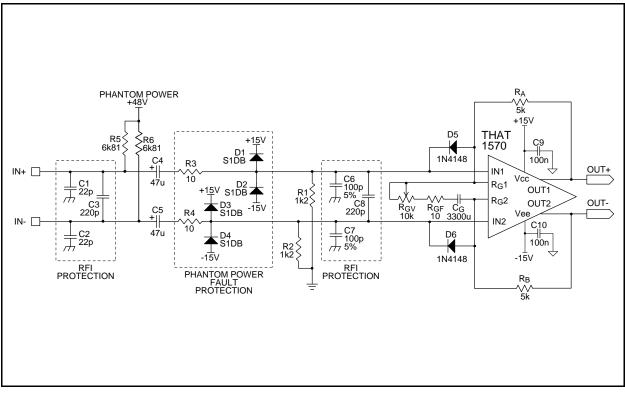

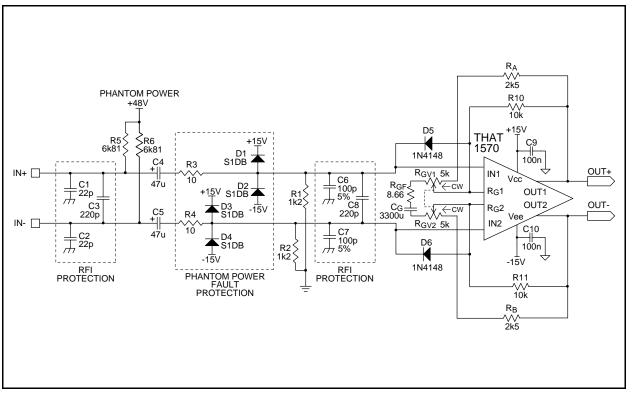

#### Phantom Power

Phantom power is required for many condenser microphones. THAT recommends the circuits of Figure 7 and 8 when phantom power is included.  $R_3$ ,  $R_4$ , and  $D_1 \sim D_6$  are used to limit the current that flows through the 1570 inputs when overloaded. These also protect the 1570 when the circuit inputs (IN+ and IN-) are shorted to ground while phantom power is turned on. This causes C4 and/or C5 to discharge through other circuit components (including the 1570 inputs), often generating transient currents of several amps.  $R_3$  and  $R_4$  should be at least 10  $\Omega$  to limit destructive currents. (Higher values further limit current flow, but introduce additional source impedance and noise.) Take care to ensure that the resistors used can handle the short-term inrush current; many small surface-mount types cannot. D<sub>1</sub> through D<sub>4</sub> prevent the IC's inputs from significantly exceeding the supply rails.

$D_1 \sim D_4$  prevent the input voltage from exceeding the supply rails. For best results, they should be glass-passivated types (sometimes called "GP") to ensure low leakage. (Leakage manifests itself as noise

Figure 6. 1570 Typical Application Circuit With Dual-Gang Pot for Gain Control, AC-Coupled  $R_G$

Figure 7. 1570 Typical Phantom Power Application Circuit With Single-Gang Pot for Gain Control, AC-Coupled R<sub>g</sub>

in addition to offset.)  $D_5$  and  $D_6$  steer currents around the input stage in the 1570 further preventing damage.

The series combination of  $C_4$  and  $C_5$  should be made large to minimize high-pass filtering of the signal based upon the sum of the values of  $R_1+R_2$ . As well, keeping their reactance low relative to the external microphone's source impedance will avoid increasing the effects of low-frequency current noise in the 1570 input stage.

As in Figures 2 and 3, Figures 7 and 8 differ in their approach to the gain potentiometer. The singlegang pot shown in Figure 7 may be a little less expensive to implement, but the dual-gang pot of Figure 8 will deliver better noise performance at low gains, for the reasons noted above. Note that Figure 8 features minimum gain of 3 dB, compared to Figure 7 at 6 dB. The low-frequency corners are about the same ( $\sim$ 5 Hz) in the two circuits.

Other manufacturers have recommended, and many pro audio products include, a zener diode arrangement instead of the bridge rectifier to  $V_{cc}$  and  $V_{EE}$  as shown in Figures 7 and 8. THAT does not recommend the zener approach, because we find that  $R_3$  and  $R_4$  must be made much larger (e.g., 51  $\Omega$ ) in order to limit peak currents enough to protect reasonably sized zener diodes (e.g. 1/2 W). Such large series input resistors will limit the noise performance of the preamp. The ultimate floor is set by the impedance of the microphone, but any additional series resistance further degrades performance.

Additionally, while at one time we recommended Schottky diodes for  $D_1 \sim D_4$  in Figures 7 and 8, we no longer do so. Schottky diodes appeal because of their fast turn-on behavior and low forward voltage drop. However, aside from their higher cost, our experience is that they tend to leak much more than conventional, glass-passivated power diodes, and that their fast turn-on behavior is unnecessary in practice.

For further insights into this subject, see the Audio Engineering Society preprint "The 48 Volt Phantom Menace," by Gary K. Hebert and Frank W. Thomas, presented at the 110th Audio Engineering Society (AES) Convention, and "The Phantom Menace Returns" by Rosalfonso Bortoni and Wayne Kirkwood, presented at the 127th AES Convention.

#### Outputs

Each of the two 1570 outputs has a dc offset of -610 mV. The differential output has low offset, but this common-mode dc offset must be considered in connecting the 1570 to subsequent circuitry. Most high-performance A/D converters require a dc offset at their inputs for proper operation. In such cases, drive circuitry should be configured to add the appropriate dc offset to the 1570 outputs in order to match the converter.

As well, the 1570 has common-mode gain of unity, regardless of its differential gain.

Figure 8. 1570 Typical Phantom Power Application Circuit With Dual-Gang Pot for Gain Control, AC-Coupled R<sub>g</sub>

Common-mode inputs are presented at the output, along with the common-mode dc offset of -610 mV. If these common-mode signals are not removed, they may limit dynamic range of subsequent stages.

If a single-ended output is desired, the THAT1246 is a self-contained differential amplifier which offers a convenient way to remove common mode offset, convert to single-ended, and match the headroom of the 1570 output to a single-ended drive. A dual version of this part, the 1280, and low cost versions (1250 single and 1290 dual) are also available. See Design Note 140, "Input and Output Circuits for THAT Preamplifier ICs" for further ideas.

The 1570 will drive loads as low as  $2 k\Omega$ , making it possible to drive A/D converters through resistive attenuators in low-cost applications. (However, in order to provide common mode rejection and to improve distortion performance, THAT recommends active designs to drive high-performance A/D converters. In addition to DN140, look for forthcoming application notes that offer more ideas on this subject.

### **PCB Layout Information**

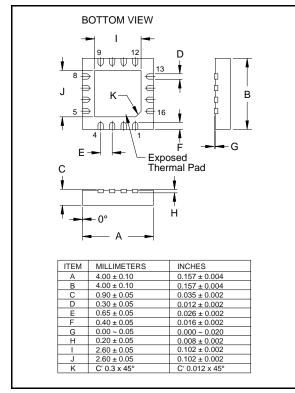

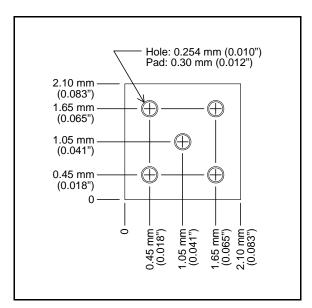

The 1570 QFN package includes a metal thermal pad on its bottom. This pad is connected internally to  $V_{EE}$ , and it should be soldered to a thermal pad on the PCB as shown in Figures 9 and 10. Five thermal vias should be arranged in the configuration shown in Figure 10 to provide uniform heat distribution between the top layer of the PCB to the bottom layer.

For current feedback amplifiers such as the THAT1570, stray capacitance to ground or power planes results in higher gains at high frequencies. This compromises common-mode rejection at high frequencies and, in extreme cases, can even lead to oscillation. Take care to avoid ground and power planes under and near  $R_A$ ,  $R_B$ ,  $R_G$ , their associated pins and traces.

The input signal lines are susceptible to magnetic pickup from power supply currents, which often take the form of half-wave rectified versions of the signal. Voltage fluctuations on the supply lines can couple capacitively as well. For this reason, take care not to run power and input signal lines close and/or parallel to each other.

#### Minimizing RFI

To minimize RF pickup, the  $C_1 \sim C_3$  network at the input of all the applications schematics should be located as close as possible to the input connector, and the ground ends of  $C_1$  and  $C_2$  tied as closely as possible to the chassis. When using the additional RFI protection network  $C_6 \sim C_8$  (shown in the phantom power circuits Fig. 7 and 8), these components should be located as close as possible to the 1570's input pins.

# Package and Soldering Information

| Symbol        | Conditions                           | Min                                                                                                          | Тур                                                                                                            | Max                                                                                                                                         | Units                                                                                                                                                  |

|---------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | See Fig. 9 for dimensions            |                                                                                                              | 16 Pin QFN                                                                                                     | I                                                                                                                                           |                                                                                                                                                        |

| $\theta_{JA}$ | QFN package soldered to board        |                                                                                                              | 110                                                                                                            |                                                                                                                                             | °C/W                                                                                                                                                   |

| ce            | Complies with January 27, 2003 Ro    | HS requir                                                                                                    | ements                                                                                                         |                                                                                                                                             |                                                                                                                                                        |

|               | JE                                   | EDEC JES                                                                                                     | SD22-A113                                                                                                      | -D (250 °C)                                                                                                                                 |                                                                                                                                                        |

| MSLAb         | ove-referenced JEDEC soldering profi | le                                                                                                           | 1                                                                                                              |                                                                                                                                             |                                                                                                                                                        |

|               | ce                                   | θ <sub>JA</sub> QFN package soldered to board       ce     Complies with January 27, 2003 Ro       JE     JE | θ <sub>JA</sub> QFN package soldered to board           ce         Complies with January 27, 2003 RoHS require | θ <sub>JA</sub> QFN package soldered to board     110       ce     Complies with January 27, 2003 RoHS requirements       JEDEC JESD22-A113 | θ <sub>JA</sub> QFN package soldered to board     110       ce     Complies with January 27, 2003 RoHS requirements       JEDEC JESD22-A113-D (250 °C) |

Figure 9. QFN-16 Surface Mount Package

| Package    | Order Number |

|------------|--------------|

| 16 pin QFN | 1570N16-U    |

Table 2. Ordering information

Figure 10. QFN-16 Thermal Solder Pad

Notes

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

# Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

# http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

# Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9