# FEATURES

- 1.6GHz 3dB Small Signal Bandwidth

- Low Distortion Driving 50Ω Load, 2.4V<sub>P-P</sub> Out –100dBc/–69dBc HD2/HD3 at 140MHz

- -80dBc IM3 and 46dBm OIP3 at 140MHz

- -100dBc/-66dBc HD2/HD3 at 380MHz

- -68dBc IM3 and 39dBm OIP3 at 380MHz

- 1.5nV/√Hz Output Noise

- 4.3pA/√Hz Input Current Noise

- Programmable High Speed, Fast Recovery Output Clamping

- 4.28V<sub>P-P</sub> Maximum Output Swing on a 50Ω Differential Load

- DC-Coupled Signal Path

- Operates on Single 4.75V to 5.25V Supply

- Power: 615mW on 5V, Can Be Reduced to 370mW, Shutdown Mode 120mW

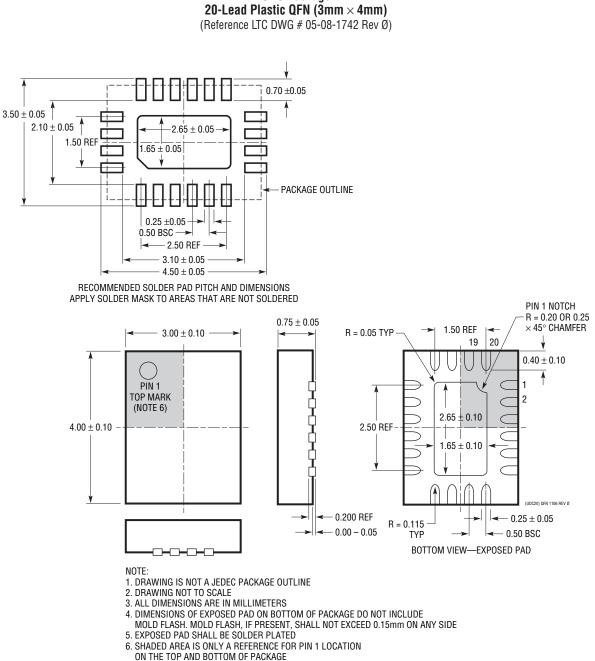

- 3mm × 4mm 20-Lead QFN Package

### **APPLICATIONS**

- Differential ADC Driver

- CCD Buffer

- Cable Driver

- 50Ω Buffer

𝗭, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### NOLOGY 1.6GHz Low Noise High Linearity Differential Buffer/16-Bit ADC Driver with Fast Clamp DESCRIPTION

The LTC<sup>®</sup>6417 is a differential unity gain buffer that can drive a  $50\Omega$  load with extremely low noise and excellent linearity. It is well suited for driving high speed 14- and 16-bit pipeline ADCs with input signals from DC to beyond 600MHz. Differential input impedance is  $18.5k\Omega$ , allowing 1:4 and 1:8 transformers to be used at the input providing additional system gain in  $50\Omega$  systems.

With no external biasing or gain setting components and a flow-through pinout, the LTC6417 is very easy to use. It can be DC-coupled and has a common mode output offset of -60mV. The LTC6417 input pins are internally biased to provide an output common mode voltage that is set by the voltage on the V<sub>CM</sub> pin for AC-coupled applications.

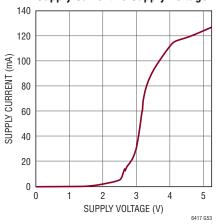

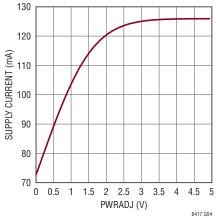

Supply current is typically 123mA and the LTC6417 operates on supply voltages ranging from 4.75V to 5.25V. Power consumption can be reduced to 74mA via the PWRADJ pin. The LTC6417 also has a hardware shutdown feature which reduces current consumption to 24mA.

The LTC6417 features fast, adjustable output voltage clamping to help protect subsequent circuitry. The CLHI pin sets the maximum swing, while a symmetric minimum swing is set up internally. LTC6417 V<sub> $\overline{OR}$ </sub> pin will signal overrange when the clamps limit output voltage.

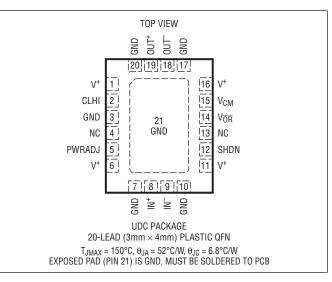

The LTC6417 is packaged in a 20-lead  $3mm \times 4mm$  QFN package. Pinout is optimized for placement directly adjacent to Linear Technology's high speed 14- and 16-bit ADCs.

### **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| Total Supply Voltage (V <sup>+</sup> to GND)<br>Input Current (CLHI, V <sub>CM</sub> )<br>Input Current (IN <sup>+</sup> , IN <sup>-</sup> ) | ±10mA         |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Output Current (OUT+, OUT <sup>-</sup> )                                                                                                     |               |

| Output Current (V <sub>OR</sub> )                                                                                                            |               |

| Operating Temperature Range                                                                                                                  |               |

| (T <sub>C</sub> ) (Note 2)                                                                                                                   | 40°C to 105°C |

| Specified Temperature Range                                                                                                                  |               |

| (T <sub>C</sub> ) (Note 3)                                                                                                                   | 40°C to 105°C |

| Storage Temperature Range<br>Junction Temperature (T <sub>JMAX</sub> )                                                                       |               |

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION                      | TEMPERATURE RANGE                |

|------------------|-------------------|---------------|------------------------------------------|----------------------------------|

| LTC6417CUDC#PBF  | LTC6417CUDC#TRPBF | LFVN          | 20-Lead (3mm $	imes$ 4mm) Plastic QFN    | 0°C to 70°C                      |

| LTC6417IUDC#PBF  | LTC6417IUDC#TRPBF | LFVN          | 20-Lead ( $3mm \times 4mm$ ) Plastic QFN | -40°C to 105°C (T <sub>C</sub> ) |

\*Temperature grades are identified by a label on the shipping container.

Consult LTC Marketing for parts specified with wider operating temperature ranges.

Consult LTC Marketing for information on lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

### DC ELECTRICAL CHARACTERISTICS

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C. V<sup>+</sup> = 5V, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sup>+</sup>, PWRADJ = V<sup>+</sup>, SHDN = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL                       | PARAMETER                                    | CONDITIONS                                                                              |   | MIN           | ТҮР    | MAX         | UNITS                                |  |  |

|------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|---|---------------|--------|-------------|--------------------------------------|--|--|

| Input/Output Characteristics |                                              |                                                                                         |   |               |        |             |                                      |  |  |

| G <sub>DIFF</sub>            | Differential Gain                            | $V_{INDIFF} = \pm 1.2V$ Differential                                                    | • | -0.15<br>-0.2 | -0.1   | 0<br>0      | dB<br>dB                             |  |  |

| TCG <sub>DIFF</sub>          | Differential Gain Temperature<br>Coefficient |                                                                                         | • |               | 0.0002 |             | dB/°C                                |  |  |

| V <sub>SWINGDIFF</sub>       | Differential Output Voltage Swing            | $V_{OUTDIFF}$ , $V_{INDIFF} = \pm 2.3V$                                                 | • | 4<br>3.3      | 4.28   |             | V <sub>P-P</sub><br>V <sub>P-P</sub> |  |  |

| V <sub>SWINGMIN</sub>        | Output Voltage Swing Low                     | Single-Ended Measurement of OUT <sup>+</sup> , OUT <sup>-</sup> $V_{INDIFF} = \pm 2.3V$ | • |               | 0.19   | 0.28<br>0.4 | V<br>V                               |  |  |

| V <sub>SWINGMAX</sub>        | Output Voltage Swing High                    | Single-Ended Measurement of OUT <sup>+</sup> , OUT <sup>-</sup> $V_{INDIFF} = \pm 2.3V$ | • | 2.25<br>2.05  | 2.33   |             | V<br>V                               |  |  |

6417f

**DC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 5V$ , GND = 0V, No  $R_{LOAD}$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ ,  $CLHI = V^+$ , PWRADJ = V<sup>+</sup>, SHDN = 0V unless otherwise noted.  $V_{INCM}$  is defined as  $(IN^+ + IN^-)/2$ .  $V_{OUTCM}$  is defined as  $(OUT^+ + OUT^-)/2$ .  $V_{INDIFF}$  is defined as  $(IN^+ - IN^-)$ .  $V_{OUTDIFF}$  is defined as  $(OUT^+ - OUT^-)$ . See DC test circuit schematic.

| SYMBOL                                                  | PARAMETER                                                                          | CONDITIONS                                                                                         |   | MIN          | ТҮР  | MAX          | UNITS      |

|---------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---|--------------|------|--------------|------------|

| I <sub>OUT</sub>                                        | Output Current Drive (Notes 1, 4)                                                  | Single-Ended Measurement of OUT+, OUT-                                                             |   | ±100         |      |              | mA         |

| V <sub>OS</sub>                                         | Differential Input Offset Voltage                                                  | $IN^+ = IN^- = 1.25V$ , $V_{OS} = V_{OUTDIFF}/G_{DIFF}$                                            | • | -3.2<br>-4   | -0.1 | 3.2<br>4     | mV<br>mV   |

| TCV <sub>OS</sub>                                       | Differential Input Offset Voltage Drift                                            |                                                                                                    |   |              | 1    |              | μV/°C      |

| VIOCM                                                   | Common Mode Offset Voltage, Input to Output                                        | V <sub>OUTCM</sub> - V <sub>INCM</sub>                                                             | • | -120<br>-140 | -60  | -10<br>0     | mV<br>mV   |

| IVR <sub>MIN</sub>                                      | Input Voltage Range, IN <sup>+</sup> , IN <sup>-</sup><br>(Minimum) (Single-Ended) | Defined by Output Voltage Swing Test                                                               | • |              |      | 0.1          | V          |

| IVR <sub>MAX</sub>                                      | Input Voltage Range IN <sup>+</sup> , IN <sup>-</sup><br>(Maximum) (Single-Ended)  | Defined by Output Voltage Swing Test                                                               | • | 2.4          |      |              | V          |

| I <sub>B</sub>                                          | Input Bias Current, IN+, IN-                                                       | IN <sup>+</sup> = IN <sup>-</sup> = 1.25V                                                          | • | -13<br>-18   | 2    | 13<br>18     | μA<br>μA   |

| R <sub>INDIFF</sub>                                     | Differential Input Resistance                                                      | V <sub>INDIFF</sub> = ±1.2V                                                                        | • | 12<br>11     | 18.5 | 25<br>27.5   | kΩ<br>kΩ   |

| CINDIFF                                                 | Differential Input Capacitance                                                     |                                                                                                    |   |              | 1    |              | pF         |

| R <sub>INCM</sub>                                       | Input Common Mode Resistance                                                       | IN+ = IN <sup>-</sup> = 0.65V to 1.85V                                                             | • | 5.8<br>5     | 9.25 | 13<br>15     | kΩ<br>kΩ   |

| CMRR                                                    | Common Mode Rejection Ratio                                                        | $IN^+ = IN^- = 0.65V \text{ to } 1.85V,$<br>CMRR = (V <sub>OUTDIFF</sub> /G <sub>DIFF</sub> /1.2V) | • | 63<br>60     | 91   |              | dB<br>dB   |

| R <sub>OUTDIFF</sub>                                    | Differential Output Resistance                                                     |                                                                                                    |   |              | 3    |              | Ω          |

| e <sub>N</sub>                                          | Input Noise Voltage Density                                                        | f = 100kHz                                                                                         |   |              | 1.5  |              | nV/√Hz     |

| i <sub>N</sub>                                          | Input Noise Current Density                                                        | f = 100kHz                                                                                         |   |              | 4.3  |              | pA/√Hz     |

| Output Common Mod                                       | e Voltage Control                                                                  |                                                                                                    |   |              |      |              |            |

| G <sub>CM</sub>                                         | V <sub>CM</sub> Pin Common Mode Gain                                               | V <sub>CM</sub> = 0.65V to 1.85V                                                                   | • | 0.82<br>0.8  | 0.92 |              | V/V<br>V/V |

| VINCMDEFAULT                                            | Default Input Common Mode Voltage                                                  | $V_{INCM}$ . IN <sup>+</sup> , IN <sup>-</sup> , $V_{CM}$ Pin Floating                             | • | 1.15<br>1.1  | 1.25 | 1.35<br>1.4  | V<br>V     |

| $V_{OS} (V_{CM} - V_{INCM})$                            | Offset Voltage, $V_{CM}$ to $V_{INCM}$                                             | $V_{CM} - V_{INCM}, V_{CM} = 1.25V$                                                                | • | -85<br>-90   | 15   | 115<br>135   | mV<br>mV   |

| VOUTCMDEFAULT                                           | Default Output Common Mode Voltage                                                 | Inputs Floating, V <sub>CM</sub> Pin Floating                                                      | • | 1.1<br>1     | 1.2  | 1.3<br>1.35  | V<br>V     |

| V <sub>OS</sub> (V <sub>CM</sub> – V <sub>OUTCM</sub> ) | Offset Voltage, $V_{CM}$ to $V_{OUTCM}$                                            | $V_{CM} - V_{OUTCM}, V_{CM} = 1.25V$                                                               | • | -50<br>-45   | 75   | 200<br>230   | mV<br>mV   |

| VOUTCMMIN                                               | Output Common Mode Voltage Range<br>(Minimum)                                      | V <sub>CM</sub> = 0.1V                                                                             | • |              | 0.29 | 0.63<br>0.65 | V<br>V     |

| VOUTCMMAX                                               | Output Common Mode Voltage Range<br>(Maximum)                                      | V <sub>CM</sub> = 2.4V                                                                             | • | 2<br>1.85    | 2.25 |              | V<br>V     |

| V <sub>CMDEFAULT</sub>                                  | V <sub>CM</sub> Pin Default Voltage                                                |                                                                                                    | • | 1.15<br>1.1  | 1.25 | 1.35<br>1.4  | V<br>V     |

| R <sub>VCM</sub>                                        | V <sub>CM</sub> Pin Input Resistance                                               | V <sub>CM</sub> = 0.65V to 1.85V                                                                   | • | 2<br>1.9     | 2.7  | 3.4<br>3.7   | kΩ<br>kΩ   |

| C <sub>VCM</sub>                                        | V <sub>CM</sub> Pin Input Capacitance                                              |                                                                                                    |   |              | 1    |              | pF         |

| BVCM                                                    | V <sub>CM</sub> Pin Bias Current                                                   | V <sub>CM</sub> = 1.25V                                                                            | • | -15<br>-27.5 | 1    | 15<br>27.5   | μA<br>μA   |

**DC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. V<sup>+</sup> = 5V, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sup>+</sup>, PWRADJ = V<sup>+</sup>, SHDN = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL                                       | PARAMETER                                    | CONDITIONS                                                                |   | MIN           | ТҮР  | MAX           | UNITS      |

|----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------|---|---------------|------|---------------|------------|

| DC Clamping Charact                          | eristics                                     |                                                                           |   |               |      |               | <u> </u>   |

| V <sub>CLHIDEFAULT</sub>                     | Default Output Clamp Voltage, High           |                                                                           | • | 2.4<br>2.35   | 2.48 | 2.55<br>2.6   | V<br>V     |

| V <sub>OS</sub> (CLHI – V <sub>OUTCM</sub> ) | Offset Voltage, CLHI to V <sub>OUTCM</sub>   |                                                                           | • | -60<br>-85    | 20   | 80<br>85      | mV<br>mV   |

| $V_{OS}$ (CLLO – $V_{OUT}$ )                 | Offset Voltage, CLLO to V <sub>OUT</sub>     | $V_{CLHI} = 2.0V, V_{CM} = 1.25V, IN^+ = 2.4V, IN^- = 0.1V$               | • | -100<br>-110  | 10   | 100<br>110    | mV<br>mV   |

| G <sub>LOHI</sub>                            | Low Side Clamp Gain with Respect to CLHI Pin | $V_{CLHI} = 2.0V, V_{CM} = 1.25V, IN^+ = 2.4V,$<br>IN <sup>-</sup> = 0.1V | • | -1.2<br>-1.25 | -1   | -0.8<br>-0.75 | V/V<br>V/V |

| G <sub>LOCM</sub>                            | Low Side Clamp Gain with Respect to CM Pin   | $V_{CLHI} = 2.0V, V_{CM} = 1.25V, IN^+ = 2.4V, IN^- = 0.1V$               | • | 1.65<br>1.5   | 1.9  | 2.2<br>2.25   | V/V<br>V/V |

| R <sub>CLHI</sub>                            | CLHI Pin Input Resistance                    | V <sub>CLHI</sub> = 1.5V to 2.5V                                          | • | 3.4<br>3.1    | 4.8  | 5.7<br>6      | kΩ<br>kΩ   |

| IB <sub>CLHI</sub>                           | CLHI Pin Bias Current                        | V <sub>CLHI</sub> = 2.5V                                                  | • | -12<br>-12.5  | 3    | 18<br>18.5    | μΑ<br>μΑ   |

| Power Supply                                 | I                                            | 1                                                                         |   |               |      |               | <u> </u>   |

| V <sub>S</sub>                               | Supply Voltage Range                         |                                                                           |   | 4.75          |      | 5.25          | V          |

| I <sub>S</sub>                               | Supply Current                               |                                                                           | • | 100<br>95     | 123  | 140<br>145    | mA<br>mA   |

| PSRR                                         | Power Supply Rejection Ratio                 | V <sub>S</sub> = 4.75V to 5.25V                                           | • | 65<br>63      | 72   |               | dB<br>dB   |

| SHDN Pin                                     |                                              | 1                                                                         |   |               |      |               |            |

| IS <sub>SHDN</sub>                           | Shutdown Current                             | V <sub>SHDN</sub> = 5V                                                    | • | 17<br>15      | 24   | 29<br>35      | mA<br>mA   |

| V <sub>SHDNDEFAULT</sub>                     | Default Shutdown Voltage                     |                                                                           | • |               |      | 0.1           | V          |

| V <sub>IL,SHDN</sub>                         | SHDN Input Low Voltage                       |                                                                           | • |               |      | 2             | V          |

| V <sub>IH,SHDN</sub>                         | SHDN Input High Voltage                      |                                                                           | • | 3.5           |      |               | V          |

| I <sub>IL,SHDN</sub>                         | SHDN Input Low Current                       | SHDN = 0V                                                                 | • | -1.6<br>-2    | 0    | 1.6<br>2      | μA<br>μA   |

| I <sub>IH,SHDN</sub>                         | SHDN Input High Current                      | SHDN = 5V                                                                 | • | 275<br>250    | 380  | 450<br>475    | μA<br>μA   |

| C <sub>SHDN</sub>                            | SHDN Pin Input Capacitance                   |                                                                           |   |               | 1    |               | pF         |

| R <sub>SHDN</sub>                            | SHDN Pin Input Resistance                    | SHDN = 2.5V to 5V                                                         | • | 6<br>5        | 10.5 | 14<br>15      | kΩ<br>kΩ   |

| PWRADJ Pin                                   |                                              | 1                                                                         |   |               |      |               |            |

| V <sub>PWRADJDEFAULT</sub>                   | Default PWRADJ Voltage                       | PWRADJ Floating                                                           |   | 1.5<br>1.45   | 1.65 | 1.8<br>1.85   | V<br>V     |

| ISL                                          | Supply Low Current                           | PWRADJ = 0V                                                               | • | 45<br>40      | 74   | 105<br>110    | mA<br>mA   |

| IIL, PWRADJ                                  | PWRADJ Input Low Current                     | PWRADJ = 0V                                                               | • | -145<br>-165  | -120 | -80<br>-75    | μA<br>μA   |

| I <sub>IH, PWRADJ</sub>                      | PWRADJ Input High Current                    | PWRADJ = 5V                                                               | • | 210<br>200    | 240  | 290<br>300    | μΑ<br>μΑ   |

| C <sub>PWRADJ</sub>                          | PWRADJ Pin Input Capacitance                 |                                                                           |   |               | 1    |               | pF         |

6417f

### DC ELECTRICAL CHARACTERISTICS

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C. V<sup>+</sup> = 5V, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sup>+</sup>, PWRADJ = V<sup>+</sup>, SHDN = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL               | PARAMETER                                           | CONDITIONS                                                                          |   | MIN           | ТҮР  | MAX         | UNITS    |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------|---|---------------|------|-------------|----------|

| R <sub>PWRADJ</sub>  | PWRADJ Pin Input Resistance                         | PWRADJ = 2.5V to 5.0V                                                               | • | 10.5<br>10    | 14.5 | 19<br>20    | kΩ<br>kΩ |

| V <sub>OR</sub> Pin  |                                                     |                                                                                     | · |               |      |             | <u> </u> |

| VOR(HI)              | Maximum Voltage on V <sub>OR</sub> Pin              | V <sub>CL</sub> = 5.0V, V <sub>CM</sub> = 1.25V                                     | • | 3.25<br>3.2   | 3.35 | 3.55<br>3.6 | V<br>V   |

| I OR(DEFAULT)        | Default Pull-Down Current on V <sub>OR</sub> Pin    | $V_{CL} = 50$ V, $V_{CM} = 1.25$ V                                                  | • | -900<br>-1150 | -770 | 650<br>500  | μA<br>μA |

| I <sub>OR(MAX)</sub> | Maximum Pull-Down Current Both<br>Clamps are Active | $V_{CL} = 2.0$ V, $V_{CM} = 1.25$ V, IN <sup>+</sup> = 2.4V, IN <sup>-</sup> = 0.1V | • |               | 1    | 1.5<br>2    | μA<br>μA |

**AC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 5V unless otherwise noted, GND = 0V,  $R_{LOAD} = 500\Omega$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, PWRADJ = V<sub>CC</sub>, SHDN = 0V unless otherwise noted.  $V_{INCM}$  is defined as  $(IN^+ + IN^-)/2$ .  $V_{OUTCM}$  is defined as  $(OUT^+ + OUT^-)/2$ .  $V_{INDIFF}$  is defined as  $(IN^+ - IN^-)$ .  $V_{OUTDIFF}$  is defined as  $(OUT^+ - OUT^-)$ . See DC test circuit schematic.

| SYMBOL                  | PARAMETER                                   | CONDITIONS                                                                                                                                   | MIN TYP M | AX UNITS |

|-------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|

| Differential A          | AC Characteristics                          |                                                                                                                                              |           |          |

| -3dBBW                  | –3dB Bandwidth                              | 200mV <sub>P-P,OUT</sub> Differential                                                                                                        | 1.6       | GHz      |

| 0.1dBBW                 | ±0.1dB Bandwidth                            | 200mV <sub>P-P,OUT</sub> Differential                                                                                                        | 0.18      | GHz      |

| 0.5dBBW                 | ±0.5dB Bandwidth                            | 200mV <sub>P-P,OUT</sub> Differential                                                                                                        | 0.45      | GHz      |

| 1/f                     | 1/f Noise Corner                            |                                                                                                                                              | 25        | kHz      |

| SR                      | Slew Rate                                   | Differential                                                                                                                                 | 10        | V/ns     |

| t <sub>S1%</sub>        | 1% Settling Time                            | 2V <sub>P-P,OUT</sub>                                                                                                                        | 0.8       | ns       |

| t <sub>OFF</sub>        | Shutdown Time                               | SHDN = 0V to 5V                                                                                                                              | 40        | ns       |

| t <sub>ON</sub>         | Enable Time                                 | SHDN = 5V to 0V                                                                                                                              | 15        | ns       |

| t <sub>PWRADJ,OFF</sub> | PWRADJ Off Time                             | PWRADJ = 5V to 0V                                                                                                                            | 10        | ns       |

| t <sub>pwradj,on</sub>  | PWRADJ On Time                              | PWRADJ = 0V to 5V                                                                                                                            | 5         | ns       |

| t <sub>CL,OFF</sub> 10% | Clamp Release Time                          | CLHI = 1.5V, $V_{CM}$ = 1.25V, IN <sup>+</sup> = 1.625V to 1.25V, IN <sup>-</sup> = 1.25V to 0.875V                                          | 1         | ns       |

| t <sub>CL,ON</sub> 10%  | Clamp Engage Time                           | CLHI = 1.5V, $V_{CM}$ = 1.25V, IN <sup>+</sup> = 1.25V to 1.625V, IN <sup>-</sup> = 1.25V to 0.875V                                          | 5         | ns       |

| Common Mo               | de AC Characteristics (V <sub>CM</sub> Pin) | · · · · ·                                                                                                                                    | · ·       |          |

| -3dBBW                  | V <sub>CM</sub> Pin Small Signal –3dB BW    | $V_{CM} = 0.1V_{P-P}$ , Measured Single-Ended at Output                                                                                      | 10        | MHz      |

| SR <sub>CM</sub>        | Common Mode Slew Rate                       | Measured Single-Ended at Output                                                                                                              | 2         | V/µs     |

| Overrange A             | C Characteristics (V <sub>OR</sub> Pin)     |                                                                                                                                              |           |          |

| –3dBBW                  | V <sub>OR</sub> Pin Small Signal –3dB BW    | $V_{OR} = 0.1V_{P-P}$ , CLHI = 2V, IN <sup>+</sup> = 2.4V, IN <sup>-</sup> = 0.1V,<br>R <sub>VOR</sub> = 1k, Measured Single-Ended at Output | 200       | MHz      |

| SR <sub>VOR</sub>       | Overrange Slew Rate                         | Measured Single-Ended at Output                                                                                                              | 40        | V/µs     |

| AC Clamping             | Characteristics                             | · · · · · ·                                                                                                                                  |           |          |

| t <sub>OVDR</sub>       | Overdrive Recovery Time                     | 1.9V <sub>P-P,OUT</sub>                                                                                                                      | 2         | ns       |

**AC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 5V unless otherwise noted, GND = 0V,  $R_{LOAD} = 500\Omega$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, PWRADJ =  $V_{CC}$ , SHDN = 0V unless otherwise noted.  $V_{INCM}$  is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2.  $V_{OUTCM}$  is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2.  $V_{INDIFF}$  is defined as (IN<sup>+</sup> - IN<sup>-</sup>).  $V_{OUTDIFF}$  is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL       | PARAMETER                              | CONDITIONS                                                                                                                              | MIN TYP MAX  | UNITS      |

|--------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|

| AC Linearity | y .                                    |                                                                                                                                         | I            |            |

| 10MHz Sigr   | nal                                    |                                                                                                                                         |              |            |

| HD3          | Third Harmonic Distortion              | $\label{eq:VoutDiff} \begin{array}{l} V_{OUTDIFF} = 2.4 V_{P-P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} = 2.4 V_{P-P} \end{array}$            | 89<br>93     | dBc<br>dBc |

| IM3          | Third Order Intermodulation Distortion | $      V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega                                 $                                                     | -100<br>-110 | dBo<br>dBo |

| OIP3         | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$                                                                                              | 56           | dBm        |

| P1dB         | Output 1dB Compression Point           |                                                                                                                                         | 16.1         | dBm        |

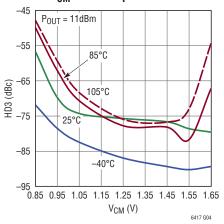

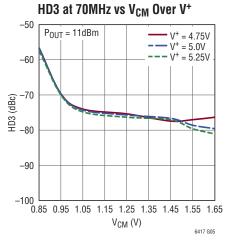

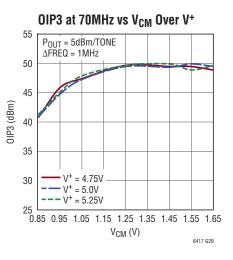

| 70MHz Sigr   | nal                                    |                                                                                                                                         |              |            |

| HD3          | Third Harmonic Distortion              |                                                                                                                                         | -74<br>-77   | dBc<br>dBc |

| IM3          | Third Order Intermodulation Distortion | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$<br>$V_{OUTDIFF} = 2.4V_{P-P}$                                                                | 86<br>96     | dBc<br>dBc |

| OIP3         | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                            | 48           | dBm        |

| P1dB         | Output 1dB Compression Point           |                                                                                                                                         | 15.8         | dBm        |

| 140MHz Sig   | gnal                                   | ,                                                                                                                                       |              |            |

| HD3          | Third Harmonic Distortion              | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$ $V_{OUTDIFF} = 2.4V_{P-P}$                                                                   | -69<br>-73   | dBc<br>dBc |

| IM3          | Third Order Intermodulation Distortion | $\label{eq:VoutDiff} \begin{split} V_{OUTDIFF} = 2.4 V_{P-P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} = 2.4 V_{P-P} \end{split}$               | -80<br>-91   | dBc<br>dBc |

| OIP3         | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$                                                                                              | 46           | dBm        |

| P1dB         | Output 1dB Compression Point           |                                                                                                                                         | 15.8         | dBm        |

| 200MHz Sig   | ynal                                   |                                                                                                                                         |              |            |

| HD3          | Third Harmonic Distortion              | $\label{eq:VoutDiff} \begin{split} V_{OUTDIFF} = 2.4 V_{P\text{-}P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} = 2.4 V_{P\text{-}P} \end{split}$ | -68<br>-71   | dBc<br>dBc |

| IM3          | Third Order Intermodulation Distortion | $\label{eq:VoutDiff} \begin{split} V_{OUTDIFF} &= 2.4 V_{P-P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} &= 2.4 V_{P-P} \end{split}$             | -78<br>-87   | dBc<br>dBc |

| OIP3         | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                            | 44           | dBm        |

| P1dB         | Output 1dB Compression Point           |                                                                                                                                         | 15.8         | dBm        |

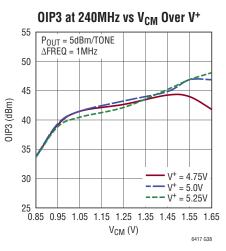

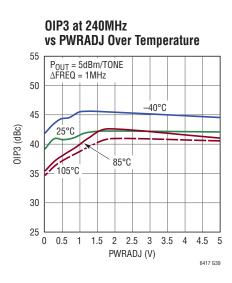

| 240MHz Sig   | ynal                                   |                                                                                                                                         | <u> </u>     |            |

| HD3          | Third Harmonic Distortion              |                                                                                                                                         | -67<br>-70   | dBc<br>dBc |

| IM3          | Third Order Intermodulation Distortion | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$ $V_{OUTDIFF} = 2.4V_{P-P}$                                                                   | -76<br>-85   | dBc<br>dBc |

| OIP3         | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                            | 43           | dBm        |

| P1dB         | Output 1dB Compression Point           |                                                                                                                                         | 15.7         | dBm        |

| 300MHz Sig   | jnal                                   |                                                                                                                                         |              | L          |

| HD3          | Third Harmonic Distortion              | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$ $V_{OUTDIFF} = 2.4V_{P-P}$                                                                   | 66<br>69     | dBc<br>dBc |

**AC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 5V unless otherwise noted, GND = 0V,  $R_{LOAD} = 500\Omega$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, PWRADJ =  $V_{CC}$ , SHDN = 0V unless otherwise noted.  $V_{INCM}$  is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2.  $V_{OUTCM}$  is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2.  $V_{INDIFF}$  is defined as (IN<sup>+</sup> - IN<sup>-</sup>).  $V_{OUTDIFF}$  is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL     | PARAMETER                              | CONDITIONS                                                                                                                   | MIN TYP MAX | UNITS      |

|------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|------------|

| IM3        | Third Order Intermodulation Distortion | $\label{eq:VoutDiff} \begin{array}{l} V_{OUTDIFF} = 2.4 V_{P-P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} = 2.4 V_{P-P} \end{array}$ | -73<br>-79  | dBo<br>dBo |

| OIP3       | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | 41          | dBn        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 15.6        | dBm        |

| 380MHz Sig | nal                                    | · ·                                                                                                                          |             |            |

| HD3        | Third Harmonic Distortion              |                                                                                                                              | 66<br>68    | dBo<br>dBo |

| IM3        | Third Order Intermodulation Distortion |                                                                                                                              | -68<br>-77  | dBo<br>dBo |

| OIP3       | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | 36 39       | dBm        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 15.3        | dBm        |

| 400MHz Sig | nal                                    |                                                                                                                              |             |            |

| HD3        | Third Harmonic Distortion              | $\label{eq:VoutDiff} \begin{array}{l} V_{OUTDIFF} = 2.4 V_{P-P}, \ R_L = 50 \Omega \\ V_{OUTDIFF} = 2.4 V_{P-P} \end{array}$ | -65<br>-68  | dBo<br>dBo |

| IM3        | Third Order Intermodulation Distortion | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | -68         | dBo        |

| OIP3       | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | 39          | dBm        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 15.3        | dBm        |

| 500MHz Sig | nal                                    |                                                                                                                              |             |            |

| HD3        | Third Harmonic Distortion              |                                                                                                                              | 65<br>67    | dBo<br>dBo |

| IM3        | Third Order Intermodulation Distortion | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | -64         | dBo        |

| OIP3       | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | 37          | dBm        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 15.0        | dBm        |

| 600MHz Sig | nal                                    |                                                                                                                              |             |            |

| HD3        | Third Harmonic Distortion              | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | -60         | dBo        |

| IM3        | Third Order Intermodulation Distortion | $V_{OUTDIFF} = 2.4V_{P-P}, R_L = 50\Omega$                                                                                   | -58         | dBo        |

| 0IP3       | Output Third Order Intercept           | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | 34          | dBm        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 14.7        | dBm        |

| 700MHz Sig | nal                                    |                                                                                                                              |             |            |

| HD3        | Third Harmonic Distortion              | $V_{OUTDIFF} = 2.4 V_{P-P}, R_L = 50 \Omega$                                                                                 | -55         | dBo        |

| IM3        | Third Order Intermodulation Distortion | $V_{\text{OUTDIFF}} = 2.4 V_{\text{P-P}}, R_{\text{L}} = 50 \Omega$                                                          | -52         |            |

| OIP3       | Output Third Order Intercept           | $V_{\text{OUTDIFF}} = 2.4 V_{\text{P-P}}, R_{\text{L}} = 50 \Omega$                                                          | 31          | dBm        |

| P1dB       | Output 1dB Compression Point           |                                                                                                                              | 14.2        | dBm        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC6417C/LTC6417I is guaranteed functional over the case temperature operating range of  $-40^{\circ}$ C to  $105^{\circ}$ C.  $\theta_{JC} = 6.8^{\circ}$ C/W.

Note 3: The LTC6417C is guaranteed to meet specified performance from 0°C to 70°C. It is designed, characterized and expected to meet specified performance from -40°C and 105°C case temperature range but is not tested or QA sampled at these temperatures. The LT6417I is guaranteed to meet specified performance from -40°C to 105°C case temperature range. Note 4: This parameter is pulse tested.

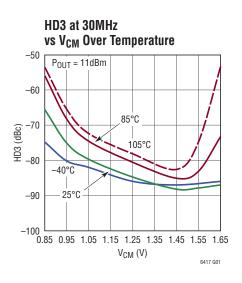

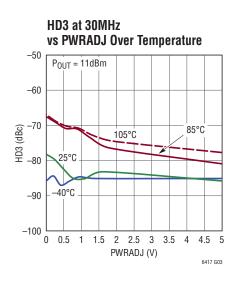

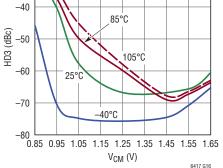

HD3 at 70MHz vs V<sub>CM</sub> Over Temperature

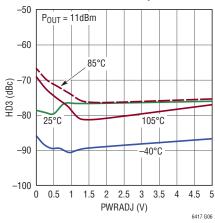

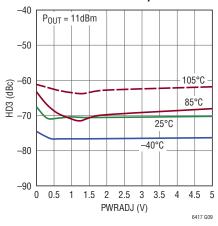

HD3 at 70MHz vs PWRADJ Over Temperature

HD3 at 140MHz vs V<sub>CM</sub> Over Temperature

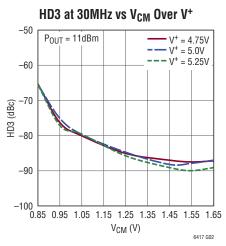

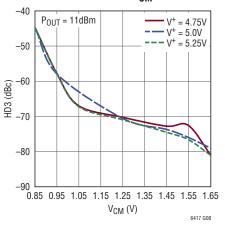

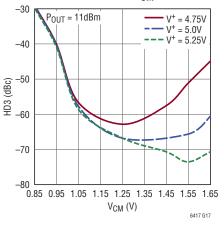

HD3 at 140MHz vs V<sub>CM</sub> Over V<sup>+</sup>

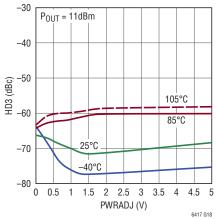

HD3 at 140MHz vs PWRADJ Over Temperature

8

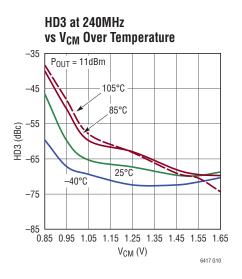

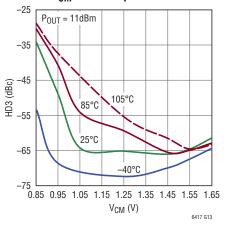

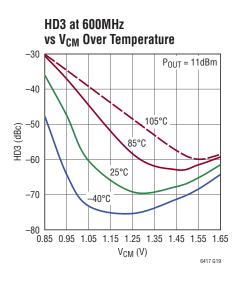

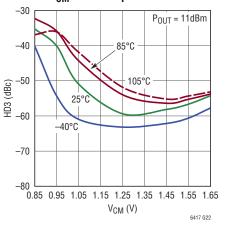

HD3 at 380MHz vs V<sub>CM</sub> Over Temperature

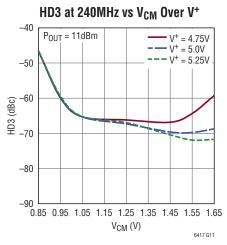

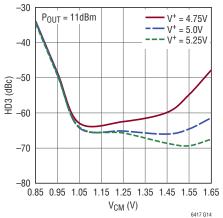

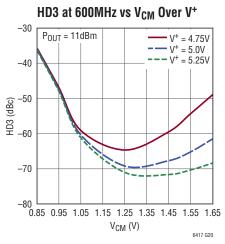

HD3 at 380MHz vs V<sub>CM</sub> Over V<sup>+</sup>

(2) −50 (2) −50 (2) −60 (2) −50 (105°C) (105°C) (2) −50 (105°C)

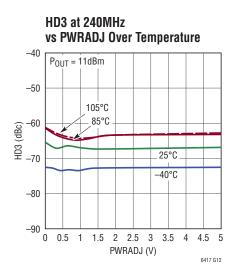

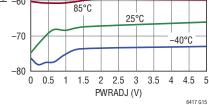

vs PWRADJ Over Temperature

HD3 at 380MHz

$P_{OUT} = 11$ dBm

-30

-40

HD3 at 500MHz vs V<sub>CM</sub> Over Temperature

HD3 at 500MHz vs V<sub>CM</sub> Over V<sup>+</sup>

HD3 at 500MHz vs PWRADJ Over Temperature

HD3 at 700MHz vs V<sub>CM</sub> Over Temperature

HD3 at 700MHz vs PWRADJ Over Temperature

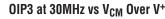

**OIP3 at 30MHz** vs V<sub>CM</sub> Over Temperature 55 25°C 85°C 50 45 OIP3 (dBm) -40°C 40 105°C 35 30  $P_{OUT} = 5dBm/TONE$  $\Delta FREQ = 1MHz$ 25 0.85 0.95 1.05 1.15 1.25 1.35 1.45 1.55 1.65 V<sub>CM</sub> (V) 6417 G25

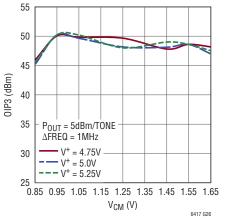

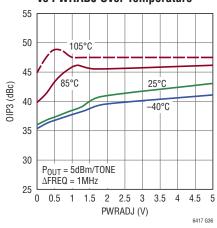

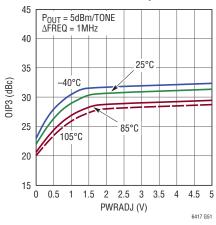

OIP3 at 30MHz vs PWRADJ Over Temperature

6417f

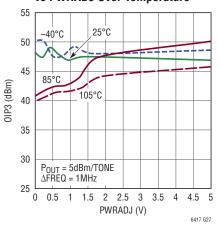

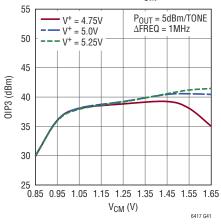

OIP3 at 100MHz vs V<sub>CM</sub> Over Temperature

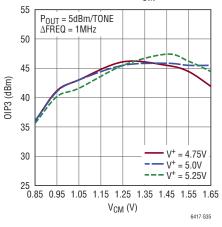

OIP3 at 100MHz vs V<sub>CM</sub> Over V<sup>+</sup> 55 P<sub>OUT</sub> = 5dBm/TONE  $\Delta FREQ = 1MHz$ 50 45 OIP3 (dBm) 40 35  $V^{+} = 4.75V$ 30 - V<sup>+</sup> = 5.0V --- V<sup>+</sup> = 5.25V 25 0.85 0.95 1.05 1.15 1.25 1.35 1.45 1.55 1.65 V<sub>CM</sub> (V) 6417 G32

OIP3 at 100MHz vs PWRADJ Over Temperature

OIP3 at 140MHz vs PWRADJ Over Temperature

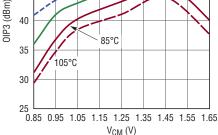

OIP3 at 140MHz vs V<sub>CM</sub> Over Temperature  $\Delta FREQ = 1MHz$  $25^{\circ}C$   $-40^{\circ}C$ 40

6417 G34

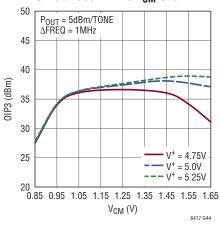

OIP3 at 140MHz vs V<sub>CM</sub> Over V<sup>+</sup>

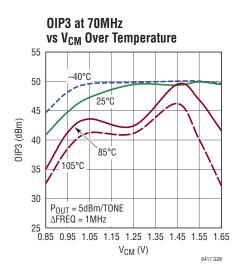

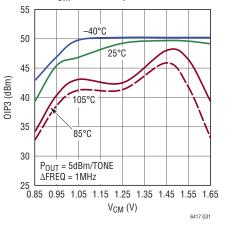

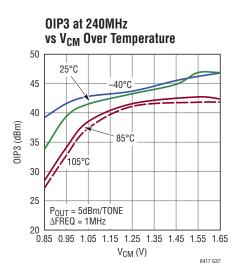

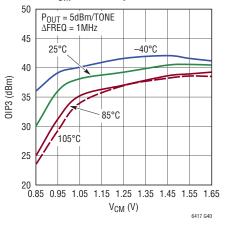

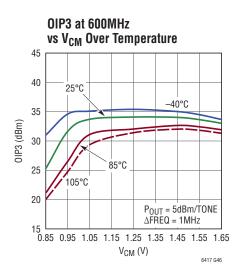

OIP3 at 380MHz vs V<sub>CM</sub> Over Temperature

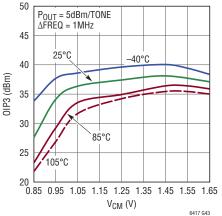

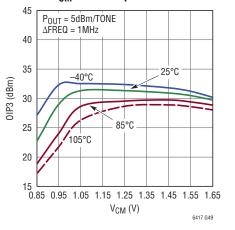

OIP3 at 500MHz vs V<sub>CM</sub> Over Temperature

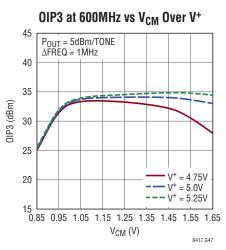

OIP3 at 380MHz vs V<sub>CM</sub> Over V<sup>+</sup>

OIP3 at 500MHz vs V<sub>CM</sub> Over V<sup>+</sup>

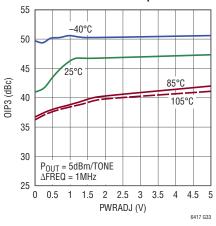

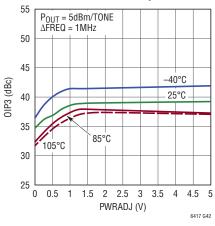

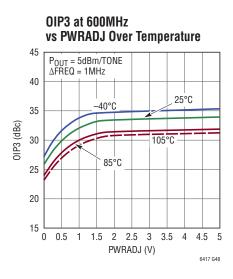

OIP3 at 380MHz vs PWRADJ Over Temperature

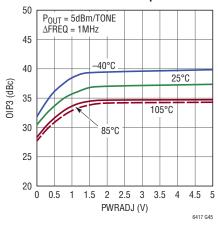

OIP3 at 500MHz vs PWRADJ Over Temperature

6417f

OIP3 at 700MHz vs V<sub>CM</sub> Over Temperature

OIP3 at 700MHz vs V<sub>CM</sub> Over V<sup>+</sup> 45  $P_{OUT} = 5 dBm/TONE$  $V^{+} = 4.75V$  $\Delta FREQ = 1MHz$  $V^+ = 5.0V$ 40 V<sup>+</sup> = 5.25V 35 OIP3 (dBm) 30 25 20 15 0.85 0.95 1.05 1.15 1.25 1.35 1.45 1.55 1.65 V<sub>CM</sub> (V) 6417 G50

OIP3 at 700MHz vs PWRADJ Over Temperature

vs Frequency and Supply Voltage 20  $V^{+} = 5.25V$  $V^{+} = 5.0V$  $V^{+} = 4.75V$ 18 dB COMPRESSION (dBm) 16 14 Ы 12 10 100 200 300 400 500 600 700 FREQUENCY (MHz) 6417 G52

**Output 1dB Compression**

Supply Current vs Supply Voltage

Supply Current vs PWRADJ

### PIN FUNCTIONS

**V**<sup>+</sup> (**Pins 1, 6, 11, 16**): Positive Power Supply. Typically 5V. Split supplies are possible as long as the voltage between V<sup>+</sup> and GND is 4.75V to 5.25V. Bypass capacitors of 680pF and 0.1 $\mu$ F as close to the part as possible should be used between the supplies.

**CLHI (Pin 2):** High Side Clamp Voltage. The voltage applied to the CLHI pin defines the upper voltage limit of the OUT<sup>+</sup> and OUT<sup>-</sup> pins. This voltage should be set at least 300mV above the upper voltage range of the ADC. On a 5V supply, the CLHI pin will float to a 2.5V default voltage. CLHI has a Thevenin equivalent of approximately 4.8k $\Omega$  and can be overdriven by an external voltage. The CLHI pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.01µF.

**GND (Pins 3, 7, 10, 17, 20, Exposed Pad Pin 21):** Negative Power Supply. Normally tied to ground. All pins and the exposed pad must be tied to the same voltage. GND may be tied to a voltage other than ground as long as the voltage between V<sup>+</sup> and GND is 4.75V to 5.25V. If the GND pins are not tied to ground, bypass each with 680pF and  $0.1\mu$ F capacitors as close to the package as possible. The exposed pad must be soldered to the printed circuit board ground plane for good heat transfer.

**NC (Pins 4, 13):** No Connection. These pins are not connected internally.

**PWRADJ (Pin 5):** Power Adjust Voltage. The voltage applied to this pin scales the bias current internal to the LTC6417. The PWRADJ pin will float to a 1.6V default voltage. PWRADJ has a Thevenin equivalent resistance of approximately 14.5k and can be overdriven by an external voltage. The PWRADJ pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.01µF.

**IN+, IN<sup>-</sup> (Pin 8, Pin 9):** Non-inverting and inverting input pins of the buffer, respectively. These pins are high impedance, approximately 9.5k. If AC-coupled, these pins will self bias to the voltage applied to the V<sub>CM</sub> pin.

**SHDN (Pin 12):** This pin puts the LTC6417 in sleep mode when pulled high. If no voltage is applied to the SHDN pin, it floats down to the same potential as GND.

$V_{\overline{OR}}$  (Pin 14): Overrange Output. This pin, by default at 3.4V, will be pulled down to GND, when one or both input signals go beyond the minimum or maximum swing set by the CLHI and V<sub>CM</sub> pins.

$V_{CM}$  (Pin 15): This pin sets the output common mode voltage seen at OUT<sup>+</sup> and OUT<sup>-</sup> by driving IN<sup>+</sup> and IN<sup>-</sup> through a buffer with a high output resistance of 9.5k. The V<sub>CM</sub> pin has a Thevenin equivalent resistance of approximately 2.7k and can be overdriven by an external voltage. If no voltage is applied to V<sub>CM</sub>, it will float to a default voltage of approximately 1.25V on a 5V supply. The V<sub>CM</sub> pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.01µF.

OUT<sup>-</sup>, OUT<sup>+</sup> (Pin 18, Pin 19): Outputs.

### DC TEST CIRCUIT SCHEMATIC

### **BLOCK DIAGRAM**

LTC6417 Simplified Schematic

### **Circuit Operation**

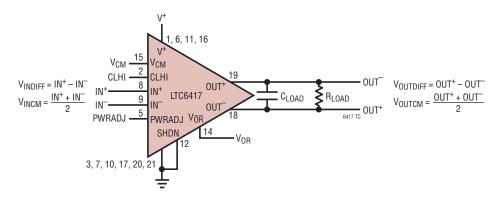

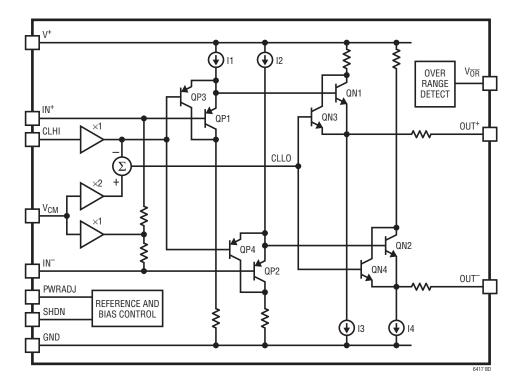

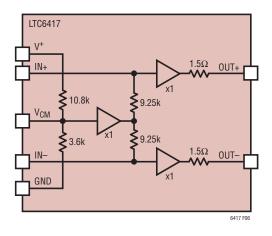

The LTC6417 is a low noise and low distortion fully differential unity gain ADC driver with a –3dB bandwidth spanning DC to 1.6GHz, a differential input impedance of 18.5k $\Omega$ , and a differential output impedance of 3 $\Omega$ . The LTC6417 is composed of a fully differential buffer with output common mode voltage control circuitry and high speed voltage-limiting clamps at the output. Lowpass or bandpass filters are easily implemented with just a few external components. The LTC6417 is very flexible in terms of I/O coupling. It can be AC- or DC-coupled at the inputs, the outputs or both. When using the LTC6417 with DC-coupled inputs, best performance is obtained with an input common mode voltage between 1V and 1.5V. For AC-coupled operation, the LTC6417 will take the voltage applied to the V<sub>CM</sub> pin and use it to bias the inputs so that the output common mode voltage equals  $V_{CM}$ , thus no external circuitry is needed. The V<sub>CM</sub> pin has been designed to directly interface with the  $V_{CM}$  pin found on Linear Technology's high speed ADC families.

#### Input Impedance and Matching

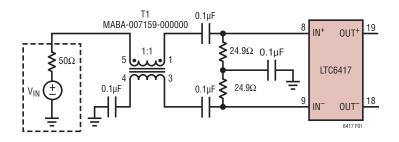

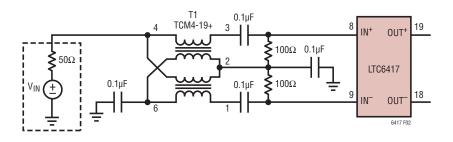

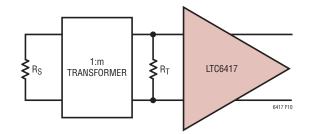

The LTC6417 has a high differential input impedance of 18.5k $\Omega$ . The differential inputs may need to be terminated to a lower value impedance, e.g.  $50\Omega$ , in order to provide an impedance match for the source. Figure 1 shows input matching and single-ended to differential conversion using a 1:1 balun, while Figure 2 shows a similar circuit using a 1:4 balun to achieve an additional 6dB of voltage gain. These circuits provide a wideband impedance match. The balun and matching resistors must be placed close to the input pins in order to minimize the rejection due to input mismatch. In Figures 1 and 2, the capacitor centertapping the two input termination resistors improves high frequency common mode rejection. As an alternative to this wideband approach, a narrowband impedance match can be used at the inputs of the LTC6417 for frequency selection and/or noise reduction.

Figure 1. Input Termination for Differential 50 $\Omega$  Input Impedance Using a 1:1 Balun

Figure 2. Input Termination for Differential 50 $\Omega$  Input Impedance Using a 1:4 Balun

The noise figure of the LTC6417 application circuit also depends upon the input termination. For example, the input 1:4 balun in Figure 2 improves noise figure by add-ing 6dB of voltage gain at the inputs. A trade-off between gain and noise is obvious when constant noise figure circle and constant gain circle are plotted within the same input Smith Chart. This technique can be used to determine the optimal source impedance for a given gain and noise requirement.

#### **Output Match and Filter**

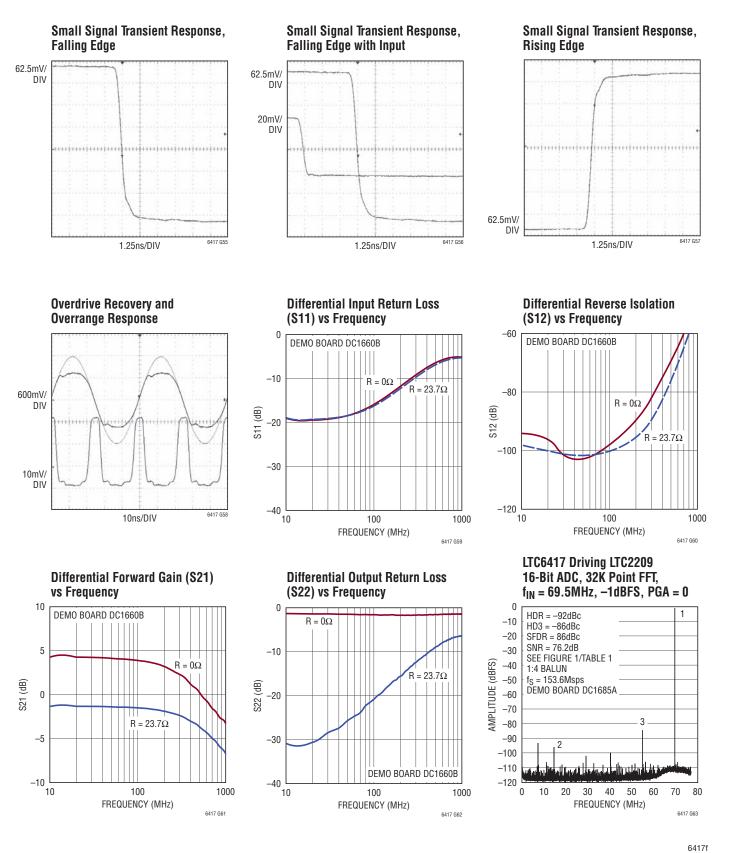

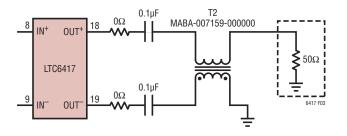

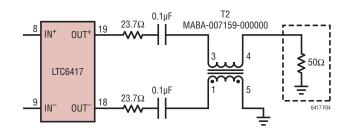

The LTC6417 provides an output resistance of  $1.5\Omega$  at each output. In most cases, the LTC6417 can be used to drive an ADC without back termination but for testing purposes, Figure 3 shows the LTC6417 driving a differential  $50\Omega$  load impedance using a 1:1 balun. If output

matching for the 1:1 balun is desired, resistors of  $23.7\Omega$  should be inserted in series with each LTC6417 output. This is shown in Figure 4 where the LTC6417 is driving a differential 100 $\Omega$  load impedance.

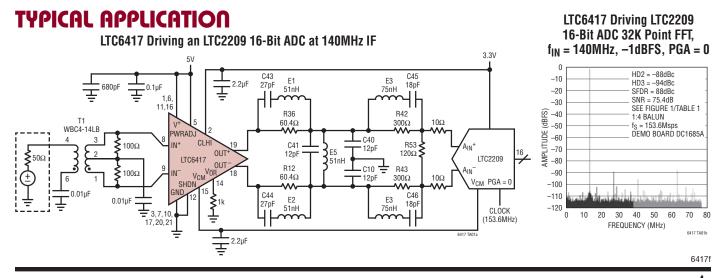

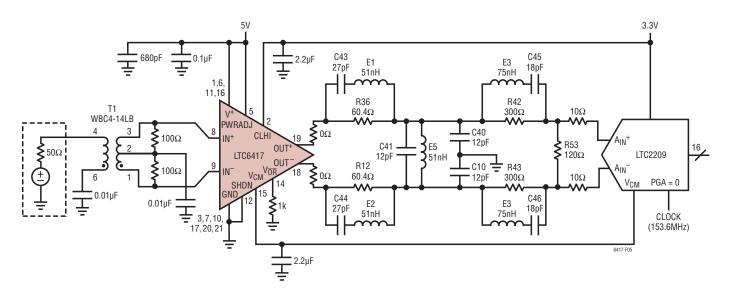

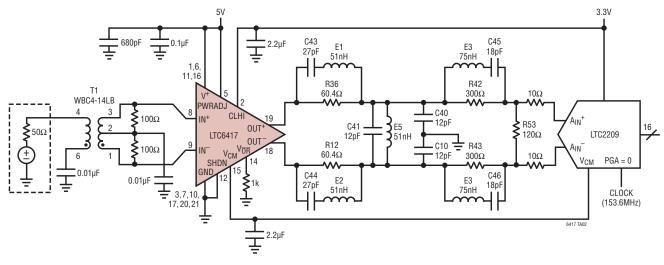

As mentioned above, the LTC6417 can drive an ADC without external output impedance matching, but improved performance can usually be obtained with the addition of a few components. Figure 5 shows a 6th order bandpass filter with a 148MHz center frequency, –3dB points of 85MHz and 210MHz used for driving the LTC2209 16-bit ADC. In the passband the filter has less than 1 dB ripple. This higher order filter has a sharp roll-off outside its passband, therefore it rejects noise and suppresses distortion components in its stopband. To double the filter center frequency, halve the capacitor and inductor values, and maintain resistor values; this also doubles the filter bandwidth.

Figure 3. LTC6417 with No Back Termination Driving a 50  $\Omega$  Load Using a 1:1 Balun

Figure 4. Output Termination for Differential 50  $\Omega$  Load Using a 1:1 Balun

Figure 5. DC1685A Simplified Schematic with Suggested Bandpass Filter for Driving an LTC2209 16-Bit ADC at 140MHz

|            |       | INPUT FREQUENCIES |        |        |  |  |  |

|------------|-------|-------------------|--------|--------|--|--|--|

| COMPONENTS | 70MHz | 140MHz            | 270MHz | 380MHz |  |  |  |

| R12 = R36  | 60.4Ω | 60.4Ω             | 60.4Ω  | 60.4Ω  |  |  |  |

| C43 = C44  | 56pF  | 27pF              | 15pF   | 12pF   |  |  |  |

| E1 = E2    | 100nH | 51nH              | 27nH   | 18nH   |  |  |  |

| C41        | 47pF  | 12pF              | 12pF   | 10pF   |  |  |  |

| C10 = C40  | 13pF  | 12pF              | 3.3pF  | 2.7pF  |  |  |  |

| E5         | 100nH | 51nH              | 27nH   | 18nH   |  |  |  |

| R42 = R43  | 300Ω  | 300Ω              | 300Ω   | 300Ω   |  |  |  |

| R53        | 120Ω  | 120Ω              | 120Ω   | 120Ω   |  |  |  |

| C45 = C46  | 39pF  | 18pF              | 10pF   | 8.2pF  |  |  |  |

| E3 = E4    | 150nH | 75nH              | 39nH   | 27nH   |  |  |  |

Table 1. Bandpass Filter Component Values for Different Input Frequencies

#### **Output Common Mode Adjustment**

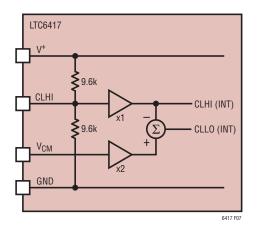

For AC-coupled applications, the output common mode voltage is set by the V<sub>CM</sub> pin. An internal buffer, as shown in Figure 6, couples the voltage on the  $V_{CM}$  pin to the inputs via high impedance resistors. Because the input common mode voltage is approximately the same as the output common mode voltage, both are approximately equal to the voltage applied to the V<sub>CM</sub> pin. For DC-coupled applications, the internal  $V_{CM}$  is overdriven by the input signal. The V<sub>CM</sub> pin has a Thevenin equivalent resistance of 2.7k and can be overdriven by an external voltage. The V<sub>CM</sub> pin floats to a default voltage of 1.25V on a 5V supply. The output common mode voltage is capable of tracking V<sub>CM</sub> in a range from 0.29V to 2.25V on a 5.0V supply. The V<sub>CM</sub> pin can be floated, but it should always be bypassed close to the LTC6417 with a 0.1µF bypass capacitor to GND. When interfacing with A/D converters such as the LTC22xx families, the  $V_{CM}$  pin can be connected to the  $V_{CM}$  output pin of the ADC, as shown in Figure 5.

#### Clamping, the CLHI Pin and the $V_{\mbox{CM}}$ Pin

The CLHI pin is used to set the high side clamp voltage of the high speed internal circuitry.

This limits the single-ended maximum and minimum voltage excursion at each of the outputs. This feature is extremely important in applications with input signals having very large peak-to-average ratios such as cellular base station receivers.

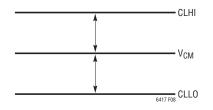

Internal circuitry generates a symmetric low side clamp voltage with respect to the common mode voltage  $V_{CM}$  (Figures 7 and 8). The LTC6417 clamp control circuitry features two additional mechanisms. First, internally imposed maximum swing of 2.5V and minimum swing of 0.2V ensure that the transistors do not go into deep saturation. This ensures a quick recovery after the clamps are released. Second, if CLHI voltage is less than  $V_{CM}$ , internal CLLO starts to track CLHI. This limits output swing and protects output transistors. Since the clamp response is on the order of 5ns to clamp and 1ns to release, clamp circuit becomes less effective at frequencies beyond 160MHz.

Figure 6. LTC6417 Internal Topology Showing the Common Mode Buffer Biasing the Inputs

Figure 7. Internal Circuitry Generating Symmetric Clamp Voltages with Respect to V<sub>CM</sub>

Figure 8. Symmetric High- and Low-Side Clamp Voltages with Respect to  $V_{\text{CM}}$

If a very large signal arrives at the LTC6417, the voltages applied to the CLHI and  $V_{CM}$  pins will determine the maximum and minimum output swing. Once the input signal returns to the normal operating range, the LTC6417 returns to linear operation within 2ns. For DC-coupled operation, the common mode of the input signals might be different than the voltage on the V<sub>CM</sub> pin. The minimum swing will still be set by the voltages applied to the V<sub>CM</sub> and CLHI pins.

CLHI is a high impedance input. It has an input impedance of 4.8k. On a 5V supply, CLHI self-biases to 2.5V. To limit the signal swing to a subsequent stage's power supply, e.g. an ADC such as the LTC2165, simply connect CLHI to the positive supply pin of the LTC2165. The CLHI pin should be bypassed with a  $0.1\mu$ F capacitor as close to the LTC6417 as possible.

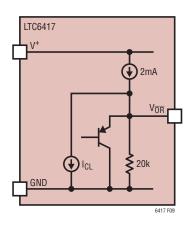

### The V<sub>OR</sub> Pin

The  $V_{\overline{OR}}$ , overrange pin signals an overrange condition when one or both inputs exceed the minimum or maximum signal swing limits set by the CLHI and  $V_{CM}$  pins.

The LTC6417  $V_{\overline{OR}}$  pin can be used by a control system to limit the input power dynamically. This is very useful in applications where the overload response of the complete system would be too slow.

Figure 9. LTC6417 Internal Topology Showing V<sub>OR</sub> Pin with Pull-Down Resistor and Clamp

The  $V_{\overline{OR}}$  pin, as shown in Figure 9, is internally connected to a current source sourcing 2mA, plus an internal 20k resistor pull-down to GND. An internal clamp limits the maximum output to 3.4V. As soon as one of the inputs goes beyond the limits, and therefore engages one of the clamps, the output current, hence, the  $V_{\overline{OR}}$  voltage goes to zero. The dynamic response of the  $V_{\overline{OR}}$  pin can be adjusted with an external resistor and an optional external capacitor. For a high speed operation, add a 50 $\Omega$  resistor from  $V_{\overline{OR}}$  to GND, resulting in a high speed signal with 100mV swing.

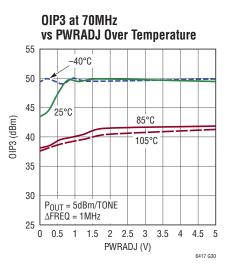

### The PWRADJ Pin

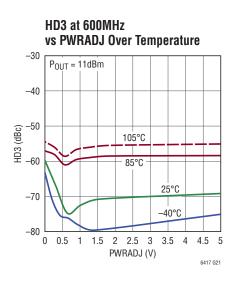

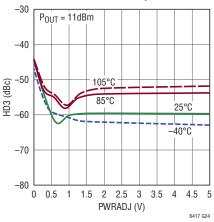

The voltage applied to the PWRADJ pin scales the supply current and performance of the LTC6417. This is useful for reducing power consumption in applications where linearity of the LTC6417 exceeds the linearity of the other components in the system; hence LTC6417's linearity can be derated without effecting system performance. PWRADJ is a high impedance input. It has an input impedance of 14.5k. On a 5V supply, PWRADJ self-biases to 1.6V. For full power, simply connect PWRADJ to the positive supply V<sup>+</sup>. For minimum power, short the PWRADJ pin to GND. The PWRADJ pin should be bypassed with a 0.1 $\mu$ F capacitor as close to the LTC6417 as possible. LTC6417 performance vs PWRADJ can be found in the graphs.

### The SHDN Pin

When pulled high, the SHDN pin puts the LTC6417 in sleep mode, significantly reducing supply current. SHDN is a high impedance input. It has an input impedance of  $10.5k\Omega$ . If the SHDN pin is not driven with an external voltage, it floats down to the same potential as GND, keeping the LTC6417 enabled. The SHDN pin should be bypassed with a 0.1µF capacitor as close to the LTC6417 as possible.

In sleep mode, the input and output stages are turned off, but the input and output clamps are kept alive to protect the part against overvoltage.

The supply current in sleep mode is only 24mA, instead of the typical 125mA. But should the clamps turn on, the current drawn from the supply can be as high as 180mA.

This can be avoided by following a few precautions when putting the LTC6417 in sleep mode:

- Do not force the outputs below the inputs, this will turn the output stages on.

- Either float CLHI or tie it to V<sub>CC</sub>. This will allow a wider signal range at the inputs before the clamps are activated.

- Maintain the inputs below CLHI or 2.5V whichever is lower, otherwise the input clamps will be activated.

- Do not short  $V_{CM}$  or the outputs to GND, in either case the output clamps will turn on. Current drawn from the supply can be as high as 180mA.

- Float the outputs if possible. The outputs will be pulled down by internal resistors to V<sub>CM</sub>.

Heeding these precautions will protect the LTC6417 as well any part it is driving, while maintaining a low current consumption in sleep mode.

#### Noise and Noise Figure

The LTC6417's differential input referred voltage and current noise densities are 1.5 nV/ $\sqrt{Hz}$  and 4.3 pA/ $\sqrt{Hz}$ , respectively.

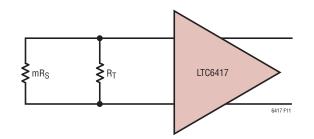

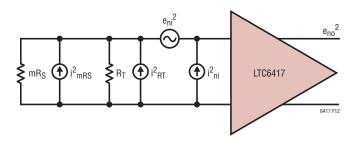

Before presenting a noise model, the circuit with the transformer in Figure 10 will be simplified. In Figure 11, the circuit is redrawn with the source impedance reflected to the secondary side of the transformer. The source impedance is multiplied by the impedance ratio m of the transformer. In Figure 12, noise sources associated with the amplifier and resistors have been added. Based on this noise model of the LTC6417, the total output noise power excluding the noise contribution of the source is:

$$e_{no}^{2} = e_{ni}^{2} + (i_{ni} \bullet R_{EQ})^{2} + i_{R_{T}}^{2} \bullet R_{EQ}^{2}$$

$$= e_{ni}^{2} + (i_{ni} \bullet R_{EQ})^{2} + \frac{4kT}{R_{T}} \bullet R_{EQ}^{2}$$

where  $R_{EQ} = mR_S ||R_T$  is the equivalent impedance seen at the input of the LTC6417. The output noise power due to the noise of source resistance is given by:

$$e_{no(mR_S)}^{2} = i_{mR_S}^{2} \bullet R_{EQ}^{2}$$

$$= \frac{4kT}{mR_S} \bullet R_{EQ}^{2}$$

Noise figure (NF) is calculated from the ratio of these noise powers:

$$NF = 10 \log \left( 1 + \frac{e_{no}^2}{e_{no(mR_S)}^2} \right)$$

Figure 10. LTC6417 with a Transformer

Figure 11. Source Resistance Referred to the Secondary

Figure 12. LTC6417 Simplified Noise Model

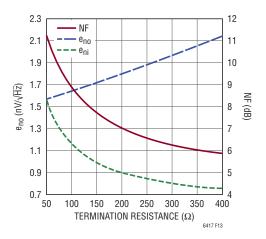

In most cases the termination resistor will be matched to the source resistance, e.g.  $R_T = mR_S$ . For the LTC6417 with a wide-band terminated transformer, a plot of output and input noise density and NF versus termination resistor is shown in Figure 13. To get the best noise performance in the system, use the LTC6417 matched to a transformer with high impedance ratio. Although the output noise density will be higher, noise figure will improve because of the additional gain realized in the transformer. An impedance ratio greater than 8 is not recommended, as the increased termination resistance with the LTC6417 input capacitance will limit signal bandwidth. Consult Table 2 for a quick estimate of the LTC6417's output noise density and NF for different transformer impedance ratios. Measured NF numbers will be higher as the simple noise model does not take the insertion loss in the transformer into account.

Table 2. Output Noise Density and NF of the LTC4617 with a Wide-Band Terminated Transformer,  $R_S$  =  $50\Omega$

| , <b>o</b>                          |                                               |               |                                                     |            |  |  |

|-------------------------------------|-----------------------------------------------|---------------|-----------------------------------------------------|------------|--|--|

| TRANSFORMER<br>IMPEDANCE<br>RATIO m | TERMINATION<br>RESISTOR R <sub>T</sub><br>(Ω) | GAIN<br>(V/V) | OUTPUT NOISE<br>DENSITY e <sub>no</sub><br>(nV/√Hz) | NF<br>(dB) |  |  |

| 1                                   | 50                                            | 1.0           | 1.57                                                | 11.2       |  |  |

| 2                                   | 100                                           | 1.4           | 1.64                                                | 8.9        |  |  |

| 4                                   | 200                                           | 2.0           | 1.80                                                | 7.0        |  |  |

| 8                                   | 400                                           | 2.8           | 2.14                                                | 5.9        |  |  |

Figure 13. LTC4617 Output and Input Noise Density and NF vs Termination Resistance

### Interfacing the LTC6417 to A/D Converters

The LTC6417 has been specially designed to interface directly with high speed A/D converters. It is possible to drive the ADC directly from the LTC6417. In practice, however, better performance may be obtained by adding a few external components at the output of the LTC6417. Figure 5 shows the LTC6417 driving an LTC2209 16-bit ADC. The differential outputs of the LTC6417 are bandpass filtered, then drive the differential inputs of the LTC2209. In many applications, a filter like this is desirable to limit the wideband noise of the amplifier. This is especially true in high performance 16-bit designs. The minimum recommended network between the LTC6417 and the ADC is simply two  $10\Omega$  series resistors, which are used to help eliminate resonances associated with the stray capacitance of PCB traces and the stray inductance of the internal bond wires at the ADC input pins and the driver output pins.

#### **Single-Ended Signals**

The LTC6417 has not been designed to convert singleended signals to differential signals. A single-ended input signal can be converted to a differential signal via a balun connected to the inputs of the LTC6417. Figure 5 shows the LTC6417 driven by a 1:4 transformer which provides 6dB of voltage gain while also performing a single-ended to differential conversion.

### **Power Supply Considerations**

For best linearity, the LTC6417 should have a positive supply of V<sup>+</sup> = 5V. For ESD protection, the LTC6417 has an internal edge-triggered supply voltage clamp. The timing mechanism of the clamp enables the LTC6417's protection circuit during ESD events. This internal clamp can also be activated by voltage overshoot and rapid slew rate on the positive supply V<sup>+</sup> pin. The LTC6417 should not be hot-plugged into a powered socket because there is a risk of activating this internal ESD clamp circuit. Bypass capacitors of 680pF and 0.1µF should be connected to the V<sup>+</sup> pin, as close as possible to the LTC6417.

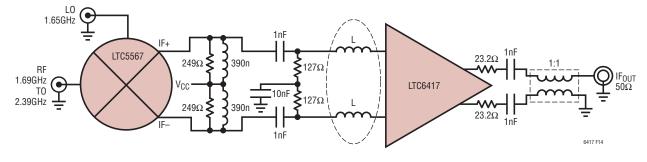

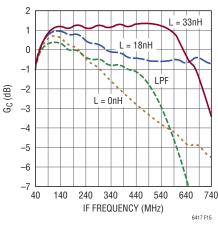

# Interfacing the LTC6417 with Active Mixers for Ultrawide IF Bandwidth

The LTC6417 is an excellent interface amplifier for use with active downconverting mixers like the LTC5567. By using 6417f

the LTC6417 as a post-amplifier for the LTC5567, it is possible to achieve IF bandwidths in excess of 500MHz, while adding bandpass filtering. A key to achieving this extremely wide IF bandwidth is the use of pre-emphasis inductors in series with the LTC6417 inputs to compensate for the inherent rolloff caused by the LTC6417 input capacitance interacting with the interface impedance. In the example seen in Figure 14, a value of 33nH for each pre-emphasis inductor gives excellent wideband performance. Figure 15 shows performance for various values of L. For L = 33nH, overall conversion gain remains within 1dB from 90MHz to 590MHz, resulting in 500MHz of IF bandwidth.

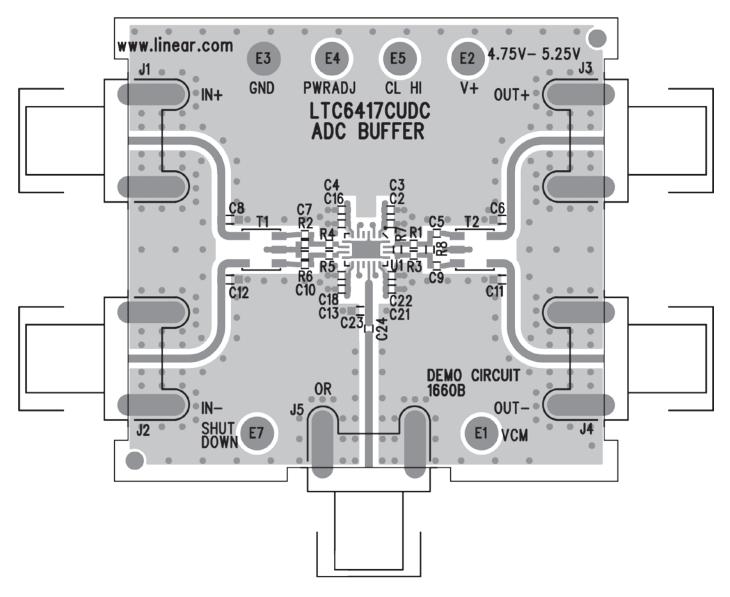

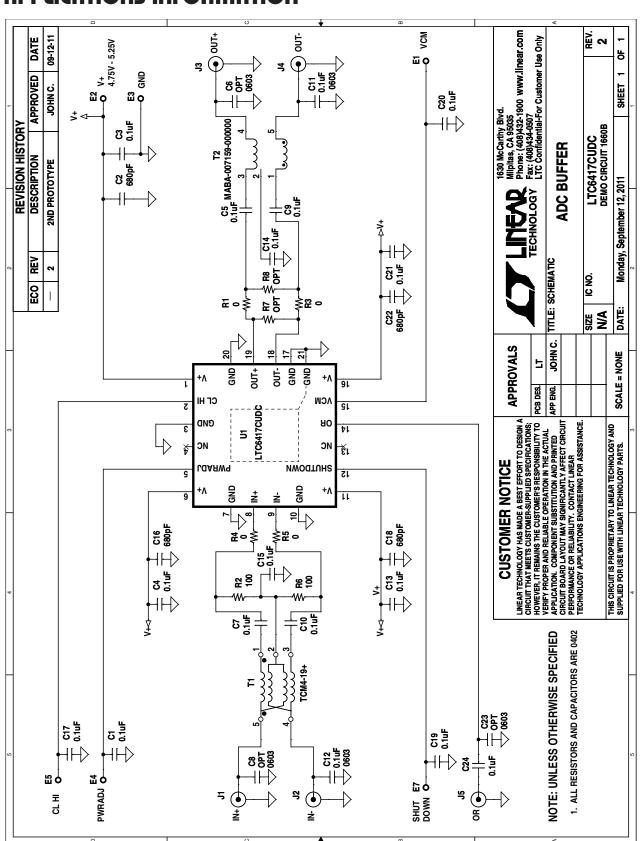

#### **Test Circuits**

Due to the fully differential design of the LTC6417 and its usefulness in applications both with and without ADCs, two test circuits have been used to generate the information in this data sheet. Test circuit A is DC1660B, a two-port

demonstration circuit for the LTC6417. The board layout and the schematic are shown in Figures 16 and 17. These circuits include a 1:4 input balun and a 1:1 output balun for single-ended-to-differential conversion, allowing direct analysis using a 2-port network analyzer. Including the input and output baluns, the –3dB bandwidth is approximately 600MHz. A 1:4 input balun before the LTC6417 inputs provides 6dB of voltage gain, but results in better noise figure performance compared to a 1:1 input balun. Noise figure measurements for both input baluns can be found in the graphs.

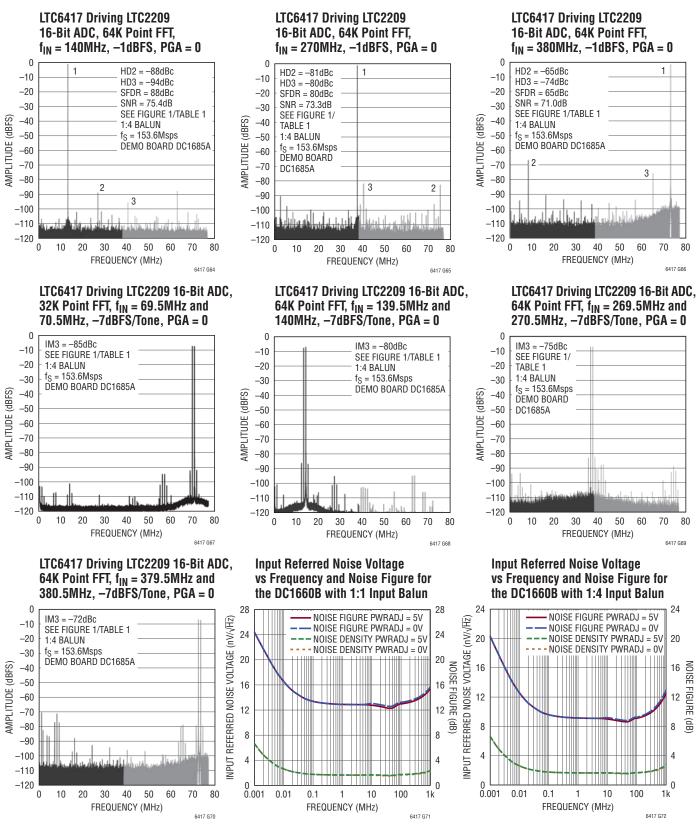

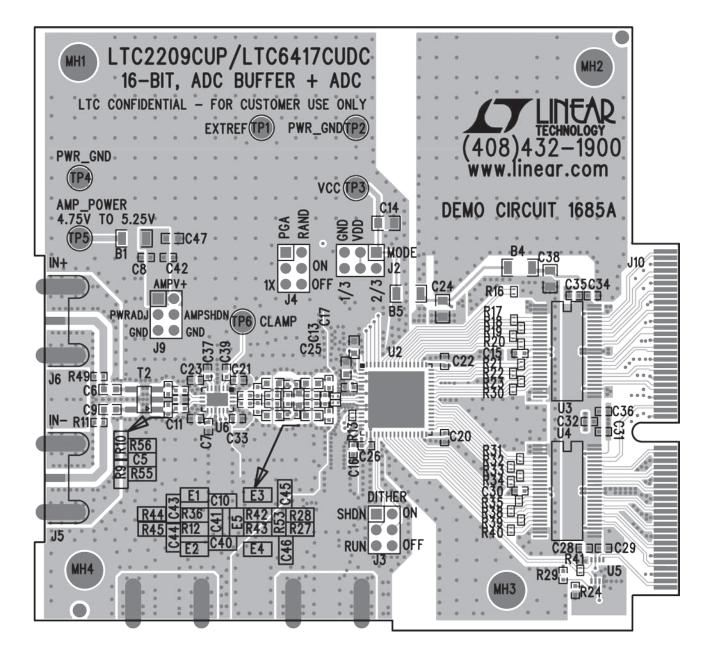

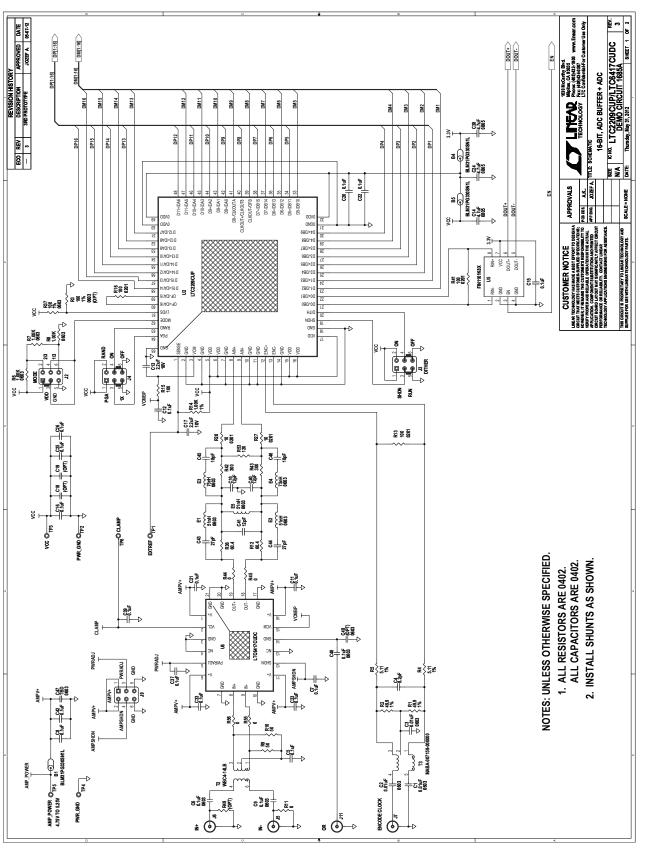

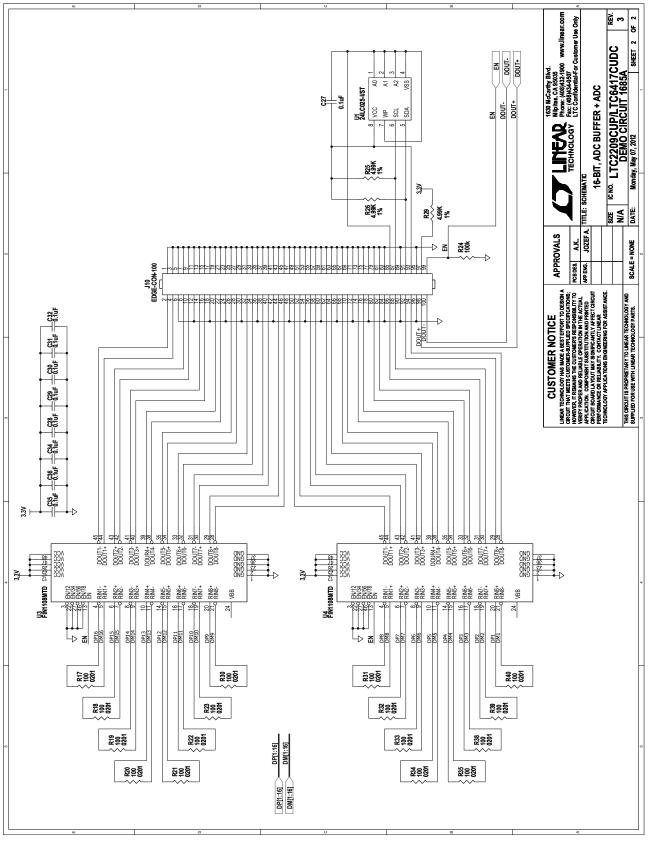

Test circuit B is DC1685A. It consists of an LTC6417 driving an LTC2209 16-bit 153.6Msps ADC. It is intended for use in conjunction with DC890B (computer interface board) and proprietary Linear Technology evaluation software to evaluate the performance of both parts together. Both the DC1685A board layout and the schematic can be seen Figures 18 and 19.

Figure 14

Figure 16. Demo Board DC1660B Layout

Figure 18. Demo Board DC1685A Layout

6417f

Figure 19. Demo Board DC1685A Schematic (Test Circuit B)

# APPLICATIONS INFORMATION

6417f

6417f

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

**UDC** Package

### TYPICAL APPLICATION

DC1685A Simplified Schematic with Suggested Output Termination for Driving an LTC2209 16-Bit ADC at 140MHz

### **RELATED PARTS**

| PART NUMBER                                    | DESCRIPTION                                                                    | COMMENTS                                                                                                                                    |

|------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed Gain IF Amplifiers/                      | ADC Drivers                                                                    |                                                                                                                                             |

| LTC6400-8/LTC6400-14/<br>LTC6400-20/LTC6400-26 | 1.8GHz Low Noise, Low Distortion Differential ADC Drivers                      | -71dBc IM3 at 240MHz 2V <sub>P-P</sub> Composite, $I_S$ = 90mA, $A_V$ = 8dB, 14dB, 20dB, 26dB                                               |

| LTC6420-20                                     | Dual 1.8GHz Low Noise, Low Distortion Differential ADC Drivers                 | Dual Version of the LTC6400-20, $A_V = 8$ dB, 14dB, 20dB, 26dB                                                                              |

| LTC6401-8/LTC6401-14/<br>LTC6401-20/LTC6401-26 | 1.3GHz Low Noise, Low Distortion Differential ADC Drivers                      | -74dBc IM3 at 140MHz $2V_{P-P}$ Composite, I <sub>S</sub> = 50mA, A <sub>V</sub> = 8dB, 14dB, 20dB, 26dB                                    |

| LTC6421-20                                     | Dual 1.3GHz Low Noise, Low Distortion Differential ADC Drivers                 | Dual Version of the LTC6401-20, A <sub>V</sub> = 8dB, 14dB, 20dB, 26dB                                                                      |

| IF Amplifiers/ADC Drivers                      | with Variable Gain                                                             |                                                                                                                                             |

| LTC6412                                        | 800MHz, 31dB Range Analog-Controlled VGA                                       | Continuously Adjustable Gain Control, –14dB to 17dB Linear-in-dB<br>Gain Range                                                              |

| LT5554                                         | High Dynamic Range 7-Bit Digitally Controlled IF<br>VGA/ADC Driver             | OIP3 = 46dBm at 200MHz, Gain Range 1.725 to 17.6dB 0.125dB Steps                                                                            |

| LT5514                                         | Ultra-Low Distortion IF Amplifier/ADC Driver with<br>Digitally Controlled Gain | OIP3 = 47dBm at 100MHz, Gain Range 10.5dB to 33dB 1.5dB Steps                                                                               |

| LT5524                                         | Low Distortion IF Amplifier/ADC Driver with<br>Digitally Controlled Gain       | OIP3 = 40dBm at 100MHz, Gain Range 4.5dB to 37dB 1.5dB Steps                                                                                |

| Baseband Differential Am                       | plifiers                                                                       |                                                                                                                                             |

| LT6416                                         | 2GHz Low Noise Differential 16-Bit ADC Buffer                                  | -84dBc IM3 at 160MHz $2V_{P-P}$ Composite, $A_V = 1$ , $e_n = 1.8nV/\sqrt{Hz}$ , 42mA                                                       |

| LTC6409                                        | 10GHz 1.1nV√Hz ADC Driver                                                      | AC- or DC-Coupled 0MHz to 100MHz                                                                                                            |

| LTC6406                                        | 3GHz Rail-to-Rail Input Differential Amplifier/<br>ADC Driver                  | -65dBc IM3 at 50MHz $2V_{P-P}$ Composite, Rail-to-Rail Inputs, $e_n = 1.6nV/\sqrt{Hz}$ , 18mA                                               |